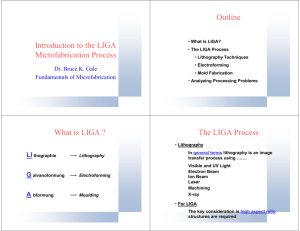

Chapter 4. Nanostructures Technology, Research, ... Applications

advertisement