Michael S. Georgas Interconnects

advertisement

An Optical Data Receiver for Integrated Photonic

Interconnects

by

Michael S. Georgas

Submitted to the Department of Electrical Engineering and Computer

Science

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2009

@ Massachusetts Institute of Technology 2009. All rights reserved.

,./1 I

A uthor .......... ...

Department of Eectrical Engineering and Computer Science

September 4, 2009

Certified by .....

Accepted by...

/

-/

Vladimir Stojanovid

Assistant Professor

Thesis Supervisor

7................................................................

Terry Orlando

Chairman, Department Committee on Graduate Theses

MASSCHUSRTTS INS

OF TECHNOLOGY

SEP 3 0 2009

LIBRARIES

ARCHIVES

An Optical Data Receiver for Integrated Photonic

Interconnects

by

Michael S. Georgas

Submitted to the Department of Electrical Engineering and Computer Science

on September 4, 2009, in partial fulfillment of the

requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

Abstract

The throughput bounds of traditional interconnect networks in microprocessors

are being pushed to their limits. In past single-core processors, the number of long

global wires constituted only a small fraction of the total. However, with the emergence of multi-core systems, where each core must be able to communicate with each

other as well as off-chip memory, global interconnects have become a major bottleneck. The solution has been proposed through integrated photonic networks, where

multiple channels of information can be placed onto a single low-latency waveguide,

reducing the number of interconnects and increasing the speed of transimssion.

This work presents a novel optical data receiver for integrated optical links. Both

the optical receiver and the photodiode are monolithically-integrated in the same

CMOS substrate. The highly-digital receiver senses the photodiode current using

a regenerative cross-coupled latch. The photodiode is modelled as an ideal current

source with a capacitance in parallel. The receiver operates in two phases, receiving

one bit per clock cycle, and is able to resolve input photocurrents of less than 50,PA

at 5-Gb/s with a power consumption of less than 500yW (100fJ/bit). The receiver

was fabricated in a 32-nm CMOS process as part of a flexible test vehicle that will

demonstrate various optical components and the electronic systems that interface

with them.

Thesis Supervisor: Vladimir Stojanovid

Title: Assistant Professor

Acknowledgments

Over the past two years I have learned a tremendous amount. I am grateful to

everyone that I have learned something from. In particular I thank my supervisor,

Professor Vladimir Stojanovid, for all of his support and guidance in this work. I

thank my closest collaborators, Ben Moss and Jonathan Leu, and I thank the rest of

the Integrated Photonics team.

I am also grateful to have enjoyed a mid-afternoon coffee with some of the most

interesting people that I have met. I thank Ranko Sredojevid for all of the discussion

(ranging from politics to parallel computing) and the rest of my research group here

at MIT. I thank all of the other new friends that I have made.

I thank my family, and for more than the last two years. You have always been a

great support for me. I thank Diana for always believing in me, even when I do not

believe in myself. I could not have made it this far without all of you.

Support

My work over the past two years has been funded by NSERC, DARPA, and Texas

Instruments. I thank each group for helping to fund my exploration of this interesting

research.

Contents

1

2

15

Introduction

1.1

Background ...................

1.2

Motivation ...............

1.3

Previous Work

. .. .

........

..

16

................

1.3.1

Optical Waveguides ...................

1.3.2

Optical Modulators ................

1.3.3

Optical Receivers ...................

1.4

Contributions of this Thesis ...................

1.5

Summary

17

..

.........

...................

15

18

.....

. .

.....

19

......

24

....

. . .

. ......................

18

25

.

27

Receiver Design

2.1

Recever Block Diagram ...................

2.2

Photodiode

..........

...................

2.2.1

Semiconductor Material

2.2.2

Geometry ...................

2.2.3

Photodiode Model

...................

28

..

29

30

2.4

Offset Compensation .......

2.5

Latch Output Buffer ...............

2.6

Dynamic to Static Converter ...................

2.7

Photodiode Clamp ...................

2.8

Clock Enable

2.9

Summary

32

.....

...................

Latching Sense Amplifier ................

. ..................

..

.........

2.3

...................

27

.......

.......

..

................

.....

..

33

.

35

..

..

38

....

.

.......

.........

.........

38

..

...

39

40

40

i

~-

~--.(~I.--~-.-.~II

-i--^-li. i-iii-l;il-"-;-"i--.i'.--~''~

3 Receiver Simulation

4

3.1

Transient Simulation .......

3.2

Offset Compensation Simulation .........

3.3

Setup Time .........................

...........

. . . .

.

43

. . .

.

46

. . . .. .

46

3.4

Characterization of the Receiver's Sampling Aperture . . . . . . . . .

49

3.5

Eye Diagram

3.6

Process Variation .

3.7

Summary

.

....

..

.

.................

. . . . .

.

51

..............

. . . . .

.

53

. . . . . .. .

55

.....

......................

EOS2 Test Chip

57

4.1

Chip Organization

4.2

Digital Test Structures .......

4.3

5

43

.

............

. . . .

.

57

. .

. . . .

.

61

.....

. . .. .

.

61

.

63

.

64

.. . . . .

65

4.2.1

Scan Chain .......

4.2.2

High-Speed Signal Synchronization

4.2.3

PRBS/Pattern Generator

4.2.4

Counters .........

4.2.5

Snapshot. ..............

Summary

. .

. . . . . . . . . . . .

. . . . .

. .

. . . . .

...

.................

. . . .

.

66

. . . .

.

67

Conclusion and Future Work

5.1

Conclusion . . ..................

5.2

Future Work .........

69

.............

.

.

.................... .

5.2.1

Co-design of Optical Devices and Electrical Circuits ....

5.2.2

Optical Device Design, Layout, and Verification . .......

69

...

70

. ..

70

70

A Testbench Schematics

73

B Power Measurement in Simulation

77

C Sampling Aperture Data

79

D Custom Standard Cell Library

81

D.1 Register

.......

...

...........................

.

81

D.2 MUX .

82

...................................

85

E Scan Chain Control

E.1

85

Correct Signalling for the Scan Chain ...................

E.1.1

Reading from EOS2

. ..................

E.1.2 Writing from EOS2 . .................

F PRBS Generation

.

.

. . .

.

86

86

89

List of Figures

17

. .........

1-1

An integrated photonic link implementing WDM [1].

1-2

A ring with a modulator on the EOS2 test chip .............

19

1-3

Optical data receivers from the literature.

. ...............

21

2-1

Block diagram of the optical data receiver implemented in the EOS2

...

test chip ...................

...........

..

27

. .

29

2-2

The absorption coeffecient plotted against wavelenth of light [15].

2-3

A cross-sectional view of the waveguide showing the mode propagation.

[Figure courtesy of Jason Orcutt]

.

...................

31

32

2-4

A 3D model of one of the photodiodes implemented in EOS2 ....

2-5

Photodiode Model

.

32

2-6

The latching data receiver implemented on the EOS2 test chip..... .

34

2-7

7-bit offset compensation scheme for latching data receiver........

35

2-8

Offset compensation performance......

2-9

The output buffer of the optical receiver. . ......

.......

...................

.

.

...........

2-10 Dynamic-to-static schematic. ...................

38

..

.......

36

39

....

2-11 The photodiode-clamping circuit used in the optical data receiver. ..

39

2-12 The clock-enabling block for each optical data receiver. . ........

40

44

3-1

Transient simulation waveforms demonstrating bit decisions. .....

3-2

Propagation delay through the latch plotted against setup time. The

input photocurrent was varied, and the input data is switched from 0

..

to 1. Clock frequency is 5-GHz. ...................

3-3

Sampling apertuture characterization for 0-1 step input.

. .......

48

50

i

3-4

In Situ eye diagram from simulation.

3-5

Transient plot of the positive output terminal of the receiver during a

...................

DC input photocurrent. Superimposed on the plot is the distribution

of threshold values from monte carlo simulation.

4-1 Layout photo of the EOS2 chip .

. . . . .

. .

. . . .

. . . . . .

4-2

Organization of the EOS2 electrical cell.

4-3

An optical link in EOS2 .

4-4

Block diagram showing cell operation. .

. . . . .

4-5

Block diagram of scan chain cells.....

. . .

4-6

High-speed SEnable synchronization.

. . . .

4-7

High-speed signal synchronization .

4-8

PRBS/pattern generator block .

4-9

Output transition counter with reference.

. . . . . .

.........

. . .

. . . .

.

58

. . . . . .

58

. . . . .

..

.

59

. . . . . .

60

. . . . . .

.

62

. . . . .

.

63

. . . . . . .

.

64

.

65

. . . . . .

66

.. .

. . . .

. . . . . . .

4-10 Snapshot implemented for the modulator and data receiver of EOS2.

A-1 Transient analysis testbench . . . . . . . ....

54

.

.

67

. . . . .

.

73

. . .

.

74

A-3 Testbench for setup and hold time simulation. . . . . . . . . . . . . .

74

A-4 Sampling aperture characterization testbench. . . . . . . . . . . . . .

75

A-5 Variation analysis testbench. ...........

.

75

A-2 Offset compensation testbench. .........

.

. . . . . .

B-I

Testbench for power measurement simulation .

. . . . .

. . . . . . .

77

C-I

Sampling apertuture characterization for 1-0 step input.

. . . . . . .

80

D-I Register design. .................

D-2 M UX design .

..

..

. . . . . . . . . . ....

. . . . . . . . . . . . . . . . . . . . . . . . . . .

E-i Block diagram of scan chain cells. ...................

F-I The output of the PRBS generator, driven at 5-GHz ..........

.

List of Tables

1.1

Summary of optical receivers scaled to 32nm. Power scaling for digital

designs follows P = fCVDD, with C scaling linearly with process.

Power scaling for analog designs follows a linear scaling with current

and supply, based on maintaining a constant transistor transconductance. 20

2.1

Example configuration data. Threshold values are found using Figure 2-7 ......

3.1

37

............................

Power consumption for each block of the data receiver during 5-GHz

45

operation with a 100-uA 'on' photocurrent. . ...............

F.1 Progression of PRBS pattern. . ..................

.

90

Chapter 1

Introduction

This thesis presents an energy-efficient monolithically-integrated optical receiver

for photonic interconnects in a 32-nm CMOS process. The work will analyze the

various aspects of the receiver, focusing on challenges such as process variation, sensitivity, energy-efficiency, and integrated photodiode modelling.

1.1

Background

Optics has been used to transmit high-bandwidth data since the 1970s, when it

was first used in long-haul interconnects. In computing, optical networks have been

envisioned as a replacement for electrical backbones since the early 1990s [2] when

they were used to connect multiple computers to form a single super-computer. Since

that time, Moore's law continued to drive CMOS gate sizes smaller and smaller,

increasing clock speeds. The price, however, was paid in power dissipation. Processor

manufacturers such as Intel and AMD drove clock speeds to the point where the heat

produced could not be pulled away fast enough, and so a practical limit in CPU clock

speed was reached in the range of 3- to 4-GHz. Designers had to find a way to keep

computation scaling, and the answer was found in parallelism.

Since the release of the first multi-core processors, the trend in industry and

academia has been to continue to increase the number of cores on each chip. At the

time of this proposal, it is common for consumer computers to have dual- or quad-

i-1

core processors, such as the Intel Core i7 [3]. More specialized consumer hardware

has seen 9-core processors, such as the IBM Cell in the Playstation 3 [4], and 16-core

server processors, such as the third-generation SPARC processor [5]. Going forward,

we can envision systems with upwards of 256 cores.

In order to fully harness the computing capability of many-core systems, communication between cores and with a shared off-chip memory must be extremely fast. In

past single-core processors, the number of long global wires constituted only a small

fraction of the total. However, with the emergence of multi-core systems, where each

core must be able to communicate with each other as well as off-chip memory, global

interconnects have become a major bottleneck. Power density requirements further

dictate that the communication must also be low power and energy-efficient. The

problem with electrical I/O is that even its projected performance will not satisfy

the bandwidth and energy-efficiency demands of many-core systems [1]. This is due

in part to the fact that electrical I/O performance is ceasing to scale with technology, and is instead becoming channel-limited [6]. Integrated photonic links provide a

new type of channel for inter- and intra-chip I/O. Wavelength-division multiplexing

(WDM) allows for several high-speed data streams to be placed onto a single lowlatency waveguide, reducing the number of interconnects and increasing the energy

efficiency and bandwidth density.

1.2

Motivation

The reward of a monolithically-integrated optical link is high, but there are many

challenges that stand in its way. The characteristics of such a link are well-suited to

high-speed communication, but have significanly different characteristics than traditional electrical interconnect. As a result, it may be difficult for designers to adapt

to optical I/O design. Designers must be knowledgeable in optical device physics in

order to determine which of the limited materials and layers to use in a given semiconductor process. They must be able to take these materials and create optical device

geometries that either route optical data or serve as an interface between the optical

LM

and electrical domains. Finally, they must have a strong system-design background in

order to optimize the electrical-optical-electrial link as a whole. This thesis addresses

this emerging design issue through the implementation of an optical data receiver.

Each of the parts of the receiver will be described and analyzed, exemplifying how

designers must use their knowledge of both optics and electronics in order to exploit

optical I/O. This serves to help future designers by focusing on the most important

design parameters.

Previous Work

1.3

Chip A

Vertical Coupler

V

and Tap

External

Lser

Soure

Ring Modulator

with A Resonance

Chip B

Photodetector.

Ring Modulator Driver

V

Waveguide

Ring Modulator

with 2 Resomnance

Mode

Fiber

Receiver

,

O\

Ring Filter

with Xl Resonance

Ring Filter

2 Resonance

with

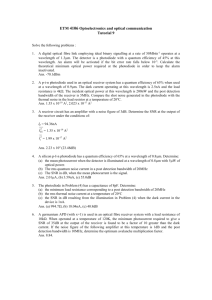

Figure 1-1: An integrated photonic link implementing WDM [1].

This section reviews the building blocks and previous work done on integrated

optical interconnects. A diagram of an integrated optoelectronic system is shown in

Figure 1-1, with the main building blocks being:

1. integrated photonic waveguide - the path along which the modulated optical

data can travel

2. optical modulator - converts electronic data into an optical signal

3. optical receiver - converts optically modulated data back into the electrical

domain

In Figure 1-1, the optical source is an off-chip continuous-wave laser. This laser

light is coupled onto the IC by means of a vertical coupler which redirects the light to

travel in the plane of the chip. Once propagating along the integrated photonic waveguides, the continuous-wave laser light can be manipulated. Different wavelengths can

be re-routed by means of wavelength-selective filters, and data can be imprinted onto

each wavelength by means of an optical modulator. The modulated light can be

placed onto a bus common with data modulated on different wavelengths, without

interference. This optically modulated data can then be routed to an optical receiver,

either on the same chip or a different one.

While these components have been demonstrated in the past, one of the key

challenges in this work is that the components must be monolithically integrated

onto a single wafer of silicon, in order to enable high energy efficiency and bandwidth

density. In the following sections, we outline each of the above components in more

depth.

1.3.1

Optical Waveguides

Optical confinement in any medium is created by an index difference between the

core and surrounding materials. Integrated photonic waveguides have been demonstrated recently in two main ways: in special processes, such as silicon-on-insulator

(SOI); and in bulk CMOS processes [7]. In an SOI process, the waveguide core can

be created using the body, with the buried-oxide layer creating the cladding. In

bulk CMOS, the waveguide core can be made from the poly-silicon layer used to

create the unsilicided resistors, located above the shallow-trench isolation (STI). One

of the main problems with bulk CMOS integration is that the oxide layer is much

thinner, increasing optical loss to the substrate. In order to mitigate this effect, an

air-undercladding is created during post-processing, as demonstrated in [8].

1.3.2

Optical Modulators

The purpose of the optical modulator is to take an electrical signal, and imprint

it onto a continuous wave of light, generating an optically modulated signal. In this

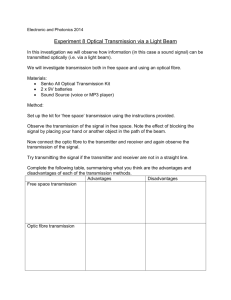

work, resonant ring modulators are used. Resonant ring filters (Figure 1-2) are circular optical structures adjacent to a waveguide. Each filter is tuned to a particular

photon wavelength. At that wavelength, light travelling down the waveguide will cou-

-

ple into the filter and remain confined there, eventually being dissipated or dropped.

All other wavelengths will travel down the waveguide undisturbed, except for some

relatively small wavelength-dependent loss.

Figure 1-2: A ring with a modulator on the EOS2 test chip.

A modulator based on this structure exploits the fact that the resonant frequency

can be tuned thermally, or by injecting charge into the ring to change the index of

refraction. To generate an optical '0', the ring is tuned to the wavelength of interest

and the transmission through the waveguide is decreased. To generate an optical '1',

the ring is tuned away from the wavelength of interest, decreasing that wavelength's

confinement and increasing its transmission [9].

1.3.3

Optical Receivers

The final component in the optical link is the receiver, which converts the opticallymodulated data back into the electrical domain. This is accomplished by sensing the

photocurrent produced by a photodiode that is being illuminated, and converting the

current into a voltage waveform. Previous implementations can be broken down into

two main types of implementations: current-sensing and current-integrating.

The

two methods are discussed further in the following subsections.

To date, the majority of optical receiver designs in the literature have addressed

telecommunications applications, where a single, discrete receiver is connected to a

fiber-optic cable and used to generate an electrical data signal. One major challenge

associated with this is the very large parasitic capacitance due to packaging of discrete

components. However, a major benefit is that since the phodiode is external, any

semiconductor material desired can be used. In contrast, in order to achieve a large

receiver density with high energy efficiency, we focus on monolithic integration. As a

M

result, in this work we are constrained to the material selection available in the 32-nm

bulk CMOS process.

The performance of several recent optical receivers is summarized in Table 1.1.

The table shows the process, data rate, power consumption, and topology used. Also

shown are power and energy/bit numbers scaled to a 32-nm process node. This was

done in order to create a more accurate performance comparison with the receiver

proposed in this work.

Process

[6]

[10]

[11]

[12]

This Work

90-nm

0.13-um SOI

80-nm

0.13-um,Ge-on-SOI

32-nm, SiGe PD

Speed

(Gb/s)

16

4x10

20-GHz

10

5

Power

(mW)

23

120

2.2

30

0.5

Power (mW)

(scaled)

8.17

19.7

0.88

4.92

0.5

pJ/bit

(scaled)

0.51

0.492

0.492

<0.1

Topology

DDR Latch

TIA/Limit

TIA

TIA/Limit

Latch

Table 1.1: Summary of optical receivers scaled to 32nm. Power scaling for digital

designs follows P = fCVD, with C scaling linearly with process. Power scaling for

analog designs follows a linear scaling with current and supply, based on maintaining

a constant transistor transconductance.

The integration of all necessary optical and electrical components onto a single

substrate was recently demonstrated in [10], where a single SOI substrate was used to

create a 4xl0-Gb/s transceiver, with the photodiodes flip-chip bonded to the CMOS

die.

The receiver consists of a TIA followed by a limiting amplifier.

impedance of the TIA is kept small by using resistive feedback.

The input

This allowed for

high-speed operation, despite the relatively large parasitic capacitance.

Current-Sensing Receivers

In current-sensing implementations, the input photocurrent is converted to a voltage waveform by means of some transimpedance gain. This can be accomplished by a

transimpedance amplifier, or as is the case in this work, a current-sense-amplifier. As

will be shown in Chapter 2, one advantage of this approach is that it easily enables

the implementation of a highly-digital design, with no biasing required at the input

(b) [12]

(a) [11]

TIAF nt.En ..

Vdd

,

P"U

(c) Narasimha Data Recever [10]

LGnd

(d) Receiver-less Optical Clock Injection [13]

ceiver presented in [11]. This work targeted low-power, high-bandwidth

optical Daylinks

T

T.

----------------

VWeora~~

--------------,-------------------

Figure 1-3: Optical data receivers from the literature.

nodes. The disadvantage however is that only the input photocurrent at the time of

evaluation is used, increasing the vulnerability due to random noise.

Figure 1-3a shows the CMOS trans-impedance amplifer for the

Clock

optical

Injecdata receiver presented in [11]. This work targeted low-power, high-bandwidth optical links

for short-distance fiber-optic interconnects. Standard TIA topologies were investigated, and limitations in the 80-nm CMOS process used were discussed. The TIA

shown in Figure 1-3a consists of a modified conventional regulated cascode, and overcomes process limitations such as low supply headroom in order to achieve its target

specification. The design also uses peaking inductors in order to increase the bandwidth, which further illustrates the problem with analog-style optical receiver designs

going forward into more advanced CMOS processes. The photodiode capacitance for

the work was 220-fF.

In [12], the advantages of monolithic integration of the photodiode and receiver

circuit are discussed, with the benefits of the use of Germanium presented. The work

uses a Ge-on-SOI detector, which is stated to have a responsivity of 0.35 A/W and

an intrinsic capacitance of 30-fF. The TIA ( 1-3b) used is a differential, common-gate

topology, that also uses peaking inductors. The TIA is followed by a 5-stage limiting

amplifier, and then a buffer to drive a 50-Q load. The complete receiver operates at

12-Gb/s, and the authors note the low photodiode biases used.

Data-rate scaling through the implementation of wavelength-division multiplexing

(WDM) is presented in [10]. The strategy of the transceiver presented was to take

multiple 10-Gb/s links and put them in parallel in order to achieve higher data rates.

This was done to address the fact that the channel can become the most expensive

part of a long I/O link. The data receiver used is shown in Figure 1-3c. Similar to

the receiver presented in [12], it consists of a TIA front-end followed by a 5-stage

limiting amplifier and 50-Q output buffer. The photodiode is flip-chip bonded to the

die, with light directed to it by means of a holographic lens. What is remarkable

about this work is the level of optelectronic integration, with the optical transmitters

and receivers implemented on the same CMOS SOI chip.

Current-Integrating Receivers

Designs that use an analog amplifying front-end burn a lot of quiescent power in

order to achieve high bandwidth and low noise [14]. In current-integrating approaches,

the input photocurrent is integrated into a capacitance, which converts the signal

into a voltage waveform that is integrated over time. The capacitance can be some

fixed capacitance, the capacitance of the diode, or the parasitic capacitance of the

interfacing transistors. It can also be the capacitance of a programmable current

source

[6] that continuously discharges the average photo-current. The advantage

of the current-integrating approach is that the input current signal is now being

integrated over as much as an entire bit time, increasing the sensitivity of the receiver.

The receiver will also be more robust to a random noise source at the input, as each

noise contribution should, on average, cancel over the integrating time.

The clearest example of an integrating-type receiver is presented in [13], and is

shown in Figure 1-3d. In this receiver-less design, two optical clock pulses that are

out of phase are propagated to two photodiodes that are stacked on top of each other.

As the optical clock pulses reach their target photodiodes, the photocurrent that is

generated is used to charge/discharge the node looking into the digital logic block.

The capacitance at this node is composed of the diode's own capacitances, as well

as any parasitic capacitances. Assuming that the diodes are well matched, and that

there is enough optical power and high-enough conversion efficiency, the input node

to the digital logic will have enough range to drive the following logic blocks.

Figure 1-3e shows the optical data receiver presented in [14]. One of the main

challenges with using clock-based designs that latch the decisions of comparators

is that there must be some reset phase in the operation.

Since we only want to

use one photodiode and one waveguide to save area, this means that it is difficult

to achieve better than one bit per clock period. An innovative solution to this is

presented in [14], where double-data-rate (DDR) operation was achieved. The author

integrates the photocurrent from the diode onto its own parasitic capacitance. A

feedback loop substracts an average optical current from the capacitor in order to

prevent the capacitor's voltage from increasing to the supply. The bit decision is

then made by comparing the voltage on the capacitor to the voltage on the capacitor

from the previous bit. If the voltage is greater, then photocurrent has been generated

during this bit decision and an optical '1' is received. If the voltage is smaller (due

to the charge subtracted by the feedback loop), then an optical '0' is received. The

receiver implemented in [14] was able to resolve a 11-pA input current at 1.6-Gb/s

with a power consumption of only 3-mW. The design was implemented in a 0.25-tum

CMOS process with a photodiode capacitance of 420-fF.

Figure 1-3f shows an updated version of [14], as presented in [6], as part of a

complete optical transceiver. In [6], the receiver demultiplexes the data stream into

five parallel receivers by means of five different clock phases. Each of the data receivers

sequentially uses two consecutive clock phases to implement the double-sampling

previously described. This allows the receiver to integrate the input photocurrent for

an entire bit-time and then evaluate the decision for another bit-time, significantly

increasing the sensitivity. This yields a high data rate while only using a single

photodiode and a relatively low-speed clock.

1.4

Contributions of this Thesis

This thesis presents the first-generation implementation of an optical data receiver

for monolithically-integrated silicon photonic interconnects. The optical receiver presented is a photocurrent-sensing receiver that amplifies the input signal by means of a

modified sense amplifier. The amplification is enabled through the positive feedback

of two cross-coupled inverter structures in the latch.

The challenge in this work is to design a highly energy- and area-efficient receiver

for massively integrated applications, that is is robust to process and noise in a highly

digital environment. The additional practical challenge associated with this work is

that monolithic silicon photonic devices are still under development, so this receiver

has to be flexible enough to accomodate a large range of device variations. The issue

is compounded by the fact that the work is done in a pilot 32-nm process, where

creating a large and complex chip is extremely difficult.

1.5

Summary

In this chapter, the use of optical interconnects for emerging multi- and many-core

processors was presented. The main building blocks of an electrical-optical-electrical

link were outlined, with particular attention paid to the optical data receivers. The

two main types of optical data receivers (current-sensing and current-integrating) were

contrasted against each other. Finally, the design and implemenation of a highlydigital, monolithically-integrated optical data receiver in a 32-nm process was then

introduced as the goal of this thesis.

Chapter

Receiver Design

The optical receiver presented in this work is a highly-digital, synchronous, currentsensing data receiver that interfaces with a monolithically-integrated photodiode. The

simulated receiver will be shown to be able to resolve input photocurrents of less than

50-pA at 5-Gb/s with a power consumption of less than 500-pW (100fJ/bit). In this

chapter the optical receiver is introduced. An overview of the receiver illustrates its

basic operation. Each of the parts of the receiver is then presented and examined in

more detail.

2.1

Recever Block Diagram

+

Buffer

+

Latching Sense

V

SAmplifier

V n

Photodiode

Clamp

Buffer

Vbuf-

Vbuf +

Vout

+

Dynamic-to-Static

+

Converter

-Oglobal

enable

-

Vout-

Clock

Enable

Figure 2-1: Block diagram of the optical data receiver implemented in the EOS2 test

chip.

i

-i-^lii)

i-iiilii--i::

--- i--i----~~~-'~-~-i'~~~~W*-i*~~il-.i~~

~i~-~i

The optical data receiver presented in this thesis is shown in Figure 2-1. The receiver consists of several highly-digital blocks, including one that provides feedback.

The front-end of the receiver consists of a monolithically-integrated photodiode connected directly to a modified latching current-sense amplifier. The output of the latch

(dynamic signals Vdy,+, -) is then buffered and converted to static signals V,,t+, -

that are valid over an entire bit time. The buffered signals Vbuf+, - are also used

to drive a feedback block that shorts the photodiode once the bit decision has been

made.

The entire receiver is driven by a clock that can be disabled if the receiver is

not to be used. Disabling the clock eliminates switching-power consumption in the

rest of the receiver. The only block that would consume static current is the offsetcompensation block inside the Latching Sense Amplifer. A separate configuration bit

disables the bias in this block, eliminating power consumption in the disabled mode.

The optical receiver operates in two clock phases, receiving 1 bit per clock period.

In the reset phase (first half clock cycle), the sense amplifier is reset to a metastable

initial state. In the evaluation phase (second half clock cycle), the latching sense

amplifier evaluates the current generated by the photodiode.

By the end of the

evaulation phase, the output of the sense amplifier has been resolved to a digital

value that is then stored at the onset of the next reset phase.

2.2

Photodiode

The main element that allows the optically-modulated data signal to be converted

into the electrical domain is the photodiode, which converts incident optical power

into electrical current that can be detected. The design, simulation, and implementation of the photodiode used in this work was done by Jason Orcutt. Some key

modelling parameters and theory of operation are presented in this section.

2.2.1

Semiconductor Material

The mechanism by which a photocurrent is generated by an optical optical signal

is the absorption of a photon, and consequently the generation of an electron-hole pair

in the depletion region of the diode. The electric field that exists in the depletion

region then causes the electron and hole to be swept to the n- and p-doped terminals, respectively, creating a current that can be measured at the diode's terminals.

Some of the fundamental parameters to consider are the bandgap of the material,

which describes the amount of optical energy required to excite an electron from the

valence to conduction band and create an electron-hole pair, the wavelength of the

incident optical power, which describes how much energy each incident photon has

(Equation 2.1), and whether or not the the semiconductor material has a direct or

indirect bandgap. The absorption coeffecient, a [cm

- 1]

describes how much light is

absorbed by a material, and can be plotted as a function of wavelength.

Ephoto =

he

(2.1)

Ge

E

E

Eg,d,

0.6

0.8

1.0

1.2

1.4

1.6

1.8

Wavelength [pm]

Figure 2-2: The absorption coeffecient plotted against wavelenth of light [15].

Figure 2-2 shows the absorption coefficients for silicon and germanium at various

wavelengths. Note that since silicon has an indirect bandgap structure, its absorption

rolls off slowly. Germanium, which has an indirect bandgap around 1.8-um also rolls

off, but at its direct bandgap between 1.5 and 1.6-nm the absorption increases quickly

with photon energy.

The photodiode material used in this work is a Silicon-Germamium (SiGe) alloy. The availability of this material is a fortunate coincidence. SiGe is becoming

more common in advanced CMOS processes, as the Germanium is implanted into the

drain regions of the PMOS transistors in order to improve mobility. We exploit the

availability of the Germanium in order to create the photodiodes.

With the photodiode created using SiGe, and the optical waveguides (which should

have as little absorption as possibile) created using polysilicon, an appropriate range

of wavelengths for the light in this work can then be selected. The wavelength should

be large enough that the light is not absorbed by the poly-silicon waveguide, but

also small enough that it can be absorbed by the high-absorption direct-bandgap of

the Germanium in the SiGe. The exact wavelength used will also be a function of

the mole fraction of Germanium, with the anticipated range for this process being

1200-1300-nm.

2.2.2

Geometry

Once the semiconductor materials for the photodiode have been selected, the geometry must be designed. The layout of the photodiode relative to the direction of the

incident optical power depends on the application, and will affect design metrics such

as the efficiency and responsivity of the diode, which describe how much current will

be generated per incident optical power. The efficiency of the photodiode describes

how many electron-hole pairs are generated per incident photon. The responsivity is

defined as the amount of photocurrent generated per incident optical power, and can

be used directly in a link-budget calcuation.

In the case of the EOS2 test chip, the incident optical power is propagating down a

poly-silicon waveguide, and must be absorbed near the termination of the waveguide.

Figure 2-3 is a simulation result that shows the intensity of the optical power through

---

,

I

_I

Figure 2-3: A cross-sectional view of the waveguide showing the mode propagation.

[Figure courtesy of Jason Orcutt]

the core of an integrated waveguide. It is the portion of the mode outside of the core

that will be absorbed.

Figure 2-4 shows a model of the photodiode placement relative to the waveguide

termination. The model (not to scale) shows that the photodiodes are made using

the same p-n junctions as in the MOSFETS of the process. The p-n junctions are

oriented radially away from the waveguide, ensuring that there is an absorptive region

along the entire length of the waveguide. Photodiodes are placed on each side of the

waveguide in order to maximize absorption. The terminals are then tied together

using the metal layers, in order to collect the photocurrent in parallel. A final layout

picture of the photodiode can be seen in the far-right of Figure 4-3b.

'I-

-,~

r

-

-

--

I

Figure 2-4: A 3D model of one of the photodiodes implemented in EOS2.

2.2.3

Photodiode Model

One of main challenges with designing any system composed of both optical and

electrical elements is properly modelling one set of elements in a manner that fits

into the design environment of the other. We needed to create a model of the photodiode that could be integrated into the existing electrical design flow. The basic

functionality of the photodiode is represented by a current source, representing the

photocurrent that is generated when the photodiode is excited by an optical source,

and a capacitance that is seen across the diode's terminals (Figure 2-5).

*l

on,off

diode

Figure 2-5: Photodiode Model

In this work, the modelling is particularly challenging, as all of the optical elements

are implemented monolithically in a CMOS process with relatively little information

I

I

~-

about critical doping concentrations and other photonic design and variation parameters.

As a result, we use reasonable estimates for the diode's parameters. The dark

current of the diode should be very small and is therefore negligible. This is because

the p-n junctions used are the same as those used in transistors, and the dark current will be on the same order as any leakage. The relatively small dimension of

the diode enables fast operation even without a reverse bias, enabling the interesting

current-sensing receiver described in this work. The difference between the diode's

on- and off-currents was taken to be 10-dB, due to the expected extinction ratio of

the modulator implemented on the chip. The diode capacitance used is 10-fF. Note

that this capacitance is significanly smaller than other diode capacitances in the optical communication literature, due to the fact that it is monolithically integrated.

While this is certainly good, the penalty that is paid is that in a monolithic implementation, the photodiode material selection is limited only to what is available in

the process. The absorption, and correspondingly the photocurrent and sensitivity,

therefore potentially suffer from monolithic integration.

2.3

Latching Sense Amplifier

For this thesis work, an optical data receiver based on a current-sense-amplifier

is proposed. The current-sense-amplifier with the photodiode connected to the input terminals is show in Figure 2-6. As described in Section 2.2, the photodiode is

modelled as an ideal current source in parallel with a capacitance. The latch design

leverages the fact that the photodiode used can be operated without a reverse-bias

applied across its terminals. This allows for a fully differential, highly digital receiver

to be designed, without having to worry about biasing the diode.

In the reset phase, all of the latch's terminals are precharged to the supply. The

photodiode is shorted. During the evaluation phase, transistors M 1,2 are enabled

by the clock, and each branch of the latch begins to discharge. If an optical 1 is

received, then a photocurrent will be generated, causing current to flow from the node

------lr~'-"~~"~""~"-*ri;i~:r-^-)?ic~~~ ~

Figure 2-6: The latching data receiver implemented on the EOS2 test chip.

in- to node in+. This will cause the negative branch of the latch to discharge more

quickly, and therefore latch low. In the absence of a photocurrent, the branches would

discharge at an equal rate, and (without offset compensation) the latch would not be

able to make a decision. Offset compensation will be examined in the next section,

and can help the negative branch to latch high in the absence of a photocurrent.

The latch's transistor sizes were selected based on speed and sensitivity constaints,

as detailed in [16]. NMOS transitors M1,2 are ideally made small, in order to maximize

the evalutation time of the latch. Non-minimum-size devices were used in order to

achieve the target data rate. The latch itself consists of two cross-coupled inverters

(NMOS M3 ,4 and PMOS M5,6 ). In each of the inverters, the NMOS-to-PMOS sizing

ratio was made larger than that used for a balanced inverter. This serves to lower

the threshold of the cross-coupled inverters, and again increases the evaluation time

where the positive-feedback integrates the input signal. Resetting the latch is achieved

through transistors M7 ,8,9,10 which precharge all of the internal nodes high. Transistor

M11 further balances the two latch branches in the reset phase. Transistors M 7,8,9,10,11

are ideally small to reduce parasitics.

2.4

Offset Compensation

Figure 2-7: 7-bit offset compensation scheme for latching data receiver.

The latching sense-amplifier presented in Section 2.3 is a differential structure

and is nominally perfectly balanced. This balance can be disrupted through process

variation, which can only be compensated after fabrication, and so a programmable

offset compensation block must be implemented. The offset compensation must have

a range that is sufficiently large to counter the effects of both optical and electrical

variation, but also enough resolution to measure the eye diagram in situ as will be

presented in Section 3.5.

The offset compensation is also required to upset the balance of the latch during

nominal operation. When an optical-1 is received, the photodiode in Figure 2-6

generates a current from node Vi,-

to Vi,+. This will cause Vi,+ to discharge more

slowly and therefore latch high. When an optical-0 is receiver, though, little or no

I

L

I

----------------

..

..........

i : -lil-

- -

- - - - --

photocurrent will be generated, and the latch input will appear to be approximately

zero. Without compensation, the decision that the latch will make will be random

and dependant on noise at the inputs. Offset compensation is therefore used in order

to raise the threshold of the latch, so that V,,t+ will always latch low for an optical-0.

140

-

-Clock

Speed:5GHz

120

100

80

60 . -.

.............

.

40

20

,. .

0

0

i

.

20

40

i.

60

80

100

120

1

DAC Code

(a) Offset Compensation Codes

S1LSB=uA

......... .... : i ....................

*

1 LSB= 1.1uA

.. ..................

.....

. :

. ...

: ....

....

...

....

....

...

....

...

....

...

..

..

, ...

,, i

r

0

:- 6646

..

1-

j-

:

*

-1

"2

0

20

40

60

80

DAC Code

100

120

140

0

(b) Integral Nonlinearity Error

*

20

40

80

60

DAC C ode

100

120

140

(c) Differential Non linearity Error

Figure 2-8: Offset compensation performance.

The offset compensation is shown in Figure 2-7. The compensation consists of a

digitally-programmable binary-weighted current mirror (transistors M30-M43) that

pulls additional current off of one of the two input nodes shown in Figure 2-6. Transistors M30-36, which have the same gate bias, have binary-weighted widths to generate

the binary-weighted currents. Transistors M3 7- 4 3 control which branches are enabled,

and are sized the same as M30-M36 to ensure that branches carrying more current

have a correspondingly smaller impedance. The node that is compensated is controlled by transistors M46 and M4 7 . The gate bias for the binary-weighted current

branches is generated by transistors M25- 29 . In the event that offet compensation is

~!

!! .

. . . . . . . . ... .

. . .. . . .=

.. _

...

.

..

.. . i

+

not required, the current mirror can be completely shut off by turning M 24 on and

M25 off. This sets the bias voltage equal to zero and prevents any current from being

generated in the branches.

Figure 2-8 summarizes the performance of the offset compensation block. Figure 28a shows the meta-stable input current that correspondes to of the 128 codes. The

range of compensation was determined based on variation analysis that will be further

analyzed in Section 3.2. It is interesting to note the non-ideality of the codes near the

origin. this shift in the transfer function is due to the capacitance that is added just

by turning on transistor M46 . The magnitude of the shift then represents the amount

of current required to overcome this additional capicitance. Figures 2-8b and 2-8c

show the integral-nonlinearity error (INL) and differential-nonlinearity error (DNL)

of the DAC, respectively. These metrics describe the linearity of the DAC.

In order to configure the offset compensation, the following steps should be carried

out experimentally. Here they are done in simulation for the purpose of this thesis.

The results are summarized in Table 2.1.

1. Determine the threshold for the receiver when the input bit is an optical 0.

2. Determine the threshold for the receiver when the input bit is an optical 1.

3. Set the offset compensation to the code half-way between the two thresholds

found in steps 1 and 2.

ION,IoFF

Optical '0'

Optical '1'

Optical

DAC

(p

1 A)

120,12

100,10

80,8

60,6

40,4

20,2

Threshold

9

8

7

6

5

2

Threshold

103

80

61

44

29

14

Threshold

56

44

34

25

17

8

Configuration

100 0111

101 0011

101 1101

110 0110

110 1110

111 0111

Table 2.1: Example configuration data. Threshold values are found using Figure 2-7

2.5

Latch Output Buffer

Vdy n +/-

>0,

Vbuf-/+

Figure 2-9: The output buffer of the optical receiver.

The latch shown in Figure 2-6 is followed by a buffer stage. The buffers are

implemented as inverters, as shown in Figure 2-9. The purpose of the buffers is to

increase the sensitivity of the latch at the cost of delay.

For a given clock speed, the sensitivity is improved as the capacitance seen at

the output nodes is a much weaker function of the previous bit received. This is

because the capacitance looking into the dynamic-to-static converter, presented in

section 2.6, depends strongly on the previous bit, which it holds on floating nodes

until the decision for the current bit is made.

During the implementation of the EOS2 test chip, an error was made in the

placement of this buffer. The output of the latch was fed directly into the input of

the dynamic-to-static converter. The buffered signal was used only in feedback for the

photodiode clamp. Not only does this error mean that the capacitances seen at the

decision nodes of the latch will depend on the previous bit, but the feedback clamp

is also delayed by an inverter delay. The simulation results presented throughout the

thesis use the flawed schematic just described, in order to be able to more closely

match measured results with simulation. The advantage of the flawed design is that

there is less delay between the clock signal and the output data becoming valid.

2.6

Dynamic to Static Converter

The dynamic-to-static converter used in the optical receiver is shown in Figure 210. Dynamic-to-static conversion is necessary because the output decisions from the

latching sense-amplifier are only valid for half of a bit-time (they are reset during the

Vbuf-

M21

M18

M19

M2

Vu-

M20

M16

M1

M22 -

Vout-

V

Vbu+

Vout +

M

M12

buf

M13

Figure 2-10: Dynamic-to-static schematic.

other half). The output of the dynamic-to-static converter is valid over the entire bit

time.

The dynamic-to-static converter consists of two cross-coupled tristate buffers (transistors M12 -19). While the clock is high, the latch output bits can be set through transistors M20-23 based on the decision of the sense-amplifier. During the receiver's reset

phase (I=0), the tristate buffers become cross-coupled inverters, holding their previous values. The output dynamic-to-static converter's output nodes are not driving

by any other signal, as V b; + /- are both high.

2.7

Photodiode Clamp

Vbuf+

In+

Vbuf-

In-

Figure 2-11: The photodiode-clamping circuit used in the optical data receiver.

The photodiode clamping circuit used is shown in Figure 2-11. The clamp consists

of a single NAND-gate that drives an NMOS transistor. The NAND-gate is connected

to the outputs of the sense-amplifier, before the dynamic-to-static conversion. During

the precharge phase, the sense-amplifier outputs are both HIGH, and the NAND's

output will be 0. During the evaluation phase, the sense-amplifier's outputs start off

the same and then diverge to a decision. It is only once the divergence has occurred

that the NAND's inputs differ, yielding a HIGH signal at the output that enables the

clamping NMOS. Therefore, the photodiode is only shorted once the bit decision has

been made.

The photodiode must be shorted in order to prevent a forward-biasing of the substrate. At the end of the evaluation phase, the photodiodes terminals are connected

to two virtual grounds (being held by transistors M1, 2 ). If additional photocurrent

causes Vi,-

to go below ground, then the M2 will have to start pulling the node up

to ground, which an NMOS cannot do well. If Vi,-

is driven low enough, the diode

formed by the N-doped drain of M2 and the P-type substrate could turn on.

2.8

Clock Enable

enable

Figure 2-12: The clock-enabling block for each optical data receiver.

The clock-enabling scheme is shown in Figure 2-12. The Figure shows that the

clock used for each data receiver is derived from a global high-speed clock. By setting

the enable bit low, the local clock will not oscillate, and the rest of the highly digital

receiver will not switch, eliminating power consumption aside from leakage.

2.9

Summary

This chapter introduced the highly-digital, synchronous, current-sensing data receiver presented in this work. The receiver's basic operation was outlined. Each

of the components of the receiver was then presented, with operation and design

decisions explained. In the next chapter, circuit simulations are presented in order

to further illustrate the circuit's functionality, and also to demonstrate the achieved

performance.

Chapter 3

Receiver Simulation

In the previous chapter we outlined the design of the optical data receiver, showing

how each of the blocks were designed and work together. In this chapter, the full

operation is shown with simulated results. The simulations further illustrate how the

receiver operates, as well as analyze the performance achieved.

3.1

Transient Simulation

The in-depth analysis of the optical data receiver starts by first looking at the

waveforms at the nodes of the data receiver. To do this, a transient simulation is set

up, as shown in the testbench Figure A-1. The current source of the photodiode's

model is set to be a pulsed current source, with each pulse representing a bit of data

to be received. The offset compensation is set such that the threshold value is placed

between the 1- and 0-bit threshold values, as determined by Table 2.1.

Figure 3-1 shows the receiver voltage waveforms during multiple bit decisions.

In this example, the photodiode on-current was set to 100-ipA, while the off-current

was only 10-pA, assuming an extinction ratio of 10-dB. The current signal (Figure 3ib) was initially low, and transitions HIGH in time for the first rising clock edge

(Figure 3-1a).

When the clock transitions high, the two photodiode input nodes

(Figure 3-1c) both race toward ground. At 200-ps, the positive node has current

being driven onto it from the photodiode, while current is being removed from the

i;L

~ --

=----:~.-----r)l-;-~-i;_-~-_-1CI

_

o 0.5

0

.

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

0.7

0.8

0.9

0.7

0.8

0.9

0.7

08

0.9

1

Time (ns)

(a) Clock Signal

Time (ns)

(b) Photodiode Current

0.5

>

0

0.2

0.3

0.4

0.5

0.5

Time (ns)

(c) Input Node Voltages

z

0.5

0

0.2

0.3

0.4

0.5

0.6

1

Time (ns)

(d) VDYN

0.2

0,3

0.4

0.5

0,6

Time (ns)

(e) V,,t+

Figure 3-1: Transient simulation waveforms demonstrating bit decisions.

negative node at the same time. This causes the negative node to race toward ground

more quickly. Figure 3-1d shows the response of the dynamic decision nodes of the

receiver (labeled Vdy, + /-

in Figure 2-6). During the reset phase, when the clock

44

is LOW, all of the internal nodes are pre-charged HIGH. When clock goes HIGH

during the evaluation phase, it is clear that if an optical '1' is being received, the

cross-coupled inverters cause Vdan+ to latch high and Vdayif an optical 'O' is being received, such as at 600- and

and Vday-

8 0 0 -ps,

to latch low. Similarly,

Vdyn+ will latch LOW

will latch HIGH. The outputs of the basic receiver are dynamic however,

and must be integrated into a static system. Figure 3-le shows the positive output

of the dynamic-to-static converter. The data at this node is valid for an entire bit

period.

Latch

Offset Compensation

Output Buffer

Dynamic-to-static Converter

Photodiode Clamp

Clock Enable

Power (uW)

110.2

237.5

2.4

12.6

0.3

53.4

Total

416.4

Table 3.1: Power consumption for each block of the data receiver during 5-GHz

operation with a 100-uA 'on' photocurrent.

Power consumption analysis is presented in Table 3.1, where the power of each

block is shown for operation at 5-GHz and a photodiode 'on' current of 100-uA.

From the table, it is clear that the offset compensation block dominates the power

consumption. Despite the use of current mirrors with ratios larger than 1, this power

results from the total range required by the compensation, while ensuring that all

mirroring transistors are near saturation. It is important to note that this power

consumption will decrease should the offset not be required to shift so far. This may

be the result of a smaller photodiode 'on' current, or from process variation. In the

former case, the problem that would arise is that the measurable eye-diagram would

have less vertical resolution. That is, the number of offset codes required to sweep

out the vertical opening of the eye would decrease. Therefore, future work should

address an offset compensation scheme that can add resolution without requiring

such a large photodiode 'on' current (which requires a large compensation power). A

.__.

~~;~~__;_~~_~

~ ~.

.~~. ~.._

_.....~.....l__,x

I-I-

--

-------

;l;x

r.

programmable array of gate capacitances is a good solution.

The energy-per-bit is computed from Table 3.1 to be 83.3-fJ/bit. From Table 1.1,

it is clear that the energy-per-bit of the data receiver is competitive with the current

state of the art, though it only represents simulated results. Power was measured

using the method presented in Appendix B.

3.2

Offset Compensation Simulation

The offset compensation block of the optical data receiver was introduced in the

previous chapter, and is a particularly crucial block. It is the means by which the

threshold of the receiver can be set in order to accomodate different incident optical

powers. It is also the means by which the eye diagram of the receiver will be measured.

As a result, the offset compensation transfer function must be determined carefully.

The testbench for the offset compensation simulation is shown in Figure A-2. The

figure shows that for each experiment, the input photocurrent is set to a DC value,

and an offset compensation code is set. A transient simulation is then run, with a

5-GHz clock driving the optical data receiver. For each compensation code, the DC

current value is increased over multiple simulations. When the positive output of the

receiver eventually latches positive, it means the meta-stable current-code pair has

been determined. The resulting transfer function was presented in Figure 2-8a.

3.3

Setup Time

One of the main metrics in evaluating the performance of a digital block is the

relationship between the setup time and the delay. The setup time is defined as the

time between a change in the input data and the rising edge of the clock. The delay

through the block is the time from the positive edge of the clock to the change in the

output of the block.

In this section we examine the effect of the data input's phase and magnitude

on the ability of the data receiver to evaluate the correct bit. Figure A-3 shows

the testbench for the setup time test. The figure shows that the phase of the data

transition relative to the rising clock edge was swept (Tsetup). The propagation delay

from the positive clock edge to the final latching of the data (Tdelay) is then plotted

against the setup time, with power recorded for each measurement. Note that delay

was measured as the time between each waveform reaching half its final value.

For the optical data receiver proposed, the propagation delay was recorded for

a range of setup times across several input signal strengths (which all assumed an

extinction ratio of 10-dB). The results are shown in Figure 3-2.

Figure 3-2a shows the propagation delay plotted against the setup time for a range

of input photocurrents. The plot shows that for larger input optical powers (and

therefore larger photocurrents), the propagation delay through the optical receiver

decreases. This directly relates to how quickly the receiver can be clocked while still

receiving the correct bits. Figure 3-2a also shows that as the setup time decreases,

the propagation delay through the latch increases. This is due to the fact that the

input photocurrent must charge various parasitic capacitances at the input terminals

in order to impact the circuit.

Figure 3-2b shows another performance metric: the total delay of the latch, equal

to the sum of the setup time and propagation delay. From the plot, it appears that

the fastest operation will be achieved from minimizing the setup time.

Figure 3-2c shows the power consumption of the receiver for each of the input

signal strengths. It is interesting to note that the power actually increases as the

signal strength increases. From Table 3.1, we know that this is because a larger

threshold shift (and therefore larger offset current) is required for larger input optical

powers.

Note that the discrepency between the larger total power in Figure 3-2c

with respect to the number reported in Table 3.1 is due to a set of buffers that were

included in the testbench. The buffers were test structures and Table 3.1 is the true

power measure.

_L

I

1111

ill

:

---

120-uA

--....

80-uA

.....

100-uA

+

++ + .

+

:o

Scooo

.000.

.00

0.

I

0

-10

+ + + ++ ++

I

10

0,00o.

*

60-uA

o

40-uA

+

20-uA

.

I

30

20

i

40

5

Ttp

(ps)

(a)

Propagation

Delay

plotted

against the setup time.

(a) Propagation Delay plotted against the setup time.

Tetup (ps)

(b) Total Delay plotted against setup time.

i-

-

--

----- 120-uA

10 0-u A

....... ...................

..................

. .............

..........

...

*

+

*

**

*+

*

444**

++++++

Ii

0

t + ++

10

.......................

*

*

+

4*

* *

. .. .. .. .. . .. .. .. .. .. .. .. .. .

+ +:+++++

I

-10

.* *

++-+

i

20

Tsetup (pS)

*

4*

*

*

*

30

60-uA

6

0-uA

40-uA

+

20-uA

*

. ... . ..

++++ + +:+++++

0

**4

*

. .. .. .

+++

++

40

(c) Average power over a bit period plotted against setup time.

Figure 3-2: Propagation delay through the latch plotted against setup time. The

input photocurrent was varied, and the input data is switched from 0 to 1. Clock

frequency is 5-GHz.

3.4

Characterization of the Receiver's Sampling

Aperture

This section characterizes the sampling aperture of the latch-based optical receiver. The sampling aperture gives us a way to measure the bandwidth of the receiver. The characterization follows the analysis presented in [17], where the latch's

bit decision is represented as a weighted time-average of the input signal. One difference between the work in this thesis and that in [17] is that our input signal is

current-mode. The DC gain that we present here is a then a transimpedance gain as

opposed to a unitless one.

The testbench for the aperture characterization is shown in Figure A-4. The input

signal consists of a photocurrent step that again assumes a 10-dB extinction ratio.

The step's phase relative to the clock is swept, and for each phase, the receiver's

threshold is swept by changing the offset compensation code. The latch's bit decision

is recorded. The phase-configuration-bit space can then be plotted, showing all of the

metastable points and yielding an eye diagram.

Figure 3-3 shows the the simulation results from the receiver's aperture analysis for

a 0-1 step transition (the results for a 1-0 step transition can be found in Appendix C).

Figure 3-3a shows the offset current required to bring the latch to a meta-stable

state for each phase of the input step. From the figure, we can see that if the step

signal arrives early (negative phase), then the input nodes have time to settle and the

input photocurrent appears as a DC signal. The meta-stable code is then predicted

by looking at Figure 2-8a. As the step occurs closer and closer to the clock edge,

its photocurrent will have less and less impact on the latch's decision. Less offset

current is required by the compensation block to match the input signal, and we see

a decrease in the metastable code. In the extreme, when the bit arrives much later

than the clock edge, the offset compensation block must only match the off-current

of the input signal. Again, this appears as a DC-input that can be predicted by

Figure 2-8a.

Implicit in the code plotted in Figure 3-3a is any non-linearity in the current-DAC

~r

-. -.r-- ---,-..rr-x---- ---r--;;

- ;-- i:r---iici-r;-;i-ii.;cr;;;.ii i;.i;r--a;;i;r~:il---r;r~r~li;r~;=r--l

-~~~;ir~~B~"

;;~~

':;~-~~~~i

w~~;i_::

70

- 40-uA

- - 60-uA

--- 80-uA

60

50

40

30

--- .

...............

20

20

10

0

-100

K

.........

L

-50

0

50

phase (ps)

100

150

0 -100

-50

0

50

phase (ps)

(a) cMS(-r)

100

150

(b) IMS(7)

x 1010

phase (ps)

phase (ps)

(c) SSF(T).

(d) ISF(r-).

235

234

,_ 231

230

40-uA

-- 60-uA

-- 80-uA

0

200

400

600

Frequency GHz

(e) FFT(ISF)

800

1000

229

228

-----0

40-uA: BW=14.9-GHz

60-uA: BW=14.9-GHz .............

80-uA: BW=14.9-GHz

5

10

Frequency GHz

15

(f) FFT(ISF) (zoom view)

Figure 3-3: Sampling apertuture characterization for 0-1 step input.

i=.

-;

shown in Figure 2-7. Using the transfer function in Figure 2-8a, the meta-stable code

(cMS) is mapped to a meta-stable input current (IMS), shown in Figure 3-3b.

The Step Sensitivity Function (SSF) is defined by Equation 3.2, and is used to

plot a normalized version of the IMS, shown in Figure 3-3c. If the slope of the step

transition is large, it means that the receiver is very sensitive to the arrival time of

the input step. The receiver's sampling aperture would be considered fast.

SSF-()

Is(T)

norm(

ISForm(T)

maz(IMs(r)

=

- min(Ins(T))

)

-

min(Ins(T))

SSForm(T)

(3.1)

(3.2)

The Impulse Sensitivity Function (ISF) is defined in Equation 3.2 as the derivative

of the SSF, and is plotted in Figure 3-3d.

Through examination of the SSF, we

determined that an SSF with a steeper slope has a smaller aperture in time during

which it samples its input. This is seen directly in Figure 3-3d, where a receiver with

a smaller aperture would appear to have a sharper impulse.

Since this impulse the same impulse that we are using to sample our imput, it must

be thin enough (have enough bandwidth) to accomodate our desired data rate. As

discussed in [17], the bandwidth of the latching receiver can be computed by taking

the FFT of the ISF and measuring the 3-dB bandwidth. Figures 3-3e and 3-3f show

the FFT of the ISF. From the figures, the bandwidth of the receiver is clearly larger

than 10-GHz for each of the input current step sizes measured. This verifies that the

latch is fast enough for the 5-Gb/s target data rate.

3.5

Eye Diagram

In the previous section we used the SSF and ISF to characterize the sampling

aperture of the latching optical receiver. We can also use the cfgMS to create an

in situ eye diagram. In order to obtain the eye diagram, the IMS is recorded for a

different bit transitions (010,100,101,000,etc) and then superimposed. The resulting

I

80

60

V 40 ......

40 uA

20

..

-100

-50

0

50

100

150

time (ps)

200

250

300

350

(a) 40-uA step input.

60 ......

C_ 40

-.......

60 .........

20

. .

-100

..........

..........

.......

....

t-.....6 OuA

..

..

-50

0

50

100

150

time (ps)

200

250

300

350

200

250

300

350

(b) 60-uA step input.

80 ....

-100

50

0

50

100

150

time (ps)

(c) 80-uA step input.

Figure 3-4: In Situ eye diagram from simulation.

plot is shown in Figure 3-4, and represents a plot of metastable currents for each

phase. The plot is used to determine the optimal sampling phase and threshold value

for each optical signal power.

It is important to emphasize that this is an experiment that will be performed onchip, and will be the only method to measure an eye-diagram. The difference between

the chip measurment and the one presented here is that while the eye diagram shown

in Figure 3-4 is derived from a single ideal transient simulation for each phase and

offset value, the on-chip measurement will take the average of 220 such simulations

for each phase and threshold value.

3.6

Process Variation

One of the major challenges with using such an advanced CMOS process as 32-nm

is combating the process variation and mismatch. These effects were mitigated by

implementing an offset compensation block with sufficient range to accomodate the

worst variation. The offset compensation block was presented in Section 2.4. In this

section, the performance of the compensation block is examined through variation

analysis.

Process variation is first studied through examination of the threshold shifts of the

latch for a DC input current over several Monte Carlo simulations. The testbench for

the experiment is shown in Figure A-5. The figure shows taht for each simulation, the

input photocurrent is set to a DC value. A transient simulation is then run with the

offset compensation code slowly incremented through the transient simulation, such

that each code will be valid over several high-speed clock periods. When the code is

incremented to the point where the positive output of the data receiver transitions

from high to low, then the meta-stable code that corresponds to the DC input current

for that Monte Carlo run has been found. Note that this threshold measurement

differs from the one used in Section 3.2 because if a new transient simulation was run

for each offset code, the Monte Carlo parameters would be reset.

The results of the DC-input variation analysis are shown in Figure 3-5. The plots

show a transient simulation with a duration of 2560ns. The codes are swept from -127

through 127, as shown in Figure 3-5a, with each code being valid for 10-ns. With a

clock rate of 1-GHz used for this experiment, each code is valid for 10 clock periods,

eliminating the effects of switching the codes during the simulation.

Each input current bias was simulated with 30 Monte Carlo runs. The threshold

for each run was recorded, and the mean and standard deviations computed. The

Gaussian distributions are superimposed onto the threshold plots in Figures 3-5b- 35f.

rl""l~u"~""m"l""x~""-~""""~

50

.

.

.....

...... ..

.

.

. .. ......

.:

.

0-C

: i0

0,5

15

2

25

time (us)

(a) Offset Code

S.

.................... ........ .........SI

I--"m'°°' 0AC0 I

I

I

1____

J.................

L................

I.-r

.

Nominal DAC=0

U

0

0.5

1

1.5

2

2.5

time

x10

(b) Idiode=0-pA

II

I

.

0 5 . .............

.

.-.

..

I0

0"

0.5

..

...........

.........I.........

r

.. .......

..........

..

...............

":

2

1.5

Nominal DAC=16

....... ..

.................

.,

1

-

mean=13

stdev=28

2.5

time

x lo

(c) Idiode=20- A

I

I

r

_

. _ ............

I..................

.