An Automated Method for Data Path Construction by A.

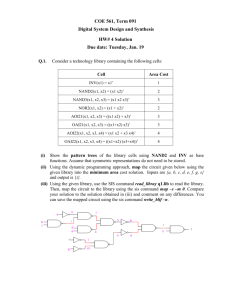

advertisement