©Copyright 2011 Michael Haselman

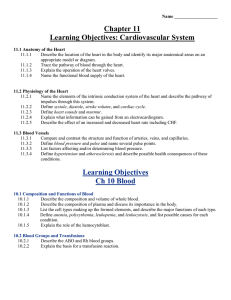

advertisement