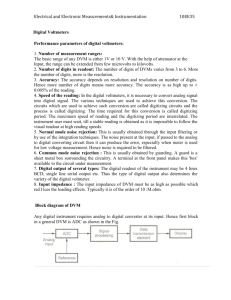

Building Blocks of a 250MHz bandwidth, ... Continuous-time Delta-Sigma Analog to Digital ...

advertisement