Document 10747841

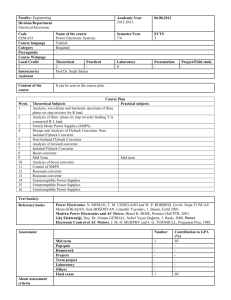

advertisement