Document 10746335

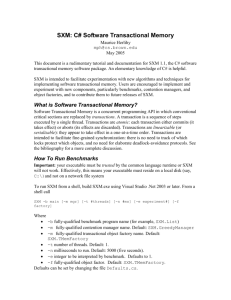

advertisement