Lab 4: “Bad” Logic Circuit Re-Design

advertisement

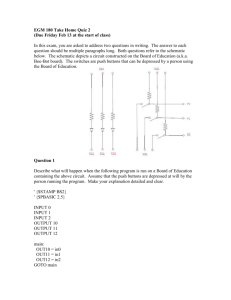

Lab 4 Digital Systems Laboratory ECE230L – Spring 2011 Lab 4: “Bad” Logic Circuit Re-Design Objective: Redesign a “bad” circuit Lab Details: You’ve been hired by a company to re-design an electronic circuit used in a product sold by the company. The boss’ son did the original circuit design. He has produced no documentation for this design, and others have found the design to be sloppy. The only information available is the following schematic (Figure 1) that is used in the assembly area. The test engineer had found that the product consumes too much power, and takes up too much space. However, the friendly criticism didn’t result in any action being taken. The boss has indicated that the anticipated sales volume for the product doesn’t justify custom silicon, which suggests that off-the-shelf chips are his preferred solution (for this lab, “off-the-shelf” chips are represented by the chips found on summary sheets previously supplied to you). It is rumored that a competing company is going to introduce a similar device, so minimizing the number of components to construct the device in order to reduce the cost is a very important goal. The boss is extremely busy and has a short attention span, so you will need to present your re-design very clearly and concisely in a summary document that he can read while he is driving to work (Remember, your job is on the line!). Since the boss often has questions about the details, calculations and other detailed data to support your conclusions need to be included elsewhere in the report. Figure 1. “Bad” logic circuit. Boise State University Electrical and Computer Engineering Department Page 1 of 2 Lab 4 Digital Systems Laboratory ECE230L – Spring 2011 Tasks: 1. Bad Design a. Schematic and symbol b. Simulation to produce wave form 2. Re-design a. Schematic and symbol b. Test bench bad and redesign 3. Proto-board redesign (improved) 4. FPGA implementation (Basys2 board) a. Bad design implementation b. Improved implementation check off ________ check off ________ check off ________ Deliverables: Check-off: TA to check off your completed NAND only circuit by end of lab period (11:55 AM) Submission: Due by Midnight Thursday 2/17/2011 Email: To: ece230lreport@gmail.com cc: your team partner Subject: Lab4_TeamX report (X is your team no.) Attachment: Lab4_TeamX.zip (contents as listed below) Attachment: (must be zip format – no others accepted) Contents of zip file: 1. Report File: \Lab4_TeamX_Report.pdf ReportA Content (create in Word using template previously provided) 1. Team number, team member names, lab no. and name 2. Abstract should serve as summary for the boss – be sure to mention purpose of project, type and number of chips used, and end result 3. The original and simplified Boolean expressions 4. The original and simplified truth table 5. Simplification technique(s) 6. Type and number of chips used 7. Schematic diagram 8. Simulation waveform 9. Results and reflections 10. Schematics and simulation waveforms for all implementations, documenting that your implementation produces the same results as the original circuit designed by the boss’ son After report has been created in Word, create a pdf and then zip. Boise State University Electrical and Computer Engineering Department Page 2 of 2