Large Angle Micro-Mirror Arrays in CMOS-MEMS Peter J. Gilgunn

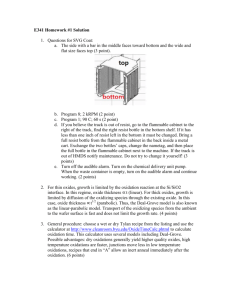

advertisement