CSC Track Finder: Hardware Status Completed a conceptual design CMS Note :

advertisement

CSC Track Finder: Hardware Status

D.Acosta, A.Madorsky, S.M.Wang

University of Florida

A.Atamanchuk, V.Golovstov, B.Razmyslovich

PNPI

EMU and CMS Week

Sept 1999

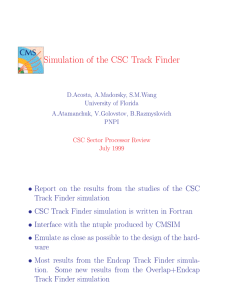

Completed

a conceptual design

CMS Note :

http://www.phys.ufl.edu/acosta/cms/sp design.pdf

Internal review on the design in July at FermiLab

CSC Muon Trigger Scheme

CSC Track-Finder

CSC

Track-Finder consists of 12 Sector Processors

(SP) that cover CSC and CSC/DT overlap

Each SP handles track primitives (LCTs) in = 60

and 1:0 <j j< 2:4

link LCTs into tracks (3-D algorithm)

Measure Pt, and Send 3 best track candidates to the Muon Sorter

Sector Processor Functional Layout

Custom

Backplane

and other devices)

SR

4 st.

Channel Links

Global Buffer (FIFOs)

Unit

CCB

Logic

Extrapolation Units

TAU2

(endcap)

Selection

TAU1

FPGA

Download

Final

(overlap)

Units(LUTs)

Pt-assignment

Storage

Pt-assignment Units (FPGAs)

Data

Channel Links

P1

Control

Output

Logic

VME

Interface

2 Bunch Crossing Analyzer

LED

Drivers

Control Logic

(Clock distribution, SRAM read/write

Transition

SR

1,3 st.

SR

1,2 st.

SR

Barrel

Simplified Sector Processor Layout for Endcap + Overlap Regions

All

components in a 9U VME board

Signals from Sector Receiver (SR) are sent across a

point-to-point backplane to the SP

DT track segments are delivered to SP via a transition

board on the back of the crate

Module

Sector Processor Block Diagram

Bx 0

Reset

3x25

3x25

3x25

6x25

3x25

6x25

Data Line

Control Line

Downloading /

Readout Line

3x24

4x18

3x24

4x18

Input Data

15x18 (endcap)

EU6

24

EU5

23

EU4

13

EU3

12

EU2

MB2 2

EU1

MB1 2

1x9

33-2

33-1

32-4

32-2

32-1

1x9

31-4

31-2

31-1

1x9

23-4

23-3

23-1

22-4

2x18

22-3

22-1

21-4

21-3

2x18

21-1

23-1

23-MB2

23-MB1

1x12

22-1

22-MB2

22-MB1

2x12

21-1

21-MB2

21-MB1

Link 33

2 Bx

Track Assembler Units

Link 32

ME4

ME3

Link 31

ME2

TAU3

ME1

MB2

Link 23

9+6

Link 22

9+6

Link 21

TAU2

14 Bx

Total

2 Bx

9+6

9+6

MB1

FSU

Final Selection Unit

9+6

9+6

9+6

9+6

9+6

Link 23

Link 22

Link 21

TAU1

Global

Buffer

(FIFO)

8x12 (barrel)

Track-Finder Processor. Block Diagram.

Select

MUX

VME

BUS

Clock

3x25

Two Bunch

Crossing Analyzer

8x25 (barrel)

Input Data &

CCB Interface

Input Data

15x27 (endcap)

9U Custom

Backplane

3x25

EU7

34

3 Bx

PC

Serial Port

33-4

3x25

3x25

Input

1 Bx

Output

Connector

Extrapolation Units

3 Bx

Downloading/

Readout

Interface

2 Bx

Pt

assignment

unit

1 Bx

Output

Assignment Unit

Two Bunch Crossing Analyzer : Analyze LCTs

received in two dierent bunch crossings

Extrapolation Unit (EU) : Links LCTs in two CSC

stations together

Track Assembler Unit (TAU) : Use extrapolation results to form tracks

Final Selection Unit (FSU) : Selects 3 best track

candidates

Assignment Unit : Determines the Pt, ,

selected track candidates

Latency expected to be 14 BX

of the

Extrapolation Unit

Endcap

ME4

41

43

4

2

ME3

31

32

33

ME2

21

23

22

ME1

11

12

13

14

15

16

Perform all combinations of extrapolations :

E1i $ E2k, E1i $ E3k, E2i $ E3k,

E2i $ E4k, E3i $ E4k,

no E1i $ E4k (to save logic and reduce random coin-

cidences)

Overlap

Perform all combinations of extrapolations :

B1i $ E2k, B2i $ E2k

Extrapolation Unit in Detail

η road finder

Q2

FF

3

Q1

2

FF

FF

64x2

2

2

LUT

FF

FF

64x1

1

1

SB

FF

LUT

FF

η1−η2

7

128x1

1

LUT

FF

FF

64x1

1

1

FF

3

η

LUT

FF

input

AND

Course Pt assign

LUT

64x7

η

high

enable

FF

7

SB

FF

η −∆ φ

1

SB

FF

η −∆ φ

1

SB

FF

η −∆ φ

1

LUT

FF

8x1

1

h

LUT

64x7

η

η

Z

3 -

6

med

LUT

FF

7

m

FF

32x2

2

Extrapolation

Quality

LUT

1

FF

64x7

6

φ

2

η

low

ABS

FF

FF

7

l

enable

FF

10

10

φ

SB

1

φ1−φ2

FF

10

ψ

FF

SB

LUT

2

FF

32x5

ψ2

5

max

ϕ road finder

1

∆ φ−ψ

FF

5

FF

2

1

6 SB

LUT

32x5

ψ2

ψ

min

∆ φ−ψ

FF

5

SB

LUT

1

FF

32x5

ψ

5

max

∆ φ−ψ

FF

5

32x5

FF

ψ

1

Amb1

FF

input

1

AND

ϕ

FF

1

1

1

SB

LUT

Amb2

2

FF

min

∆ φ−ψ

FF

5

FF

1

1

1

NOT

FF

FF

AND

1

1

1

Global

Clock

1Bx

1Bx

1Bx

Extrapolation Unit for ME1-ME2, ME1-ME3.

Track primitives are matched in (Endcap only)

Assign coarse Pt ( Low Pt, Medium Pt, High Pt)

road nder : match with b of the two LCTs

Results of extrapolations are in form of quality codes

Data Streams to Track Assembler Unit (TAU)

33

33 4

33 2

33 1

3 1, 3 2, 3 4

Extrapolations

32

32 4

32 2

Track Assembler

32 1

Unit

(TAU2)

Track types:

Stream 2

Extrapolation

34

31

32

31 4

31

31 2

Units

234

134

31 1

123

1234

Track Assembler

23 4

Unit

(TAU1)

23 3

23

Track types:

23 1

24

Stream 1

23

21

234

124

22 4

123

22 3

2 1, 2 3, 2 4

Extrapolations

22

1234

22 1

21 4

21 3

21

21 1

Data streams structure

Results

Streams

from extrapolations are sent to TAU in 3

{ Stream 1 : E1 $ E2, E2 $ E3, E2 $ E4 (Endcap)

{ Stream 2 : E1 $ E3, E2 $ E3, E3 $ E4 (Endcap)

{ Stream 3 : B1 $ E2, B2 $ E2 (Overlap)

3

3

12

ME33 ME4

ME33 ME2

ME33 ME1

LINK

33

9

6

3

3

12

ME32 ME4

ME32 ME2

ME32 ME1

LINK

32

9

6

3

3

12

ME31 ME4

ME31 ME2

ME31 ME1

LINK

31

9

6

3

3

12

ME23 ME4

ME23 ME3

ME23 ME1

LINK

23

9

6

3

3

12

ME22 ME4

ME22 ME3

ME22 ME1

LINK

22

9

6

3

3

12

ME21 ME4

ME21 ME3

ME21 ME1

LINK

21

9

6

6 ME23 ME1

4 ME23 MB2

8 ME23 MB1

LINK

23

9

6

6 ME22 ME1

4 ME22 MB2

8 ME22 MB1

LINK

22

9

6

6 ME21 ME1

4 ME21 MB2

8 ME21 MB1

LINK

21

9

6

SRAM

256Kx16

IDT

To Final Selection Unit

From Extrapolation Units

Track Assembler Unit (TAU)

6 bit Ranking &

9 bit hit i.d. :

Endcap:

Overlap:

3 bits for ME1

2 bits for MB1

2 bits for ME2

2 bits for MB2

2 bits for ME3

3 bits for ME1

2 bits for ME4

2 bits for ME2

TAU

implemented as 9 static RAM memories for

Endcap and Overlap

Each Link unit handles all extrapolations to a single

LCT in station 2 and 3. Successful extrapolations are

used to form the best track pattern.

1

1

1

3

4

2

3

1

4

1

1

Id

2

3

4

2

1

1

2

1

3

3

5

6

of the track segments and the quality of the

assembled track are sent to the Final Selection Unit

(FSU)

4

3

1

4 bits:

Station ME1

6

Station ME2

3

Station ME3

3

Station ME4

3

st

nd

2

1

3

AND

stub Bx ID 1 bit;

th

1

4

stub Bx ID 1 bit.

1

To prohibit

Select

Double Count

1

1

MUX

1

AND

MODE

1

0 no

1

(only for 3-stn)

2 1-2-3

1

3 1-2-4

1

MUX

1

AND

4 1-3-4

1

5 2-3-4

1

Stream 3

9

Track 8

9

Track 7

9

Stream 2

Track 6

9

Track 5

9

Track 4

9

Stream 1

Track 3

9

Track 2

9

Track 1

9

Stream3 ME3 key station

9

9

9

Stream 3

Stream 2

Stream 1

Extrapolation Quality Part

9

Track 9

6

Track 8

6

Track 7

6

5

Track 6

6

Track 5

6

Track 4

6

Track 3

6

Track 2

6

Track 1

6

13 MB2-ME1-ME2

9 2-4

14 MB1-ME2

10 3-4

15 MB2-ME2

13

Converter 4

Enable

13

Converter 4

Enable

13

Converter 4

Enable

Converter 17

Sel1 Sel2 Sel3

4

4

Final

(36 Units)

9

12 MB1-ME1-ME2

8 2-3

Converter 17

Decision

36

Unit

17 bits:

st

1

nd

2

rd

3

stub number 5 bits;

stub number 5 bits;

stub number 5 bits;

2-stn or 3-stn mode 1 bit;

overlap or endcap track 1 bit.

To select

(36 Units)

9

Hit Number Comparators

9

11 MB1-MB2-ME2

7 1-3

MUX

4

Comparators

9

6 1-2

Converter 17

9

Extrapolations Quality

Stream 2 ME2 key station

Stream 1 ME2 key station

Hit Number Part

Select

Track 9

µ

1 a Match bit unset

Select

From Track Assembler Unit

stub Bx ID 1 bit;

rd

1

MUX

stub Bx ID 1 bit;

1

Unit (FPGAs)

Station MB2

4

1

To Assignment

4

Unit (FPGAs)

Station MB1

To Assignment

Bunch crossing ID

From 2 Bx Analyzer

Final Selection Unit (FSU)

3 best tracks

out of 9

36

Final Selection Unit

FPGA XCV50 (XILINX)

Compare the qualities of the tracks and the ID of the

LCTs that form the tracks to

{ cancel redundant tracks

{ select 3 best distinct tracks

Assignment Unit

Determines

the , , Pt of the slected 3 best muon

candidates

Pt Assignment

Determines Pt using , measurements from 2 or 3

stations

12

φ

1 sign

1

3 msb

Subtract

φ

13

7 lsb

12

2 vlsb

2

13

Pt LUT

φ

13

8

Subtract

φ

Pt

MX

1 sign

2

4 lsb

8

3

4

4

4

mode

Eta

Pt=Pt 30%

with only 2 stations

Pt=Pt 20% with 3 stations

) improve rate reduction at Level 1

5

mode

Plans

Custom backplane

design has started. Prototype

board will be ready by late October.

SP board layout has started

Begin prototype production in Spring 2000

Test SP + backplane + SR in Summer, nish by Fall

VME Interface

LEDs

Output Data

Storage

Track Assembler Units

Pt-assignment

Unit

Global FIFOs

LVDS Channel

LVDS Channel

Links

Links

Board Layout of the Sector Processor (endcap + overlap region).

SP Layout

Extrapolation Units

Preliminary layout consideration of the Sector Processor

Final Selection Unit