Sector Processor Prototype Reference Manual Introduction University of Florida

advertisement

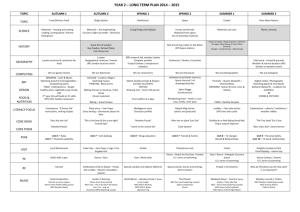

Sector Processor Prototype Reference Manual University of Florida St. Petersburg Nuclear Physics Institute May 28, 2016 Introduction The conceptual design of the Sector Processor 2000 prototype is documented in CMS Note 1999/060. Listed here are amendments to the design specification, as well as details on the data format and VME registers. The trigger algorithms implemented in the SP currently match those used in the ORCA 4.3 simulation package. Table 1: Track categories and ranking used by the Track Assembler Units, Final Selection Unit, and Assignment Unit of the Sector Processor. Number 0 1 2 3 4 5 6 Track Type None ME3–ME4 ME2–ME4 ME2–ME3 ME2–ME3–ME4 ME1–ME3 ME1–ME2 EU PT – – – – – low low TAU Rank 0 1 2 3 4 5 6 AU Mode 0 a 9 8 5 7 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 MB2–ME2 MB2–ME1–ME2 MB1–ME2 ME1–ME3 ME1–ME2 MB1–ME2 ME1–ME3 ME1–ME2 MB1–ME2 ME1–ME3–ME4 ME1–ME2–ME4 ME1–ME2–ME3 MB1–ME1–ME2 MB1–MB2–ME2 ME1–ME3–ME4 ME1–ME2–ME4 ME1–ME2–ME3 MB1–ME1–ME2 MB1–MB2–ME2 ME1–ME3–ME4 ME1–ME2–ME4 ME1–ME2–ME3 MB1–ME1–ME2 MB1–MB2–ME2 ME1–ME2–ME3–ME4 MB1–MB2–ME1–ME2 ME1–ME2–ME3–ME4 MB1–MB2–ME1–ME2 ME1–ME2–ME3–ME4 MB1–MB2–ME1–ME2 – – low medium medium medium high high high low low low low low medium medium medium medium medium high high high high high low low medium medium high high 7 8 9 a b c d e f 10 11 12 13 14 15 16 17 18 19 1a 1b 1c 1d 1e 1f 20 21 22 23 24 f d e 7 6 e 7 6 e 4 3 2 c b 4 3 2 c b 4 3 2 c b 2 b 2 b 2 b AU Quality 0 1 1 1 1 2 1 (barrel) 2 (endcap) 2 2 2 2 2 2 2 2 2 2 3 3 3 3 2 3 3 3 3 2 3 3 3 3 3 3 3 3 3 3 Table 2: Data format of the 16-bit output of Track Assembler Units corresponding to the endcap region. The word is constructed from the hit i.d. for each station and the 6-bit track rank. If the bits are zero for a given station, no track segment from that station was used to construct the track. spare R5 MSB R4 Rank R3 R2 R1 R0 ME4 D1 D0 ME3 C1 C0 ME2 B1 B0 A2 ME1 A1 A0 LSB Table 3: Data format of the 16-bit output of Track Assembler Units corresponding to the barrel/endcap overlap region. If the bits are zero for ME1 or ME2, no track segment from that station was used to construct the track. If the bits are zero for MB1 or MB2, zero denotes a fourth hit in that station. The rank must be used to decode whether or not a hit actually exists in that station. Rank ME2 ME1 spare R5 R4 R3 R2 R1 R0 D1 D0 C2 C1 C0 MSB MB2 B1 B0 MB1 A1 A0 LSB Table 4: Data format of the 21-bit input to an Assignment Unit memory when a 3-station momentum assignment is performed. Absolute phi differences are computed, and the sign bit is the relative sign of the subtractions. For a 2-station measurement, the lowest 12 bits are Phi1 – Phi2. M3 MSB Mode M2 M1 M0 E3 Eta E2 E1 E0 Sign S abs(Phi2 – Phi3) Q3 Q2 Q1 Q0 P7 P6 abs(Phi1 – Phi2) P5 P4 P3 P2 Table 5: Data format of the 8-bit output of an Assignment Unit. A 7-bit track rank is formed from the 5-bit transverse momentum assignment and a 2-bit quality (as the most significant bits). spare MSB Q1 Quality Q0 P5 P4 Transverse Momentum P3 P2 P1 P0 LSB P1 P0 LSB Table 5: VME registers of Sector Processor for A24/D16 operation. The geographical address forms the most significant 5 bits of the 24-bit address. Listed is the offset to this base address for each register. Address Offset 02000 04000 06000 08000 0A000 0C000 0E000 10000 12000 Operation R/W TAU_MB_2A R/W TAU_MB_2B R/W TAU_MB_2C R/W TAU_ME_2A R/W TAU_ME_2B R/W TAU_ME_2C R/W TAU_ME_3A R/W TAU_ME_3B R/W TAU_ME_3C 20000 40000 60000 R/W PT_L (U76) R/W PT_M (U78) R/W PT_H (U80) 01000 01200 01400 01600 01800 01A00 01C00 01E00 R/W R/W R/W R/W R/W R/W R/W R/W 00010 00020 00030 00040 00050 00060 00070 00080 00090 000A0 1E000 Address Counter RESET Status Register Write * CLK (VME) RST (VME) BX (VME) L1 (VME) RSV1 (VME) RSV2 (VME) BXA Shift CLK Start dynamic (or FSU) test FSU Register Write (except FSU test)** Notes: LUT size 256K 16 256K 16 256K 16 256K 16 256K 16 256K 16 256K 16 256K 16 256K 16 (U50) (U47) (U41) (U51) (U48) (U42) (U52) (U49) (U43) DATA_STORAGE_1 DATA_STORAGE_2 DATA_STORAGE_3 DATA_STORAGE_4 DATA_STORAGE_5 DATA_STORAGE_6 DATA_STORAGE_7 DATA_STORAGE_8 2M 8 2M 8 2M 8 (U89) (U89) (U89) (U89) (U89) (U89) (U89) (U89) 256 8 256 8 256 8 256 8 256 8 256 8 256 8 256 8 * Least significant bit = 0 select VME control signals Least significant bit = 1 select CCB control signals ** Least significant bit = 0 TAU LUTs path enable (FIFO disable) Least significant bit = 1 FIFO path enable (TAU LUTs disable) Priority selector ME1* FIFO (phi only) Priority selector me1*_h me1*_m me1*_l MB2 FIFO (phi only) Priority selector mb2_h mb2_m mb2_l MB1 FIFO (phi only) Priority selector mb1_h mb1_m mb1_l me4_l me3_l me2_l me1**_l me1*_l mb2_l mb1_l Stub 1(phi) Stub 2(phi) Stub 3(phi) 21 1 21 1 5 5 sel Final sel Selection mode Unit Extrapolation Unit FPGA chips Final Selection Unit FPGA chip Sign_h eta_h phi_h Pt assignment Unit FPGA chips Assignment Unit LUTs Figure 1: Block diagram of the Assignment Unit of the Sector Processor. Rank_m Sign_m eta_m phi_m 5 5 Stub 1(phi) Stub 2(phi) Stub 3(phi) Rank_h Rank_l Sign_l eta_l phi_l To Muon Sorter ME1** FIFO (phi only) me1**_h me1**_m me1**_l me4_m me3_m me2_m me1**_m me1*_m mb2_m mb1_m 2Mx8 LUT me2_h me2_m me2_l 1 5 5 2Mx8 LUT Priority selector 21 2Mx8 LUT ME2 FIFO (phi+eta) Pt – core (high priority) me3_h me3_m me3_l Pt – core (med. priority) Priority selector Stub 1(phi) Stub 2(phi) Stub 3(phi) Pt – core (low priority) ME3 FIFO (phi+eta) me4_h me3_h me2_h me1**_h me1*_h mb2_h mb1_h High Priority Track Segments Selector me4_h me4_m me4_l Medium Priority Track Segments Selector Priority selector Low Priority Track Segments Selector ME4 FIFO (phi only) if (A B) RC = 1 else RC = 0 Phi_A Phi_B 12 12 A–B B–A RC 12 13 13 1 0 12 Phi_C B–C C–B Mode 4 LUT 13 Pt (to LUT) 8 12 1 0 12 0 1 1 RC 12 RC 12 1 0 12 4 2- or 3-station mode select Figure 2: Block diagram of the core FPGA logic of the Assignment Unit of the Sector Processor.