CSC Track Finder Crate Specification Abstract

advertisement

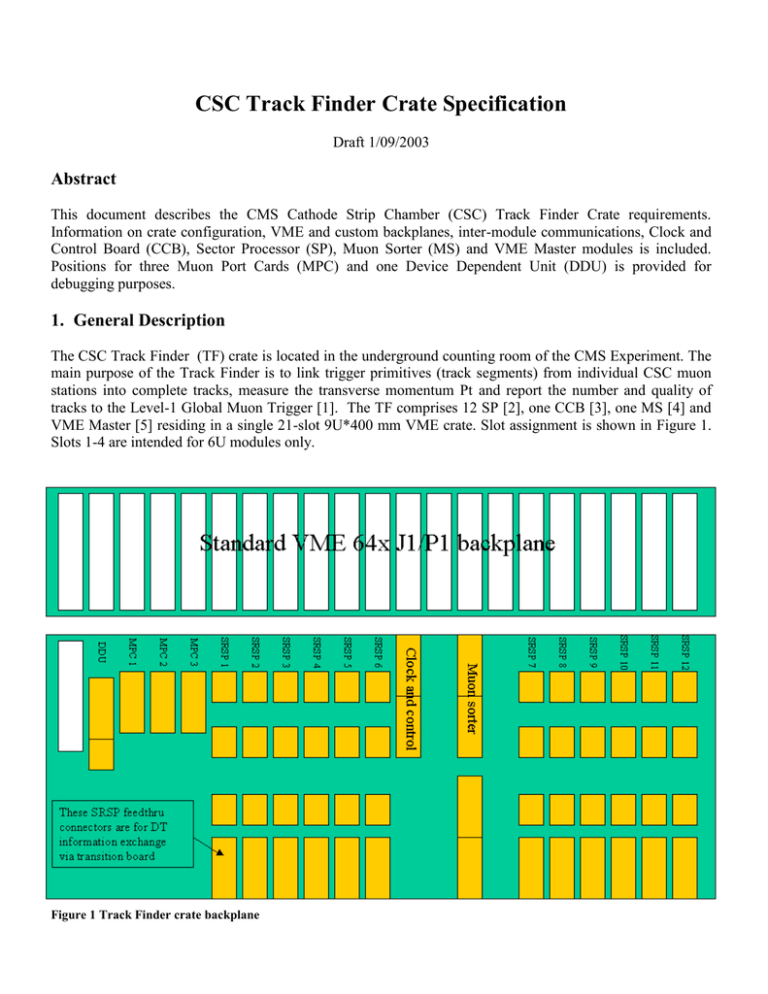

CSC Track Finder Crate Specification Draft 1/09/2003 Abstract This document describes the CMS Cathode Strip Chamber (CSC) Track Finder Crate requirements. Information on crate configuration, VME and custom backplanes, inter-module communications, Clock and Control Board (CCB), Sector Processor (SP), Muon Sorter (MS) and VME Master modules is included. Positions for three Muon Port Cards (MPC) and one Device Dependent Unit (DDU) is provided for debugging purposes. 1. General Description The CSC Track Finder (TF) crate is located in the underground counting room of the CMS Experiment. The main purpose of the Track Finder is to link trigger primitives (track segments) from individual CSC muon stations into complete tracks, measure the transverse momentum Pt and report the number and quality of tracks to the Level-1 Global Muon Trigger [1]. The TF comprises 12 SP [2], one CCB [3], one MS [4] and VME Master [5] residing in a single 21-slot 9U*400 mm VME crate. Slot assignment is shown in Figure 1. Slots 1-4 are intended for 6U modules only. Figure 1 Track Finder crate backplane VME Master performs an overall control, monitoring and testing of the TF modules over VME bus. VME bus is based on J1-only version of the VME64x backplane, which utilizes 160-pin 5-row connectors. Backplane connector is Harting 02-02-160-2201 female type. PCB connector is Harting 02-01-160-2101 male right angle. All communications between TF modules are performed over custom backplane, which will be located below J1 VME backplane. Custom backplane connectors are AMP 2-mm Z-pack male type and PCB connectors are matching female right angle ones. The number of connectors per slot and number of pins per connector vary from module to module and will be described below. 2. Clock and Control Board The Clock and Control Board distributes the system clock and other signals common to all TF modules. These signals are listed in Table 1. Timing parameters correspond to a timing of the TTCrx ASIC [6]. Table 1 CCB Signal Summary Signal Bits Source TTCrx2, FP3,Xtal QPLL on CCB VME4, FP Total 17 3 1 18 Total 6 1 1 1 1 1 8 1 4 1 25 ccb_clock401 ccb_clock80 ccb_clock40_enable ccb_cmd[5..0] ccb_evcntres ccb_bcntres ccb_cmd_strobe ccb_bx0 ccb_l1accept ccb_data[7..0] ccb_data_strobe ccb_reserved[3:0] ccb_ready 6 sp_hard_reset sp_cfg_done[12..1] ms_hard_reset ms_cfg_done mpc_hard_reset Mpc_cfg_done[3:1] Ddu_cfg_done Total Ms_l1a_req Sp_l1a_req Total Ms_to_ccb[1..0] Sp_to_ccb[2..0] Ccb_to_ms[2:0] Total 1 1 12 1 1 1 3 1 20 1 1 2 2 3 3 8 Destination Type Logic Duration Point-to-point Point-to-point Bussed LVDS LVDS GTLP 40 MHz 80 MHz Pulse, n counts Bussed Bussed Bussed Bussed Bussed Bussed Bussed Bussed Bussed Bussed GTLP GTLP GTLP GTLP GTLP GTLP GTLP GTLP GTLP GTLP Level 25ns 25ns 25ns 25ns+ECL FP 25ns+ECL FP Level 25ns Bussed Point-to-Point Point-to-Point Point-to-Point Bussed Point-to-Point Point-to-Point GTLP GTLP GTLP GTLP GTLP GTLP GTLP 400ns Level 400ns Level 400ns Level Level MS SP L1A request lines CCB CCB Bussed 7 Bussed GTLP GTLP 25 ns 25 ns MS SP CCB Reserved Lines CCB CCB MS Bussed 7 Bussed Point-to-Point GTLP GTLP GTLP 25 ns 25 ns 25 ns Clock Bus All 17 Slots MPC1,2,3 All 17 Slots Fast Control Bus TTCrx, VME All 17 Slots TTCrx, VME All 17 Slots TTCrx, VME All 17 Slots TTCrx, VME All 17 Slots dTTCrx5, VME, FP All 17 Slots TTCrx, VME, FP All 17 Slots TTCrx, VME All 17 Slots TTCrx, VME All 17 Slots VME All 17 Slots TTCrx All 17 slots Reload Bus dTTCrx, VME 12 SP 12 SP VME dTTCrx, VME MS MS VME dTTCrx, VME 3 MPC+DDU 3 MPC VME DDU VME Static level Clock: CCB distributes Clock40Des1 from the TTCrx or a crystal or FP, de-skewed separately for each slot. TTCrx: Signals derived unaltered by the CCB from the TTCrx chip 3 FP: Signals input or output via CCB Front Panel (ECL levels) 4 VME: Signals read or written via the CCB VME interface 5 dTTCrx: Signals decoded by CCB from TTCrx Brcst[7..2] 6 hard_reset: CCB decodes separate TTC commands for sp_hard_reset, ms_hard_reset. The TTC command "hard_reset" pulses all hard resets simultaneously. 7 This signal is actually point-to-point, but there is a termination for it on the backplane to provide compatibility with peripheral CCB 2 2.1 CCB Signal Description 2.1.1 Clock Bus Ccb_clock40 – System 40.08Mhz clock. Derived from TTCrx signal Clock40Des1. The clock source can be either Clock40Des1 or an on-board crystal (80.16Mhz divided by 2 for symmetry). Ccb_clock80 – 80.16Mhz clock. Derived from TTCrx signal Clock40Des1 by doubling its frequency in QPLL. Ccb_clock40_enable - Enables ccb_clock40 in SP and MS to single-step synchronous logic for debugging. 2.1.2 Fast Control Bus Ccb_cmd[5..0] – TTC broadcast commands. Commands are binary encoded according to Table 2. Extracted from TTCrx Brcst[7..2] lines. Table 2 Fast Control Bus Ccb_cmd[5..0] Decoding Scheme Signal BX0 L1 Reset Hard_reset SP_hard_reset MS_hard_reset MPC_hard_reset Code (hex) 1 3 4 1C 1D ??? Description Bunch Crossing Zero Reload all FPGAs at MS and SP’s from their EPROM’s Reload SP FPGAs from EPROM Reload MS FPGAs from EPROM Reload MPC FPGAs from EPROM Ccb_evcntres – Event Counter Reset. TTC broadcast command, predefined to be Brcst[1]. Event Counter Reset clears the Event Counters contained in each VME module (if any) that increment on Level 1 Accept. Ccb_bcntres – Bunch Counter Reset. TTC broadcast command, pre-defined to be Brcst[0]. Bunch Counter Reset sets the Bunch Counters (that increment on ccb_clock40) in each VME module to a predefined state. Ccb_cmd_strobe – indicates ccb_cmd[5..0], ccb_evcntres, ccb_bx0, ccb_bcntres and ccb_l1accept are valid on the rising edge of ccb_clock40. Ccb_bx0 – Bunch Crossing Zero. Decoded by CCB from Brcst[7..2], it allows Bunch Counters to start counting on the next ccb_clock40 tick. Ccb_l1accept – L1 Accept derived from TTCrx. Ccb_data[7..0] – individually addressed command. Extracted by CCB from Dout[7..0] Ccb_data_strobe – indicates that ccb_data[7..0] are valid on the rising edge of ccb_clock40. Ccb_reserved[3:0] – bussed signals from CCB to all modules reserved for future use. Ccb_ready – static signal indicating that TTCrx chip is working properly. 2.1.3. Reload Bus MS_hard_reset – 400 ns pulse that reloads all FPGA logic from EPROM on MS board. SP_hard_reset – 400 ns pulse that reloads datapath FPGA logic from EPROM on SP boards. MS_cfg_done – FPGA “configuration done” success signal from MS logic. SP_cfg_done – FPGA “configuration done” success signal from all SP boards. MPC_hard_reset -- 400 ns pulse that reloads all FPGA logic from EPROM on MPC and DDU boards. MPC_cfg_done -- FPGA “configuration done” success signal from MPC logic. DDU_cfg_done -- FPGA “configuration done” success signal from DDU logic. 2.1.4. L1A request bus Ms_l1a_req – L1A request from MS SP_l1a_req – L1A request from SP The CCB pin assignment is shown on Figure 3. It is designed to be compatible with the pin assignment of the Peripheral crate CCB, so the same board can be used. All connectors used on the MS board are AMP 100145-1 parts (female 25 rows by 5 pins). 3. Sector Processor For the list of signals delivered from Sector processor to Muon Sorter, see Error! Reference source not found. in Muon Sorter Section. For the list of signals in the control bus from CCB see Table 1 in CCB section. For the list of signals delivered from the Sector Receiver to the DT Track-Finder through a transition board behind the backplane, and from the DT Track-Finder to the Sector Processor through a transition board behind the backplane, see CMS IN 2002/040 Specification of the Interface Between the DT and CSC Level1 Track-Finders SP pin assignment is shown on Figure 2. Connectors used on SP board are AMP 100145-1 (125 pins) and 100161-1 (55 pins). 4. Muon Sorter Muon Sorter will be receiving 80MHz data streams from 12 SP. Connection to every SP comprises 32 pointto-point backplane lines. Data that is sent over these lines every 25 ns represents three best muon segments constructed by SP (see SP02 to MS Data Format document). MS selects four best patterns out of 36 possible and transmits them to Global Muon Trigger crate over four parallel LVDS cables. Pin assignment of the custom backplane connectors X1-X4 on MS slot is given in Figure 4 and Figure 5. All connectors used on the MS board are AMP 100145-1 parts (female 25 rows by 5 pins). 5. VME Master TBA 6. 7. Custom Backplane Electrical and Mechanical Interfaces. The guiding pins will be implemented on the backplane-strengthening bars. The corresponding guiding modules will be shown on the mechanical drawings (AMP partnumber 223957-1). These modules are used also for keying the boards. All bussed signals must NOT be terminated on daughter boards, the tracks from the connector to GTLP transceivers should be done as short as possible. All 40 MHz point-to-point signals must be terminated on receiving boards: 100 OHM to 1.5 V for GTLP, 100 OHM between the complementary signals for LVDS (clock), as close to the receiver as possible. All 80 MHz signals must be terminated on receiving boards: 50 OHM to 1.5 V for GTLP, as close to the receiver as possible. 1.5 V power from the backplane is provided for GTLP termination. The board designer should provide bypassing for it. MS is powered from two regulators, so there are two 1.5V inputs. The load must be distributed so that each of the regulators provides exactly one half of the total power necessary to terminate all GTLP signals (1.5V and 1.5V_1 nets on Figure 4 and Figure 5). All GTLP signals are sent in negative (active “low”) logic. SP-to-DT feed-thru connectors’ pin assignment is not defined, all pins are left unconnected on the backplane, except for ground and 3.3V power. VME Interface All TF modules in the crate are A24D16 slaves. They will use 5-bit geographical addressing to partition the available 24-bit address space. This leaves 19 bits of address space for use within each module. Pin assignment of the VME64x J1/P1 connector is given in Table 3. Table 3 VME64x J1/P1 connector Pin 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 Row Z MRP GND MCLK GND MSD GND MMD GND MCTL GND RESP* GND RsvBus1 GND RsvBus2 GND RsvBus3 GND RsvBus4 GND RsvBus5 GND RsvBus6 GND RsvBus7 GND RsvBus8 GND RsvBus9 GND RsvBus10 GND Row A D00 D01 D02 D03 D04 D05 D06 D07 GND SYSCLK GND DS1* DS0* WRITE* GND DTACK* GND AS* GND IACK* IACKIN* IACKOUT* AM4 A07 A06 A05 A04 A03 A02 A01 -12V +5V Row B BBSY* BCLR* ACFAIL* BG0IN* BG0OUT* BG1IN* BG1OUT* BG2IN* BG2OUT* BG3IN* BG3OUT* BR0* BR1* BR2* BR3* AM0 AM1 AM2 AM3 GND SERCLK SERDAT GND IRQ7* IRQ6* IRQ5* IRQ4* IRQ3* IRQ2* IRQ1* +5VSTDBY +5V Row C D08 D09 D10 D11 D12 D13 D14 D15 GND SYSFAIL* BERR* SYSRESET* LWORD* AM5 A23 A22 A21 A20 A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A09 A08 +12V +5V Row D VPC GND +V1 +V2 RsvU -V1 -V2 RsvU GAP* GA0* GA1* +3.3V GA2* +3.3V GA3* +3.3V GA4* +3.3V RsvBus11 +3.3V RsvBus12 +3.3V RsvBus13 +3.3V RsvBus14 +3.3V LI/I* +3.3V LI/O* +3.3V GND VPC References [1]. The Track-Finding Processor for the Level-1 Trigger of the CMS Endcap Muon System. CMS IN 1999/060. Available at: ftp://cmsdoc.cern.ch/documents/99/note99_060.pdf [2]. Merged Sector Receiver/Sector Processor Design Specification. Available at: http://www.phys.ufl.edu/~acosta/cms/srsp_spec.doc [3]. Clock and Control Board for the Track Finder Crate Specification. [4]. Muon Sorter Specification. [5]. VME Master Specification. [6]. TTCrx Reference Manual. February 2001. Version 3.2. Available at: http://ttc.web.cern.ch/TTC/intro.html [7] CMS IN 2002/040 Specification of the Interface Between the DT and CSC Level-1 Track-Finders [8] SP02 to MS Data Format document History 09/24/2001: Changes in Table 3. One more line is added for communication between MS and each SP. 12/17/2001: Multiple changes in all sections. Pin assignment for all modules added. 12/06/2002: Additions and fixes after the backplane is routed. This version is to be discussed. 1/9/2003: Multiple corrections suggested by Lev Uvarov 08/23/2004: 80 MHz clock for MPC positions added (A.Madorsky) Appendix A: Pin assignments for the daughter boards. Pin assignment for the boards in the Track Finder crate Pin assignment for Sector Processor is shown on Figure 2, for CCB on Figure 3, for Muon sorter on Figure 4 and Figure 5. Zpack125 on schematics is AMP part number 100145-1 (female 25 rows by 5 pins). Zpack55 on schematics is AMP part number 100161-1 (female 11 rows by 5 pins). Mechanical drawings for connector placement are available here: http://www.phys.ufl.edu/~madorsky/TrackFinder/ms.dxf http://www.phys.ufl.edu/~madorsky/backplane/ccb.dxf X27A X27B 1 2 3 4 5 6 7 8 9 10 11 A1 A2 A3 A4 A5 A6 A7 A8 A9 A 10 A 11 CLK+ Clock_Enable ccb_cmd0 ccb_cmd4 ccb_cmd_strobe ccb_data0 ccb_data4 ccb_r eady sp_to_ccb0 ZPack55 X28A 1 2 3 4 5 6 7 8 9 10 11 A1 A2 A3 A4 A5 A6 A7 A8 A9 A 10 A 11 X27C 1 2 3 4 5 6 7 8 9 10 11 CLKccb_r eserved4 ccb_cmd1 ccb_cmd5 ccb_bx0 ccb_data1 ccb_data5 ccb_r eserved1 sp_to_ccb1 1 2 3 4 5 6 7 8 9 10 11 ZPack55 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 1 2 3 4 5 6 7 8 9 10 11 w _1 sp_1 sp_5 sp_9 sp_13 sp_17 sp_22 sp_27 ZPack55 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 ZPack125 A1 A2 A3 A4 A5 A6 A7 A8 A9 A 10 A 11 A 12 A 13 A 14 A 15 A 16 A 17 A 18 A 19 A 20 A 21 A 22 A 23 A 24 A 25 ZPack55 3.3V ZPack125 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15 B16 B17 B18 B19 B20 B21 B22 B23 B24 B25 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 3.3V 1 2 3 4 5 6 7 8 9 10 11 sp_2 sp_6 sp_10 sp_14 sp_19 sp_24 sp_29 1 2 3 4 5 6 7 8 9 10 11 ZPack125 E1 E2 E3 E4 E5 E6 E7 E8 E9 E10 E11 1 2 3 4 5 6 7 8 9 10 11 E1 E2 E3 E4 E5 E6 E7 E8 E9 E10 E11 ZPack55 X29E 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZPack125 Figure 2 SP pin assignment sp_3 sp_7 sp_11 sp_15 sp_20 sp_25 sp_30 ZPack55 ZPack55 3.3V ccb_cmd3 ccb_bcntres ccb_data_strobe ccb_data3 ccb_data7 ccb_r eserved3 sp_l1a_req X30E X29D C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 C18 C19 C20 C21 C22 C23 C24 C25 sp_har d_reset ZPack55 X28E D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 ZPack55 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 E1 E2 E3 E4 E5 E6 E7 E8 E9 E10 E11 ZPack55 X29C 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 1 2 3 4 5 6 7 8 9 10 11 1 2 3 4 5 6 7 8 9 10 11 ccb_cmd2 ccb_evcntres ccb_l1accept ccb_data2 ccb_data6 ccb_r eserved2 sp_to_ccb2 ZPack55 X28D sp_31 sp_18 sp_23 sp_28 sp_cf g_done X30D 1 2 3 4 5 6 7 8 9 10 11 X29B 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 1 2 3 4 5 6 7 8 9 10 11 X30C 1 2 3 4 5 6 7 8 9 10 11 X29A C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 X27E D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 ZPack55 X30B A1 A2 A3 A4 A5 A6 A7 A8 A9 A 10 A 11 C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 ZPack55 X28C ZPack55 X30A 1 2 3 4 5 6 7 8 9 10 11 X27D 1 2 3 4 5 6 7 8 9 10 11 1.5V ZPack55 X28B w _0 sp_0 sp_4 sp_8 sp_12 sp_16 sp_21 sp_26 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D24 D25 3.3V 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZPack125 E1 E2 E3 E4 E5 E6 E7 E8 E9 E10 E11 E12 E13 E14 E15 E16 E17 E18 E19 E20 E21 E22 E23 E24 E25 3.3V X 5A X 5B 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 A1 A2 A3 A4 A5 A6 A7 A8 A9 A 10 A 11 A 12 A 13 A 14 A 15 A 16 A 17 A 18 A 19 A 20 A 21 A 22 A 23 A 24 A 25 CLK +DDU CLK +MP C1 CLK +MP C2 CLK +MP C3 CLK +SP 1 CLK +SP 2 CLK +SP 3 CLK +SP 4 CLK +SP 5 CLK +SP 6 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 dd u_cfg_ don e mpc _cfg_d one _2 sp _cfg_d one _1 sp _cfg_d one _3 sp _cfg_d one _5 Clo ck_E nab le cc b_cmd 0 cc b_cmd 4 cc b_cmd _strobe cc b_da ta 0 cc b_da ta 4 cc b_read y ZP ack1 25 X 5C B1 B2 B3 B4 B5 B6 B7 B8 B9 B 10 B 11 B 12 B 13 B 14 B 15 B 16 B 17 B 18 B 19 B 20 B 21 B 22 B 23 B 24 B 25 CLK -DDU CLK -MPC1 CLK -MPC2 CLK -MPC3 CLK -S P1 CLK -S P2 CLK -S P3 CLK -S P4 CLK -S P5 CLK -S P6 X 6A cc b_rese rve d4 cc b_cmd 1 cc b_cmd 5 cc b_bx0 cc b_da ta 1 cc b_da ta 5 cc b_rese rve d1 ZP ack1 25 X 6B 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ack1 25 A1 A2 A3 A4 A5 A6 A7 A8 A9 A 10 A 11 A 12 A 13 A 14 A 15 A 16 A 17 A 18 A 19 A 20 A 21 A 22 A 23 A 24 A 25 sp _hard_ re set ms_ to_ ccb 0 mpc _hard_ re set cc b_to_ms 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 mpc _cfg_d one _1 mpc _cfg_d one _3 sp _cfg_d one _2 sp _cfg_d one _4 sp _cfg_d one _6 ZP ack1 25 X 5D C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 C18 C19 C20 C21 C22 C23 C24 C25 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ack1 25 ms_ hard_res et ms_ to_ ccb 1 cc b_to_ms 1 sp _to_cc b0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 CLK 80+MP C1 CLK 80+MP C2 CLK 80+MP C3 cc b_cmd 2 cc b_evc ntre s cc b_l 1ac cep t cc b_da ta 2 cc b_da ta 6 cc b_rese rve d2 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 1.5V ZP ack1 25 Figure 3 CCB pin assignment E1 E2 E3 E4 E5 E6 E7 E8 E9 E 10 E 11 E 12 E 13 E 14 E 15 E 16 E 17 E 18 E 19 E 20 E 21 E 22 E 23 E 24 E 25 CLK -S P1 2 CLK -S P1 1 CLK -S P1 0 CLK -S P9 CLK -S P8 CLK -S P7 CLK -MS sp _cfg_d one _12 sp _cfg_d one _11 sp _cfg_d one _10 sp _cfg_d one _9 sp _cfg_d one _8 sp _cfg_d one _7 ms_ cfg _do ne CLK 80-MP C1 CLK 80-MP C2 CLK 80-MP C3 cc b_cmd 3 cc b_bc ntre s cc b_da ta _strobe cc b_da ta 3 cc b_da ta 7 cc b_rese rve d3 ZP ack1 25 X 6D C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 C18 C19 C20 C21 C22 C23 C24 C25 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 CLK +SP 12 CLK +SP 11 CLK +SP 10 CLK +SP 9 CLK +SP 8 CLK +SP 7 CLK +MS ZP ack1 25 X 6C B1 B2 B3 B4 B5 B6 B7 B8 B9 B 10 B 11 B 12 B 13 B 14 B 15 B 16 B 17 B 18 B 19 B 20 B 21 B 22 B 23 B 24 B 25 X 5E D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D24 D25 X 6E 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 D1 D2 D3 D4 D5 D6 D7 sp _l 1a_req D8 D9 D10 D11 D12 cc b_to_ms 2 D13 sp _to_cc b1 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D24 D25 ZP ack1 25 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ack1 25 E1 E2 E3 E4 E5 E6 E 7 ms_ l1a _req E8 E9 E 10 E 11 E 12 cc b_to_ms 3 E 13 sp _to_cc b2 E 14 E 15 E 16 E 17 E 18 E 19 E 20 E 21 E 22 E 23 E 24 E 25 X 23A X 23B 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 A1 A2 A3 A4 A5 A6 A7 A8 A9 A 10 A 11 A 12 A 13 A 14 A 15 A 16 A 17 A 18 A 19 A 20 A 21 A 22 A 23 A 24 A 25 CLK +MS Clo ck_E nab le cc b_cmd 0 cc b_cmd 4 cc b_cmd _strobe cc b_da ta 0 cc b_da ta 4 cc b_to_ms 0 sp 1_2 sp 1_6 sp 1_10 sp 1_31 sp 1_18 sp 1_23 sp 1_28 sp 12_2 sp 12_6 sp 12_1 0 sp 12_1 4 sp 12_1 9 sp 12_2 4 sp 12_2 9 sp 3_2 sp 3_6 sp 3_10 ZP ac k1 25 X 24A 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ac k1 25 X 23C 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 B1 B2 B3 B4 B5 B6 B7 B8 B9 B 10 B 11 B 12 B 13 B 14 B 15 B 16 B 17 B 18 B 19 B 20 B 21 B 22 B 23 B 24 B 25 CLK -MS cc b_rese rve d4 cc b_cmd 1 cc b_cmd 5 cc b_bx0 cc b_da ta 1 cc b_da ta 5 cc b_to_ms 1 sp 1_3 sp 1_7 sp 1_11 sp 1_14 sp 1_19 sp 1_24 sp 1_29 sp 12_3 sp 12_7 sp 12_1 1 sp 12_1 5 sp 12_2 0 sp 12_2 5 sp 12_3 0 sp 3_3 sp 3_7 sp 3_11 ZP ac k1 25 X 24B A1 A2 A3 A4 A5 A6 A7 A8 A9 A 10 A 11 A 12 A 13 A 14 A 15 A 16 A 17 A 18 A 19 A 20 A 21 A 22 A 23 A 24 A 25 sp 3_31 sp 3_18 sp 3_23 sp 3_28 sp 10_2 sp 10_6 sp 10_1 0 sp 10_1 4 sp 10_1 9 sp 10_2 4 sp 10_2 9 sp 5_2 sp 5_6 sp 5_10 sp 5_31 sp 5_18 sp 5_23 sp 5_28 sp 8_2 sp 8_6 sp 8_10 sp 8_14 sp 8_19 sp 8_24 sp 8_29 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ac k1 25 X 23D 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 C18 C19 C20 C21 C22 C23 C24 C25 cc b_read y sp 1_15 sp 1_20 sp 1_25 sp 1_30 1.5V sp 12_1 2 sp 12_1 6 sp 12_2 1 sp 12_2 6 ZP ac k1 25 X 24C B1 B2 B3 B4 B5 B6 B7 B8 B9 B 10 B 11 B 12 B 13 B 14 B 15 B 16 B 17 B 18 B 19 B 20 B 21 B 22 B 23 B 24 B 25 sp 3_14 sp 3_19 sp 3_24 sp 3_29 sp 10_3 sp 10_7 sp 10_1 1 sp 10_1 5 sp 10_2 0 sp 10_2 5 sp 10_3 0 sp 5_3 sp 5_7 sp 5_11 sp 5_14 sp 5_19 sp 5_24 sp 5_29 sp 8_3 sp 8_7 sp 8_11 sp 8_15 sp 8_20 sp 8_25 sp 8_30 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ac k1 25 X 23E 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D24 D25 cc b_rese rve d1 cc b_rese rve d2 cc b_cmd 2 cc b_evc ntre s cc b_l 1ac cep t cc b_da ta 2 cc b_da ta 6 cc b_to_ms 2 sp 1_0 sp 1_4 sp 1_8 sp 1_12 sp 1_16 sp 1_21 sp 1_26 sp 12_0 sp 12_4 sp 12_8 sp 12_1 3 sp 12_1 7 sp 12_2 2 sp 12_2 7 sp 3_0 sp 3_4 sp 3_8 ZP ac k1 25 X 24D C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 C18 C19 C20 C21 C22 C23 C24 C25 sp 3_15 sp 3_20 sp 3_25 sp 3_30 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 1.5V sp 10_1 2 sp 10_1 6 sp 10_2 1 sp 10_2 6 sp 5_15 sp 5_20 sp 5_25 sp 5_30 1.5V sp 8_12 sp 8_16 sp 8_21 sp 8_26 ZP ac k1 25 Figure 4 MS J2/P2 area pin assignment 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 E1 E2 E3 E4 E5 E6 E7 E8 E9 E 10 E 11 E 12 E 13 E 14 E 15 E 16 E 17 E 18 E 19 E 20 E 21 E 22 E 23 E 24 E 25 ms_ hard_res et cc b_rese rve d3 cc b_cmd 3 cc b_bc ntre s cc b_da ta _strobe cc b_da ta 3 cc b_da ta 7 cc b_to_ms 3 sp 1_1 sp 1_5 sp 1_9 sp 1_13 sp 1_17 sp 1_22 sp 1_27 sp 12_1 sp 12_5 sp 12_9 sp 12_3 1 sp 12_1 8 sp 12_2 3 sp 12_2 8 sp 3_1 sp 3_5 sp 3_9 E1 E2 E3 E4 E5 E6 E7 E8 E9 E 10 E 11 E 12 E 13 E 14 E 15 E 16 E 17 E 18 E 19 E 20 E 21 E 22 E 23 E 24 E 25 sp 3_13 sp 3_17 sp 3_22 sp 3_27 sp 10_1 sp 10_5 sp 10_9 sp 10_3 1 sp 10_1 8 sp 10_2 3 sp 10_2 8 sp 5_1 sp 5_5 sp 5_9 sp 5_13 sp 5_17 sp 5_22 sp 5_27 sp 8_1 sp 8_5 sp 8_9 sp 8_31 sp 8_18 sp 8_23 sp 8_28 ZP ac k1 25 X 24E D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D24 D25 sp 3_12 sp 3_16 sp 3_21 sp 3_26 sp 10_0 sp 10_4 sp 10_8 sp 10_1 3 sp 10_1 7 sp 10_2 2 sp 10_2 7 sp 5_0 sp 5_4 sp 5_8 sp 5_12 sp 5_16 sp 5_21 sp 5_26 sp 8_0 sp 8_4 sp 8_8 sp 8_13 sp 8_17 sp 8_22 sp 8_27 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ac k1 25 X 25A X 25B 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 A1 A2 A3 A4 A5 A6 A7 A8 A9 A 10 A 11 A 12 A 13 A 14 A 15 A 16 A 17 A 18 A 19 A 20 A 21 A 22 A 23 A 24 A 25 sp 6_2 sp 6_6 sp 6_10 sp 6_31 sp 6_18 sp 6_23 sp 6_28 sp 7_2 sp 7_6 sp 7_10 sp 7_14 sp 7_19 sp 7_24 sp 7_29 sp 4_2 sp 4_6 sp 4_10 sp 4_31 sp 4_18 sp 4_23 sp 4_28 sp 9_2 sp 9_6 sp 9_10 sp 9_14 ZP ac k1 25 X 26A 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ac k1 25 X 25C 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 B1 B2 B3 B4 B5 B6 B7 B8 B9 B 10 B 11 B 12 B 13 B 14 B 15 B 16 B 17 B 18 B 19 B 20 B 21 B 22 B 23 B 24 B 25 sp 6_3 sp 6_7 sp 6_11 sp 6_14 sp 6_19 sp 6_24 sp 6_29 sp 7_3 sp 7_7 sp 7_11 sp 7_15 sp 7_20 sp 7_25 sp 7_30 sp 4_3 sp 4_7 sp 4_11 sp 4_14 sp 4_19 sp 4_24 sp 4_29 sp 9_3 sp 9_7 sp 9_11 sp 9_15 ZP ac k1 25 X 26B A1 A2 A3 A4 A5 A6 A7 A8 A9 A 10 A 11 A 12 A 13 A 14 A 15 A 16 A 17 A 18 A 19 A 20 A 21 A 22 A 23 A 24 A 25 sp 9_19 sp 9_24 sp 9_29 sp 2_2 sp 2_6 sp 2_10 sp 2_31 sp 2_18 sp 2_23 sp 2_28 sp 11_2 sp 11_6 sp 11_1 0 sp 11_1 4 sp 11_1 9 sp 11_2 4 sp 11_2 9 ms_ to_ ccb 0 w6_0 w5_0 w4_0 w3_0 w2_0 w1_0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ac k1 25 X 25D 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 C18 C19 C20 C21 C22 C23 C24 C25 B1 B2 B3 B4 B5 B6 B7 B8 B9 B 10 B 11 B 12 B 13 B 14 B 15 B 16 B 17 B 18 B 19 B 20 B 21 B 22 B 23 B 24 B 25 sp 9_20 sp 9_25 sp 9_30 sp 2_3 sp 2_7 sp 2_11 sp 2_14 sp 2_19 sp 2_24 sp 2_29 sp 11_3 sp 11_7 sp 11_1 1 sp 11_1 5 sp 11_2 0 sp 11_2 5 sp 11_3 0 ms_ to_ ccb 1 w6_1 w5_1 w4_1 w3_1 w2_1 w1_1 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ac k1 25 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 sp 6_15 sp 6_20 sp 6_25 sp 6_30 1.5V _1 sp 7_12 sp 7_16 sp 7_21 sp 7_26 sp 4_15 sp 4_20 sp 4_25 sp 4_30 1.5V _1 sp 9_12 ZP ac k1 25 X 26C X 25E D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D24 D25 sp 6_0 sp 6_4 sp 6_8 sp 6_12 sp 6_16 sp 6_21 sp 6_26 sp 7_0 sp 7_4 sp 7_8 sp 7_13 sp 7_17 sp 7_22 sp 7_27 sp 4_0 sp 4_4 sp 4_8 sp 4_12 sp 4_16 sp 4_21 sp 4_26 sp 9_0 sp 9_4 sp 9_8 sp 9_13 ZP ac k1 25 X 26D C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 C18 C19 C20 C21 C22 C23 C24 C25 sp 9_16 sp 9_21 sp 9_26 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 sp 2_15 sp 2_20 sp 2_25 sp 2_30 1.5V _1 sp 11_1 2 sp 11_1 6 sp 11_2 1 sp 11_2 6 ZP ac k1 25 Figure 5 MS J3/P3 area pin assignment 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 E1 E2 E3 E4 E5 E6 E7 E8 E9 E 10 E 11 E 12 E 13 E 14 E 15 E 16 E 17 E 18 E 19 E 20 E 21 E 22 E 23 E 24 E 25 sp 6_1 sp 6_5 sp 6_9 sp 6_13 sp 6_17 sp 6_22 sp 6_27 sp 7_1 sp 7_5 sp 7_9 sp 7_31 sp 7_18 sp 7_23 sp 7_28 sp 4_1 sp 4_5 sp 4_9 sp 4_13 sp 4_17 sp 4_22 sp 4_27 sp 9_1 sp 9_5 sp 9_9 sp 9_31 E1 E2 E3 E4 E5 E6 E7 E8 E9 E 10 E 11 E 12 E 13 E 14 E 15 E 16 E 17 E 18 E 19 E 20 E 21 E 22 E 23 E 24 E 25 sp 9_18 sp 9_23 sp 9_28 sp 2_1 sp 2_5 sp 2_9 sp 2_13 sp 2_17 sp 2_22 sp 2_27 sp 11_1 sp 11_5 sp 11_9 sp 11_3 1 sp 11_1 8 sp 11_2 3 sp 11_2 8 ms_ cfg _do ne w7_1 w8_1 w9_1 w10_ 1 w11_ 1 w12_ 1 ZP ac k1 25 X 26E D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18 D19 D20 D21 D22 D23 D24 D25 sp 9_17 sp 9_22 sp 9_27 sp 2_0 sp 2_4 sp 2_8 sp 2_12 sp 2_16 sp 2_21 sp 2_26 sp 11_0 sp 11_4 sp 11_8 sp 11_1 3 sp 11_1 7 sp 11_2 2 sp 11_2 7 ms_ l1a _req w7_0 w8_0 w9_0 w10_ 0 w11_ 0 w12_ 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 ZP ac k1 25