TANet 新世代骨幹路由挑戰-

advertisement

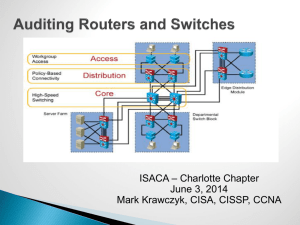

New Generation Backbone Router ~ A Longevous Solution Presented by: Furman Chang, Business Develop Department, Hauman E-Mail: furmanc@hauman.com.tw HAUMAN 豪 技 勉 科 The Old Generation Network From Humble Beginnings… HAUMAN 豪 技 勉 科 The New Generation Network From Humble Beginnings… The New Generation Network is Well Beyond Critical Mass! HAUMAN 豪 技 勉 科 Users & Applications Physical Pipes Why Talk About Backbone Routers? Application demand (any-any) Bandwidth Supply (point-point) HAUMAN 豪 技 勉 科 Users & Applications Backbone Routers Dominate the Intelligence of Internet Application demand (any-any) Routing Physical Pipes Maps ‘any-any’ demand to ‘point-point’ supply Bandwidth Supply (point-point) HAUMAN 豪 技 Legacy IP Routers 勉 科 Poor architecture Borrowed from embedded computer base Functionality incorrectly partitioned Fragile and unreliable (working at edge of performance) Configurations complex due to tradeoffs and limitations Monolithic, bloated software Designed for multiprotocol LAN connectivity Focus on bells and whistles, not on stability and performance Weak hardware base Microprocessors, jelly bean parts, FPGAs Inefficient for forwarding IP packets HAUMAN 豪 技 Routing Technology Revolution 勉 科 The New IP Infrastructure Scale Intelligence Performance Reliability Connectivity 1996 Today Time For details please access BTexact Thchnologies. http://www.btexact.com/docimages/42267/42267.pdf HAUMAN 豪 技 勉 科 So What Is a Backbone IP Router Certain minimum qualifications Capable of switching IP datagrams: Layer 3 forwarding Symmetric any-port-to-any-port switching speed Delay-bandwidth buffering, plus congestion control Internet scale IS-IS, OSPF, MPLS, BGP4 Today’s benchmark Wire-rate forwarding on all ports Performance independent of load Support of class-of-service (CoS) queuing, shaping, and policing Traffic engineering Classification and filtering at wire rate What a Backbone Router Looks Like? HAUMAN 豪 技 勉 科 Cisco GSR 12416 Juniper T640 19” 19” Capacity: 640Gb/s Capacity: 320Gb/s 6ft 3ft 2.5ft 2ft HAUMAN 豪 技 勉 科 Why Are They so Hard to Build? Bottom line: inherent complexity Scaling along multiple dimensions Bandwidth, packets per second # interfaces, # channels, # routes, # neighbors, # policies, #filters Unpredictable, demanding environment Need for reliable, seamless interoperability Deep technical expertise across multiple Software: routing protocols, embedded systems, network management Hardware: ASIC design, board design, high-speed circuit design Mechanical: power, packaging, thermal, emissions Changing requirements Building Internet routers requires a special viewpoint The network is the system, not the box Internet routers uniquely integrate the network at scale Building A Provider Business: Standard Services HAUMAN 豪 技 勉 科 Service Deployment Market Readiness Standard Service Portfolio Services TANet.edu.tw STANDARD SERVICES Network Access IP Transport Concept IP Routing Operating System Access Access Edge Edge IP IP Core Core Building A Provider Business : Smart IP Services HAUMAN 豪 技 勉 科 Service Deployment Market Readiness Smart IP Services Standard Services Service Provider.com STANDARD SERVICES Network Access IP Transport Concept Enriched IP Toolkit IP Routing Operating System Access Edge Edge IP Core IP Service Market Readiness Challenges the Old IP Infrastructure HAUMAN 豪 技 勉 科 Service Deployment Deployability Deficit Market Readiness Smart IP Services Concept Enriched IP Toolkit IP Routing Operating System Access Edge Edge IP Core Service activation dramatically impacts performance Insufficient feature scalability Prohibitive operational complexity Inability to bill Smart IP Services : A Longevous Solution HAUMAN 勉 科 Market Readiness t Concept Accounting CoS/QoS Layer 2/3 MPLS Multicasting Smart IP Services IPv6 豪 技 Single Operation System Enriched IP Toolkit IP Routing Operating System Access For Edge All Network IP Core Interfaces For All Routing Platforms HAUMAN 豪 技 Agenda 勉 科 Router Architecture and Technologies Major Router Functionalities Major Hardware of Routers Major Components of Routers The Evolution of Router Architecture Case Study – A Juniper Networks Example Architecture Overview Routing Engine Forwarding Engine Hardware & Architecture Flexibility Router’s Position : Late 1980 ~ Early 1990 HAUMAN 豪 技 勉 科 IP SNA DECnet IPX IPX DECnet SNA IP To interconnect different types of LAN technologies in a multiprotocol enterprise environment. Router’s Position : Mid 1990 HAUMAN 豪 技 勉 科 Ethernet ATM FDDI Token Ring Token Ring FDDI ATM Ethernet Switch When You Can, Route When You Must! Router’s Position : IP Service Aggregation Core HAUMAN 豪 技 勉 科 Separate Networks (IP) (Broadband) (ATM/FR) (Circuit) The TheNew NewIPIP Infrastructure Infrastructure Major Functionalities of Internet Routers HAUMAN 豪 技 勉 科 Route Processing IPv4 Header Routing Table construction / maintenance / update using routing protocol. Packet Forwarding Packet Validation Destination Address Parsing and Table Lookup Packet Lifetime Control Checksum Calculation Queuing & Scheduling (CoS/QoS) Special Service:Packet Translation, Encapsulation, Authentication, Filtering… IPv6 Header Control Plane Processing Communicating with the rest of the system (Powers, Fans…) Management protocols( SNMP, RMON, SMON) Other Admission control MPLS Header HAUMAN 豪 技 勉 科 Router Architecture and Technologies Major Router Functionalities Major Hardware of Routers Off-the-shelf Components Memory Processors Major Components of Routers The Evolution of Router Architecture Case Study – A Juniper Networks Example Architecture Overview Routing Engine Forwarding Engine Hardware & Architecture Flexibility HAUMAN 豪 技 Why We Need Faster Router? 勉 科 To prevent routers from being the bottleneck 100,000% DWDM Link speed x2/8 months 10,000% Internet Traffic x2/1 yr Router capacity x2.2/18 m Moore’s law x2/18 m 1,000% DRAM access rate x1.1/18 m 100% 1996 1998 Source: SPEC95Int & David Miller, Stanford. 2000 2002 HAUMAN 豪 技 勉 科 Why are Fast Routers Difficult to Make? Access Time (ns) Speed of Commercial DRAM Commercial DRAM x1.1/18 m Moore’s law x2/18 m DWDM Link speed x2/8 months Source: Nick McKeown, Stanford. Router capacity x2.2/18 m HAUMAN 豪 技 Major Hardware of Routers 勉 科 Processors ASIC NPU FPGA CPU … Transceiver Cell buffer Scheduler + FQ Memory DRAM/SDRAM SRAM … Framer Network processor Off-the-shelf Components (Can buy from other vendors) CPU Transceiver MAC Chips (Ethernet and ATM SAR) SONET Framer … Routing table Major Hardware of Routers : Processors HAUMAN 豪 技 勉 科 Software-based Router Hardware-based Router Common Processor Routing Forwarding Topology Forwarding Services Services Routing Major Hardware of Routers : Processors HAUMAN 豪 技 勉 科 ASIC (Application Specific Integrated Circuit)--特殊應用積體電路 純硬體接線的解決方案,程式碼以Hard-Code方式固定燒錄在晶片上 如電子計算機晶片 ASIP (Application Specific Instruction Processor)--特殊應用指令處理器 專為特殊應用開發的指令集處理器 網路處理器(Network Processing Unit, NPU):專為網路封包處理而開發的ASIP, 常使用多個精簡指令集處理器(RISC)做平行處理,以加快處理效能 Co-processor--協同處理器 硬體接線的解決方案,具備有限的編程介面做功能設定 如浮點運算器 FPGA (Field Programmable Gate Array)--現場可編程閘陣列 一種可透過閘道重新編程的裝置 通常應用於硬體平台開發的實驗階段 GPP (General Purpose Processor)--通用處理器 可針對一般用途計算的可程式化處理器 如Intel/AMD CISC CPU, PowerPC/MIPS/SPARC RISC CPU HAUMAN 豪 技 勉 科 Major Hardware of Routers : Processor decision considerations Source: Niraj Shah, Understand Network PRocessor A Compromise Solution Between Performance and Flexibility HAUMAN 豪 技 勉 科 Packet Forwarding Engine Physical Layer Forwarding Engine Fabric Interface Memory ASIC To Fabric Switch Fabric CPU Memory ASIC From Fabric Scheduler Fast Path Slow Path Major Hardware of Routers : NPU Architecture Example HAUMAN 豪 技 勉 科 RISC-based NPU VLIW-Based NPU Source: Simon Stanley, Network Processors HAUMAN 豪 技 勉 科 Major Hardware of Routers : Various NPU Solutions Major Hardware of Routers : Memory HAUMAN 豪 技 勉 科 DRAM (Dynamic RAM ) SRAM (Static RAM ) 特色 存取速度:慢(>60ns,ns=10-9) 記憶容量:大 組成 每個位元只使用1個電晶體,且該電晶 體需要週期性的電源補充,以確保資料 不會流失。其優點是省空間與低消耗功 率,因為必須不斷充電,所以總是佔用 系統一部份的時間,因此降低系統效率。 用途 通常應用於「主記憶體」,儲存正在使 用中的程式和資料。 PS. SDRAM為同步DRAM,速度較 DRAM快,常做為路由交換器的Packet Buffer Memory。 特色 存取速度:快(4~10ns) 記憶容量:小 組成 每個位元使用6個電晶體組成正反器 (flip-flop)來保有資料,也因此不需要 週期性的電源補充,所以 SRAM 的速 度較快,但價格也較高。 用途 通常介於CPU和DRAM之間,做為外部 快取記憶體之用(如L2 cache),可暫時 儲存 經常存取的DRAM資料,使CPU的 執行速度更快。 說明 採用0.13μm CMOS技術,最大只能製 造出16MB的SRAM,若用其儲存0.25秒 的資料,則最高只能支援100Mb/s的頻 寬。 HAUMAN 豪 技 Memory Hierarchy 勉 科 Processor Control Registers Datapath On-Chip Cache Second Level Cache (SRAM) Third Level Cache (SRAM) Main Memory (DRAM) Secondary Storage (Disk) Tertiary Storage (Tape) HAUMAN 豪 技 An Example: Packet buffers 勉 科 40Gb/s router linecard 10Gbits Buffer Buffer Buffer Buffer Memory Memory Memory Memory Write Rate, R One 40B packet every 8ns Buffer Manager Read Rate, R One 40B packet every 8ns Use SRAM? + Fast enough random access time, but - Too low density to store 10Gbits of data. Use DRAM? + High density means we can store data, but -Can’t meet random access time. HAUMAN 豪 技 勉 科 Router Architecture and Technologies Major Router Functionalities Major Hardware of Routers Major Components of Routers Input/Output Ports Processor Switch Fabric The Evolution of Router Architecture Case Study – A Juniper Networks Example Architecture Overview Routing Engine Forwarding Engine Hardware & Architecture Flexibility HAUMAN 豪 技 勉 科 Major Components of Routers Network/Routing Processor Switch Fabric Input Ports Output Ports Major Components of Routers : Input/Output Ports HAUMAN 豪 技 勉 科 Input Port From Fabric Layer 1 Func: Line Termination Layer 2 Func: Protocol Decapsulation Lookup/ Forwarding/ Queuing Buffer Management /Queuing Layer 2 Func: Protocol Encapsulation Layer 1 Func: Line Termination Layer 1 Function : Line Termination Layer 2 Function Input Port : Data-Link Protocol Decapsulation Output Port : Data-Link Protocol Encapsulation Other Packet Process Input Port : Local Lookup/Forwarding/Queuing Output Port :Buffer Management / Queuing To Fabric Output Port Major Components of Routers : Processor HAUMAN 豪 技 勉 科 Processor Major Processor Tasks Maintain Routing Table Packet Processing Routing Table Maintenance Decapsulation/Encapsulation (Header Rewrite) Buffer Management Classification Forwarding Lookup QoS Management Forwarding Lookup Packet Classify QoS Management Buffer Management Others Accounting (Log, Sampling…) Network Management (SNMP, MIB) Decapsulation Encapsulation INPUT Switch Fabric OUTPUT Major Components of Routers : Processor Kernels HAUMAN 豪 技 勉 科 Pattern Matching Matching bits in packet fields (header/payload) Inputs : Regular expression pattern & packet field Outputs : A Boolean value Lookup Looking up data based on a key, mostly used in conjunction with pattern matching to find a specific entry in a table. Lookup type Exact Match (One-to-one) : ATM, MPLS Longest Prefix Match (Many-to-one) : IPv4, IPv6 Computation The type of computation required for packet processing vary widely Ex. IPSec, Encryption, Decryption, Authentication, checksum, CRC value Data Manipulation Any function that modifies a packet header Ex. TTL decrement, adding tags/ header fields, replacing fields, segmentation, reassembly, fragmentation Queue Management The Scheduling and storage of ingress and egress packets Control Processing Consists of a number of different tasks that don’t need to be performed at wire speed Ex. Exceptions, table update, statistics gathering… Major Components of Routers : Processor Kernels HAUMAN 豪 技 勉 科 Processor Kernels with Different Protocols ATM Switching VLAN IPv4 Routing IPv6 MPLS Pattern Matching VCI(8 bits) VPI(16bits) MAC address(48bits) IP subnet(8-24bits) Version & address check IP address (128bits) MPLS Label (20bits) Lookup VCI(8 bits) VPI(16bits) MAC address(48bits) IP subnet(8-24bits) IP address (32bits) IP address (128bits); Flow label (20bits) MPLS Label (20bits) Checksum Checksum Insert unique ID in VLAN field; Checksum Insert next hop; TTL decrement; Checksum TTL adjustment Incoming packet management, to implement CoS/QoS Incoming packet management, based on flow label for QoS Computation Data Manipulation TTL adjustment; Update VCI/VPI Queue Management Incoming cell management Control Processing VCI/VPI table update; Path/circuit setup VLAN group update IPSec Routing table update; RSVP Popping or pushing labels to packet; TTL decrement Path table updates Major Components of Routers : Switch Fabric HAUMAN 豪 技 勉 科 Memory Bus Shared Memory Crossbar Interconnect Input Ports to Output Ports, includes 3 modes Bus All Input ports transfer data through the shared bus. Problem : Often cause in data flow congestion. Shared Memory Input port write data into the share memory. After destination lookup is performed, the output port read data from the memory. Problem : Require fast memory read/write and management technology. Crossbar N input ports has dedicated data path to N output ports. Result in N*N switching matrix. Problem : Blocking (Input, Output, Head-of-line HOL). Max switch load for random traffic is about 59%. HAUMAN 豪 技 Queuing Technology 勉 科 Input Queuing Output Queuing Memory b/w = 2R N : Number of Input/output ports R : Line Rate Usually a non-blocking switch fabric (e.g. crossbar) Usually a fast bus Queuing Technology : Output Queuing HAUMAN 豪 技 勉 科 Individual Output Queues Centralized Shared Memory Memory b/w = 2N.R 1 2 N 1 2 Memory b/w = (N+1).R N : Number of Input/output ports R : Line Rate N HAUMAN 豪 技 勉 科 Switch Fabric : Crossbar Head-of-Line Blocking (HOL) HAUMAN 豪 技 勉 科 Switch Fabric : Crossbar Virtual Output Queue (VOQ) Require N*N Buffers N=Number of Output ports HAUMAN 豪 技 勉 科 Router Architecture and Technologies Major Router Functionalities Major Hardware of Routers Major Components of Routers The Evolution of Router Architecture Case Study – A Juniper Networks Example Architecture Overview Routing Engine Forwarding Engine Hardware & Architecture Flexibility First Generation Routers : Single Processor, Shared Bus HAUMAN 豪 技 勉 科 Typically <0.5Gb/s aggregate capacity CPU Route Table Buffer Memory Line Interface Line Interface Line Interface MAC MAC MAC Shared Backplane Bottlenecks: 1. The CPU has to process all packets flowing through the router. 2. The memory access rate limitation for memory intensive operations. 3. Every packet has to traverse twice through the shared bus. Second Generation Routers : Multiple Processors, Shared Bus HAUMAN 豪 技 勉 科 Typically <5Gb/s aggregate capacity CPU Route Table Buffer Memory Line Card Line Card Line Card Buffer Memory Buffer Memory Buffer Memory Fwding Cache Fwding Cache Fwding Cache MAC MAC MAC Bottlenecks: The shared bus still allowed only one packet at a time to move from input to output port. Route caching may not be efficient if cache not hit. The general purpose CPU in the slow path still been a bottle neck for specific traffic pattern. Third Generation RoutersGigabit Switching Router Multiple Processors, Switched Fabric HAUMAN 豪 技 勉 科 Typically <50Gb/s aggregate capacity Bottlenecks: Switch Fabric Capacity : N * N Matrix Switched Backplane Line Card CPU Card Line Card Local Buffer Memory Routing Table Local Buffer Memory Fwding Table Fwding Table MAC MAC Physical limitation : Circuit density and number of (I/O) pins Interconnection complexity and Power dissipation Example C_12012(60Gbps) : 12*12 C_12016(80Gbps) : 16*16 C_12416(320Gbps) : 64*64 C_12XXX(1Tbps) : 256*256? Slow Path HOL without VOQ Problems : Distribute PFE architecture result in different performance and functionalities. Fourth Generation RoutersMulti-Terabit Switching Router HAUMAN 豪 技 勉 科 Optics inside a router for the first time Optical links Switch Core Line cards 0.3 - 10Tb/s routers in development Fourth Generation RoutersMulti-Terabit Switching Router HAUMAN 豪 技 勉 科 Matrix Technology Greater than 10 Tbps 5 Tbps WAN + 5 Tbps LOCAL Interface connectivity T640 T640 Switch fabric connectivity T640 T640 HAUMAN 豪 技 勉 科 Router Architecture and Technologies Major Router Functionalities Major Hardware of Routers Major Components of Routers The Evolution of Router Architecture Case Study – A Juniper Networks Example Architecture Overview Routing Engine Forwarding Engine Data Path Internet Processor II Hardware & Architecture Flexibility Juniper Networks M&T Series Routers Overview HAUMAN 豪 技 勉 科 Packet Forwarding Performance per Rack Inch T640 Industry's first true solution for high-performance access M40 Industry's first 10G-class solution or ultra-high end access M160 T320 M40e M5/M10 M20 Industry's fastest router today. OC768 ready. A Growing History of Rapid Innovation 1998.09 1999.12 2000.03 2000.09 2002.02 2002.04 2002.07 Juniper Networks M&T Series Routers Overview HAUMAN 豪 技 勉 科 Packet Throughput TX T640 M40e M160 T320 M40 M20 M5/M10 4/8 PIC Slot >5/10Gbps 16 PIC Slot >20Gbps 32 PIC Slot >40Gbps 32 PIC Slot >40Gbps 32 PIC Slot >160Gbps 32 PIC Slot 16 PIC Slot >640Gbps >320Gbps 1~10Tbps Density Juniper Networks Breakthrough Density HAUMAN 豪 技 勉 科 Ports per rack 300 256 250 200 150 100 50 0 64 56 14 OC-48 OC-192 12416 Redundant configurations T640 redefines the core routing market Juniper M-Series Chassis Overview HAUMAN 豪 技 勉 科 A M40e Example Craft Interface Flexible PIC Concentrators (FPCs) Physical Interface Cards (PICs) Switch Fabric Modules (SFMs) Miscellaneous Control Modules (MCSs) Routing Engines (REs) PFE Clock Generators (PCGs) Power Entry Modules (PEMs) Front Rear HAUMAN 豪 技 Juniper M-Series Architecture 勉 科 Routing Engine Junos Internet Software Forwarding Table Software Update Internet Packet Forwarding Engine Processor II Forwarding Table Switch Fabric I/O Card I/O Card Intelligent Hardware Pure Hardware (With Microcode) Juniper M-Series Architecture : System Partitioning HAUMAN 豪 技 勉 科 All Packets Control Packets Only Forwarding Engine (FE) Routing Engine (RE) Why this partitioning is good Problem is broken into two roughly equally complex parts that interact infrequently Loading of one does not affect the other, eliminating a common failure mode of legacy routers Facilitates independent hardware and software development and early software testing RE is standard off-the-shelf Intel platform, so it leverages industry advances in computer design and can be leveraged across multiple generations of FE’s with no change HAUMAN 豪 技 Routing Engine 勉 科 Fast Intel™ based Compact-PCI platform 768MB DRAM Routing Table Forwarding Table Storage Primary:80MB fixed flash memory Two Software Images Two Configuration Files Microcode Secondary:6.4GB IDE hard drive Log Files Memory Dumps External :128MB PC Card flash drive Capacity BT Test : 450,000 Entries for Internet and MPLS VRF HAUMAN 豪 技 Routing Engine 勉 科 Atomic Table Updates Advantages Updated portion of forwarding table created separate from active table New portion “switched into” live table Single 32-bit atomic operation Done in one system clock cycle No forwarding interruption Other vendors Stop forwarding on all interface cards simultaneously Update table on each interface card HAUMAN 勉 科 JUNOS Internet Software Common software across all platforms M-series and T-series Internet-class operating system Best-in-class routing protocol implementations Foundation for providing new features for services Standards based MPLS VPNs IPv6 Security SNMP Protected memory architecture prevents one module from corrupting others Rapid software change and verification Restart or upgrade specific module without rebooting entire chassis Chassis Mgmt Modular design for high reliability Interface Mgmt JUNOS 5.4 – 15th Major Release Protocols 豪 技 Operating System HAUMAN 豪 技 JUNOS Software Code Train 勉 科 3.2 3.3 3.4 4.0 Multicast Services 4.1 4.2 4.3 DoS Attack Containment Frame/ATM Migration 4.4 5.0 5.1 5.2 5.3 Packet Sampling & Counting 5.4 HAUMAN 豪 技 勉 科 Packet Forwarding Engine : A M40e Example HAUMAN 豪 技 勉 科 Juniper M-Series : Shared Memory Interconnect Efficiency of memory bandwidth One write, one read Ease of multicasting One write, number of reads <= number of ports on shared memory Note Shared Memory is in FPC, controlled by DBM ASIC, and can be synchronized within 200ms. HAUMAN 豪 技 勉 科 Juniper M-Series: PFE Architecture Benefit All forwarding decisions are centralized All interfaces perform equally well New features added to Internet Processor become immediately available on every interface type All packet sizes are handled exactly the same Latency through the PFE is constant across packet sizes Latency very low (< 10µs) Adding additional FPCs adds additional shared memory Available to any interface in the system There is never a possibility of “memory starvation” HAUMAN 豪 技 Internet Processor II ASIC 勉 科 IP II內建三種封包處理原始程序(Primitives): 樹狀查詢(Tree lookup) 執行IPv4或IPv6路由表的「最長字首配對」 查詢工作 也可供過濾程式用來搜尋字首(Prefix)。 表格查詢(Table lookup) 決定另一個程序是否要被執行,例如一個基 於封包輸入介面的表格查詢,可以決定是否 要針對特定的封包執行防火牆過濾程式。 表格查詢也很適合用來進行MPLS的Tag查詢, 因為其比「樹狀查詢」使用更少的記憶體。 過濾指令引擎(Filter instruction engine) 用來將流量分類,並針對所有符合「特定類 別」的封包執行「特定功能」。 過濾程式並非使用微碼來佈署,而是透過使 用者介面利用高階語言所撰寫的使用者定義 程式(User-Defined Programs),在進行組譯 (Compile)及最佳化工作後,使其能在 Internet Processor II ASIC上順利執行。 HAUMAN 豪 技 勉 科 Internet Processor II ASIC : Flexible Architecture IP II ASIC 可以任意排列以上三種原始程序,以進行各式各樣的封包處理工作 HAUMAN 豪 技 勉 科 Internet Processor II ASIC : Enabling Smart IP Services Service Features Premium Features Flexible Bandwidth Juniper Networks Enablers SP IP Services Priority Services Line-Rate Packet Filtering VPNs Rate Limiting Dedicated High Speed Access Layer 3 VPNs Packet Classification (CoS) Layer 2 VPNs Filter-Based Forwarding Security Packet Sampling & Counting DoS Attack Containment Line-Rate Forwarding Managed Firewall MPLS Traffic Engineering Convergence / Migration Generalized MPLS Virtual Leased Line RFC 2547bis VPNs Frame/ATM Migration Translational Cross Connect IP VPNs Transit Services Multiservice Multicast Services VoIP Transport Circuit Cross Connect IP Multicast Juniper M-Series : Hardware Performance HAUMAN 豪 技 勉 科 All ASICs in Packet Forwarding Engine PIC Media-Specific ASIC per interface FPC Packet Director ASIC I/O Manager ASIC Switching Fabric Module Distribute Buffer Manager ASIC Internet Processor II ASIC HAUMAN 豪 技 勉 科 Juniper Networks announced winner of key and overall testing categories March 12, 2001, Best IP Best MPLS Best OC-48c Best OC-192c Best Overall Juniper Networks Cisco “The M160 clearly demonstrates why Juniper has come so far in so few years… This is truly the best core router available today.” Source: Light Reading, March, 2001 http://www.lightreading.com/testing/ - David Newman Juniper M-Series : Hardware Flexibility HAUMAN 豪 技 勉 科 Why Juniper Hardware with Flexibility? Flexible Forwarding Engine All ASICs in forwarding data path are hard-coded ASICs with microcode instruction set. Intelligent Hardware IP II ASIC support various lookup by changing the components and order of primitives. ASIC JUNOS ASICs’ Microcode can easily be reprogrammed by JUNOS upgrading. Hard-Code:固定功能 Microcode:彈性功能 Juniper M-Series : Architecture Flexibility HAUMAN 豪 技 勉 科 Why Juniper Hardware support IPv6/MPLS in any Interface? Separated Routing and Forwarding Engine Routing Engine : CPU cooperate with JUNOS Forwarding Engine : ASICs Re-Programmable ASICs with Microcode Instruction Set I/O Manager ASIC Can be programmed to recognize different types of frames, including IPv4, IPv6, Frame Relay, MPLS, and IPX. Distributed Buffer Manager ASIC Can be programmed to look at any point in a packet header to extract forwarding information and build packet notifications. Intelligent Internet Processor II ASICs Using millions logic to perform three primitives, not applications. Using JUNOS to chain different primitives in any order to perform various applications. Filter programs can be complied through CPU in Routing Engine. Modular Design JUNOS Accelerate the delivery of major releases. (4+ MR per year) Same software image for all platforms. Service PIC for special service Only for specific traffic and won’t affect common traffic flow. HAUMAN 豪 技 Juniper IP Service PICs 勉 科 ES PIC IPSec encryption up to 800-Mbps throughput rates (half duplex) 1,000 IPSec tunnels or 2,000 security association (SA) pairs per PIC Multilink Services PIC Aggregate throughput up to 450-Mbps, full-duplex Supports up to 128 bundles with 8 links per bundle Passive Monitoring PIC 100-Kpps of monitoring performance per PIC Supports 1 million records Tunnel Services PIC IP-IP unicast tunneling. GRE unicast tunneling. PIM-SM encapsulation and deencapsulation for locally attached hosts and rendezvous point operation. HAUMAN 豪 技 Summary 勉 科 Category Features IP Scale T-series & M-series: Single binary image JUNOS seamless scale to multi-terabit IP Dependability IP Security IP Service Richness Internet proven platforms Internet proven JUNOS Any port, any speed, any scale No compromise Any port, any speed, any scale No compromise HAUMAN 豪 技 勉 科 Questions? HAUMAN 豪 技 勉 科 Thank You!