EECS 122 Communications Networks

advertisement

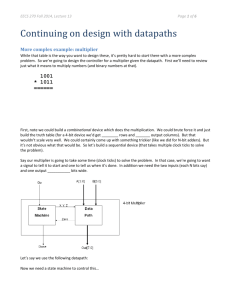

Lecture 11 Switching & Forwarding EECS 122 University of California Berkeley TOC: Switching & Forwarding Why? Switching Techniques Switch Characteristics Switch Examples Switch Architectures Summary EECS 122 Walrand 2 Switching: Why? Direct vs. Switched Networks: n links Single link Switches Direct Switched Direct Network Limitations: Distance (coordination delay; propagation limitation) Number of hosts (collisions; shared bandwidth; address tables) Single link technology (cannot mix optical, wireless, …) Internetworking: Externality gain at low cost EECS 122 Walrand 3 Switching: Techniques Circuit-Switching (e.g., Telephone net.) Packet-Switching Datagram (e.g., IP, Ethernet) Virtual Circuits (e.g., MPLS, ATM) Source Routing Comparison EECS 122 Walrand 4 Techniques: Circuit-Switching Link divided into fixed, independent circuits Mechanism: Features: Circuit Switch Connection list Time scale: connection (e.g., TDM, WDM) • Packets not switched independently (establish circuit before sending data) • Dedicated path and resources from source to destination • Setup time; low delays and guaranteed resources thereafter EECS 122 Walrand 5 Techniques: Packet-Switching Whole link shared by all packets Mechanism: Packet Switch Features: • Data separated into packets • Switching decision (output port) for each individual packet • Statistical multiplexing: Sum of peak rates may exceed link bandwidth (as long as mean does not) EECS 122 Walrand 6 Techniques: PS - Datagram General idea: no connection establishment, but each packet contains enough info to specify destination Switches contain forwarding tables (but no per-connection “state”) Forwarding tables contain info on which outgoing port to use for each destination Two types of addressing: EECS 122 Layer 2 or Layer 3 Walrand 7 Datagram: Layer 2 (e.g., Ethernet) Flat address space (no structure) Forwarding table: Exact match of destination L2 address a b e|b| 1 4 a b c d e f 1 4 3 2 2 2 2 1 a b c d e f 4 3 c 1 1 1 2 3 4 2 3 d e f To From EECS 122 Walrand 8 Datagram: Layer 3 (e.g., IP) E.g. 1 E.g. 2 L3-network (e.g., IP) Topological structure – match prefix Either fixed prefix length or longest match 10100111 11010001 B 10100000 1101 A’ 11010101 11001101 EECS 122 E.g. 3 11010000 B’ Fixed Longest D A Other 11001000 C 1100 C’ Walrand 11001001 01000000 11100000 9 Datagram: Layer 3 (e.g., IP) E.g. 1 11011001 matches 4 bits at A, 1 at B, 3 at C A = LPM 4 bits at A’ A’ = EM 10100111 11010001 B 10100000 1101 A’ 11010101 11001101 EECS 122 11010000 B’ Fixed Longest D A Other 11001000 C 1100 C’ Walrand 11001001 11011001 01000000 11100000 10 Datagram: Layer 3 (e.g., IP) E.g. 2 11001001 matches 3 bits at A, 1 at B, 7 at C C = LPM 10100111 11010001 B 10100000 1101 A’ 11010101 11001101 EECS 122 11010000 B’ Fixed Longest D A Other 11001000 C 1100 C’ Walrand 11001001 11001001 01000000 11100000 11 Datagram: Layer 3 (e.g., IP) 01100101 matches 0 bit at A’ B’ 0 bit at B, 0 at C, 2 at D D = LPM 10100111 11010001 B 10100000 1101 A’ 11010101 11001101 E.g. 3 11010000 B’ Fixed Longest D A Other 11001000 C 1100 C’ 01000000 11100000 01100101 EECS 122 Walrand 11001001 12 Techniques: PS – Virtual Circuit Connection setup establishes a path through switches A virtual circuit ID (VCI) identifies path Uses packet switching, with packets containing VCI VCIs are often indices into per-switch connection tables; change at each hop VC1 VC2 1 2 VC1 EECS 122 In, VC Out, VC 1, 1 4, 1 1, 2 4, 3 2, 1 4, 2 4 VC1 VC2 3 1 VC3 2 VC1 Walrand 4 3 VC1 VC2 …. 13 Techniques: Source Routing Each packet specifies the sequence of routers (or of output ports) from source to destination source 4 3 4 1 2 3 4 1 2 3 4 1 2 3 4 4 3 4 EECS 122 1 2 3 4 Walrand 1 2 3 4 1 2 3 4 4 3 4 14 Techniques: Comparison Datagram Forwarding cost Bandwidth utilization Resource reservations Robustness* Circuit switching high Virtual circuit switching low high flexible low none flexible yes high low low none *The idea is that in case of failure, circuit and VC are lost; datagram routing can adapt after routing update …. EECS 122 Walrand 15 Switching: Characteristics Ports Fast Ethernet, OC-3, ATM, … Protocols ST, Link Agg., VLAN, OSPF, RIP, BGP, VPN, Load Balancing, WRED, WFQ Performance EECS 122 Throughput, Reliability, Power, … Walrand 16 Switching: Examples Juniper M160 Cisco “GSR” Cisco “7600” Cisco “catalyst 6500” Extreme “Summit” Foundry “ServerIron” EECS 122 Walrand 17 Examples: Cisco GSR - 12416 WAN Router – Large throughput; SONET links Up to 16 line cards at 10 Gbps each Crossbar Fabric Cisco GSR 12416 19” Line Cards: 1-port OC-192c 4-port OC48c Many others (ATM, Ethernet, …) 6ft 2ft EECS 122 Walrand 18 Examples: Juniper M160 WAN Router – Large throughput; SONET links Crossbar Fabric Line Cards: 1-port OC-192c Juniper M160 4-port OC48c 19” Many others (ATM, Ethernet, …) Capacity: 3ft 80Gb/s Power: 2.6kW 2.5ft EECS 122 Walrand 19 Examples: Cisco 7600 MAN-WAN Router Up to 128 Gbps with Crossbar Fabric 10Mbps – 10Gbps LAN Interfaces OC-3 to OC-48 SONET Interfaces MPLS, WFQ, LLQ, WRED, Traffic Shaping EECS 122 Walrand 20 Examples: Cisco cat 6500 From LAN to Access 48 to 576 10/100 Ethernet Interfaces 10 GE, OC-3, OC-12, OC-48, ATM QoS, ACL Load Balancing; VPN Up to 128Gbps (with crossbar) L4-7 Switching VLAN IP Telephony (E1, T1, inline-power Ethernet) SNMP, RMON EECS 122 Walrand 21 Examples: Extreme - Summit 48 10/100 ports 2 GE (SX, LX, or LX-70) 17.5Gbps non-blocking 10.1 Mpps Wire speed L2 Wire speed L3 static or RIP OSPF, DVRMP, PIM, … EECS 122 Walrand 22 Examples: Foundry - ServerIron Server Load Balancing Transparent Cache Switching Firewall Load Balancing Global Server Load Balancing Extended Layer 4-7 functionality including URL-, Cookie-, and SSL Session ID-based switching Secure Network Address Translation (NAT) and Port address translation (PAT) EECS 122 Walrand 23 Switching: Architectures Generic Architecture First Generation Second Generation Third Generation Input Functions Output Functions Interconnection Designs OUT IN VOB Combined IN/OUT EECS 122 Walrand 24 Architectures: Generic Input and output interfaces are connected through an interconnect A interconnect can be implemented by input interface output interface Interconnect Shared memory low capacity routers (e.g., PC-based routers) Shared bus Medium capacity routers Point-to-point (switched) bus High capacity routers EECS 122 Walrand 25 Architectures: First Generation Shared Backplane CPU Route Table Buffer Memory Line Interface Line Interface Line Interface MAC MAC MAC Typically < 0.5Gbps aggregate capacity Limited by rate of shared memory Slide by Nick McKeown EECS 122 Walrand 26 Architectures: Second Generation CPU Typically < 5Gb/s aggregate capacity Limited by shared bus Buffer Memory Route Table Line Card Line Card Line Card Buffer Memory Buffer Memory Buffer Memory Fwding Cache Fwding Cache Fwding Cache MAC MAC MAC Slide by Nick McKeown EECS 122 Walrand 27 Architectures: Third Generation Switched Backplane Line Card Local Buffer Memory Line Card Routing Table Local Buffer Memory Fwding Table Fwding Table MAC MAC Typically < 50Gbps aggregate capacity EECS 122 CPU Card Walrand Slide by Nick McKeown 28 Architectures: Input Functions Packet forwarding: decide to which output interface to forward each packet based on the information in packet header examine packet header lookup in forwarding table update packet header EECS 122 Walrand 29 Architectures: Output Functions Buffer management: decide when and which packet to drop Scheduler: decide when and which packet to transmit Buffer Scheduler 1 2 EECS 122 Walrand 30 Architectures: Output Functions (ct) Packet classification: map each packet to a predefined flow/connection (for datagram forwarding) use to implement more sophisticated services (e.g., QoS) Flow: a subset of packets between any two endpoints in the network flow 1 1 2 Classifier flow 2 Scheduler flow n Buffer management EECS 122 Walrand 31 Architectures: Output Queued Only output interfaces store packets Advantage Easy to design algorithms: only one congestion point input interface output interface Disadvantage Requires an output speedup Ro/C = N, where N is the number of interfaces not feasible for large N Backplane RO EECS 122 Walrand C 32 Architectures: Input Queues Only input interfaces store packets Advantages Easy to build Simple algorithms input interface output interface Disadvantages HOL Blocking In practice: Speedup of 2 suffices Backplane RO EECS 122 Walrand C 33 Note: Head-of-line Blocking The cell at the head of an input queue cannot be transferred, thus blocking the following cells Cannot be transferred because of HOL blocking Input 1 Output 1 Input 2 Output 2 Input 3 Output 3 Cannot be transferred because of output contention Being transferred EECS 122 Walrand 34 Architectures: Virtual Output Buffers OUT buffers at each input port Complexity: Matching Problem Full throughput algorithm Good Heuristic Crossbar Note: Figure from Prof. Varaiya’s notes for EE228b EECS 122 Walrand 35 VOB: Full Throughput Maximum Weighted Matching: A = 14 B = 11 C = 15 D = 10 B + C > A + D => Serve (B, C) EECS 122 Walrand 36 VOB: Good Heuristic – i-SLIP Inputs request permission to send from outputs Outputs grant permissions to inputs (round-robin) Inputs accept permissions (round-robin) Request Grant Accept Iter 3 1 2 Last Accept EECS 122 2 1 3 Last Grant Walrand 37 Architectures: Combined IN/OUT Both input and output interfaces store packets Advantages input interface output interface Easy to built Utilization 1 can be achieved with limited input/output speedup (<= 2) Backplane Disadvantages Harder to design algorithms Two congestion points RO C Need to design flow control EECS 122 Walrand 38 Switching: Summary Switching needed for big networks Internetworking externality Circuit Packet – VC: QoS possible Packet – Datagram L2: Limited by flat address space L3: Exact Match: Easy lookup – less efficient Longest Prefix Match Switch functions: control and data Different Architectures: EECS 122 cost vs. performance Walrand 39