VHDL

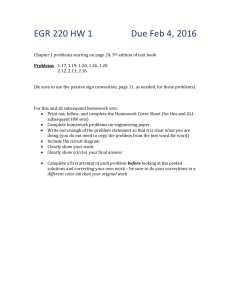

advertisement

數位電路晶片設計及實習講義

半導體學院

數位電路設計人才培訓班

郭英哲 編撰

國立勤益技術學院 電機系

92.10.12

2016/3/23

Digital Circuit IC Design

1

數位電路晶片設計及實習

• 授課教師:郭英哲 (04-23924505 ext:7271)

kuoyc@chinyi.ncit.edu.tw

• 上課時數:2堂正課、2堂實習,計3學分。

• 開課學期:四技一下選、在職二技一下選、進推部二技選

• Text Book :

J. Bhasker, “A VHDL Primer 3/e,” Prentic-Hall, 1999

蕭如宣,VHDL數位電路設計,儒林出版,SIM-829

• Reference Book :

李宜達,數位邏輯電路設計與模擬---使用AHDL/VHDL,全華出版

唐佩忠,VHDL與數位邏輯設計,高立出版108328

盧毅,VHDL與數位電路設計,文魁出版T0278

林明權,數位控制系統設計---使用VHDL,全華出版 05066

2016/3/23

Digital Circuit IC Design

2

數位電路晶片設計及實習

•

實習設備:24套

– P-4 2.4GHz PC

– ALTERA公司(www.altera.com) MAX+Plus–II Baseline設計軟體

– 力浦電子(www.leap.com.tw) LP-2900實驗板一組(含變壓器及25-pin printer port

cable)

•

上課內容:

–

–

–

–

–

–

–

•

晶片設計資源介紹

ALTERA MAX+Plus – II 設計軟體介紹

Schematic design

VHDL syntax

組合邏輯電路設計

序向邏輯電路設計

期末專題

計分方式:

– 平時

– 期末專題

– 期末術科考試

2016/3/23

50% (有5次實驗,每個實驗10%)

20%

30%

Digital Circuit IC Design

3

2016/3/23

Digital Circuit IC Design

4

Using fixed function ICs

2016/3/23

Digital Circuit IC Design

5

IC design approach

2016/3/23

Digital Circuit IC Design

6

Introduction

passive components(1/2)

2016/3/23

Digital Circuit IC Design

7

Introduction

passive components(2/2)

2016/3/23

Digital Circuit IC Design

8

Introduction

IC and VLSI

2016/3/23

Digital Circuit IC Design

9

Introduction

IC design methnologies

2016/3/23

Digital Circuit IC Design

10

Active Components

logic Gates(1/12)

2016/3/23

Digital Circuit IC Design

11

Active Components

logic Gates(2/12)

VHDL syntax

Y <= not A ;

2016/3/23

Digital Circuit IC Design

12

Active Components

logic Gates(3/12)

VHDL syntax

Y <= A ;

2016/3/23

Digital Circuit IC Design

13

Active Components

logic Gates(4/12)

VHDL syntax

Y <= A nand B ;

2016/3/23

Digital Circuit IC Design

14

Active Components

logic Gates(5/12)

VHDL syntax

Y <= A nor B ;

2016/3/23

Digital Circuit IC Design

15

Active Components

logic Gates(6/12)

2016/3/23

Digital Circuit IC Design

16

Active Components

logic Gates(7/12)

VHDL syntax

Y <= A xor B ;

2016/3/23

Digital Circuit IC Design

17

Active Components

Combinational Circuit

2016/3/23

Digital Circuit IC Design

18

Active Components

logic Gates(8/12)

2016/3/23

Digital Circuit IC Design

19

Active Components

logic Gates(9/12)

2016/3/23

Digital Circuit IC Design

20

Active Components

logic Gates(10/12)

2016/3/23

Digital Circuit IC Design

21

Active Components

example of tri-state buffer

2016/3/23

Digital Circuit IC Design

22

Active Components

logic Gates(11/12)

2016/3/23

Digital Circuit IC Design

23

Active Components

logic Gates(12/12)

2016/3/23

Digital Circuit IC Design

24

Active Components

sequential Circuit

2016/3/23

Digital Circuit IC Design

25

2016/3/23

Digital Circuit IC Design

26

2016/3/23

Digital Circuit IC Design

27

2016/3/23

Digital Circuit IC Design

28

Programmable Logic Device

•

•

•

•

•

PROM: Programmable ROM

PLA : Programmable Logic Array

PAL: Programmable Array Logic

PEEL: Programmable Electrically Erasable Array

FPGA: Field Programmable Gate Array

2016/3/23

Digital Circuit IC Design

29

PROM

• AND部份不可以規劃

• OR部份可以規劃

2016/3/23

Digital Circuit IC Design

30

2016/3/23

Digital Circuit IC Design

31

2016/3/23

Digital Circuit IC Design

32

2016/3/23

Digital Circuit IC Design

33

2016/3/23

Digital Circuit IC Design

34

2016/3/23

Digital Circuit IC Design

35

2016/3/23

Digital Circuit IC Design

36

2016/3/23

Digital Circuit IC Design

37

2016/3/23

Digital Circuit IC Design

38

2016/3/23

Digital Circuit IC Design

39

get symbol

(schematic)

• Symbol \ Enter symbol (or double-click)

2016/3/23

AND2

VCC

OR3

DFF

INPUT

OUTPUT

Digital Circuit IC Design

40

4-bit asynchronous (非同步)ripple downcounter

(schematic)

2016/3/23

Digital Circuit IC Design

41

Steps of simulation

(schematic)

• File / New / Waveform Editor File

• Node / Enter Nodes from SNF…

• Right-click / Enter Nodes from SNF…

2016/3/23

Digital Circuit IC Design

42

Steps of simulation

end time / grid size

• File / End time

– 延長模擬時間

• Options / grid size

– 設定最小時間刻度

2016/3/23

Digital Circuit IC Design

43

Steps of simulation

end time / grid size

2016/3/23

Digital Circuit IC Design

44

Result of simulation

2016/3/23

Digital Circuit IC Design

45

Result of simulation

Delay會累加

2016/3/23

Digital Circuit IC Design

46

4-bit synchronous(同步) up-counter

2016/3/23

Digital Circuit IC Design

47

Result of simulation

2016/3/23

Digital Circuit IC Design

48

Result of simulation

不會有Delay累積

2016/3/23

Digital Circuit IC Design

49

Create user symbol

Create symbol

2016/3/23

Digital Circuit IC Design

50

Create user symbol

• \File \Create Default Symbol

Create Default Symbol

2016/3/23

Digital Circuit IC Design

51

Create user library

• step 1 : Options / User Libraries

2016/3/23

Digital Circuit IC Design

52

Create user library

• step 2 : assign the library directory

• step 3 : 將 xxx.gdf (schematic)、xxx.tdf (AHDL)、

xxx.vhd (VHDL)、xxx.sym (symbol)等檔案 copy 至

此 user libraries 目錄下

2016/3/23

Digital Circuit IC Design

53

Quiz

• Down counter (下數) → Up counter (上數)

• Asynchronous (非同步) → Synchronous (同步)

2016/3/23

Digital Circuit IC Design

54

mod-10 (BCD) up-counter

2016/3/23

Digital Circuit IC Design

55

2-digit mod-10 up-counter

個位數

拾位數

2016/3/23

Digital Circuit IC Design

56

2-digit mod-10 up-counter

2016/3/23

Digital Circuit IC Design

57

實驗進度

• Counter (falling-/rising-edge trigger, sync/ripple)

– 4-/8-bit, mod-10/mod-12

– 2-digit mod-10 up-counter

• 除頻電路

– 除2/4/8/16/../2n, 50% duty-cycle

– 除10 (偶數), 50% duty-cycle (責任周期)

– 除13 (奇數), 50% duty-cycle

2016/3/23

Digital Circuit IC Design

58

mod-10 (BCD) up-counter

for divide-10

2016/3/23

Digital Circuit IC Design

59

除2波形

x

x

除2

y

y

x

y

P.S. 任何波形 除2 後會對稱

2016/3/23

Digital Circuit IC Design

60

Disbounce circuit

(schematic)

Q0

Q1

INV_KEY

2016/3/23

Digital Circuit IC Design

61

simulation result under 200ns clock rate

2016/3/23

Digital Circuit IC Design

62

simulation result under 100ns clock rate

2016/3/23

Digital Circuit IC Design

63

Conclusion of DISBOUNCE circuit

• clock 的frequency 會對disbounce效果有所影響

– clock快 按鍵較靈敏,disbounce 效果較差

– clock慢 按鍵較遲鈍,disbounce 效果良好

• P.S. clock generator :

• Crystal 石英晶體

• Oscillator (O.S.C) 振盪器

2016/3/23

Digital Circuit IC Design

64

Implementation of LED example

keyin

O.S.C

10MHz

2016/3/23

除10000

Disbounce

4-bit

Up counter

Digital Circuit IC Design

65

實驗設備LP-2900(力浦公司)

2016/3/23

Digital Circuit IC Design

66

實驗設備LP-2900(力浦公司)

Altera FLEX10K family device

EPF10K10TC144-4

• 指定IC

\Assign \Device\

2016/3/23

Digital Circuit IC Design

67

ALTERA FLEX 10K devices

2016/3/23

Digital Circuit IC Design

68

ALTERA FLEX 10K devices

2016/3/23

Digital Circuit IC Design

69

ALTERA FLEX 10K devices

2016/3/23

Digital Circuit IC Design

70

ALTERA FLEX 10K devices

2016/3/23

Digital Circuit IC Design

71

ALTERA FLEX 10K devices

2016/3/23

Digital Circuit IC Design

72

Quad Package

• Quad Package family includes

– QFP : Quad Flat Pack

– LQFP : Low-profile Quad Flat Pack

– TQFP : Thin Quad Flat Pack

• All of the Quad Packages are with Gullwing lead.

With the same QFP outline, thermally enhanced QFP

provides better thermal performance. LQFP (body

thickness 1.4 mm) and TQFP (body thickness 1.0 mm)

with reduced thickness are offered to meet thin

profile requirement. Thermally enhanced structures

are also applicable in LQFP and TQFP to improve the

thermal performance.

• 封測廠 : 矽品 www.spil.com.tw

•

日月光 www.asecl.com.tw

2016/3/23

Digital Circuit IC Design

73

TQFP

2016/3/23

Digital Circuit IC Design

74

Configuration EPROMs

2016/3/23

Digital Circuit IC Design

75

Configuration EPROMs

2016/3/23

Digital Circuit IC Design

76

Appropriate configuration EPROM

for each FLEX device

2016/3/23

Digital Circuit IC Design

77

EPC1 & EPC1V pin function during

FLEX 10K device configuration

2016/3/23

Digital Circuit IC Design

78

腳位配置floorplan

•

腳位配置floorplan

(1) \Maxplus II \Floorplan Editor\

(2) \Layout\ Current Assignments Floorplan

2016/3/23

Digital Circuit IC Design

79

Device programming

2016/3/23

Digital Circuit IC Design

80

Device programming

2016/3/23

Digital Circuit IC Design

81

晶片規劃 programming

(1) \Maxplus II \ Programmer

(2) \Options \ Hardware Setup

Byte Blaster(MV), LPT1

(3) \JTAG \ Multi-Device JTAG Chain Setup

1

5

3

4

2

2016/3/23

Digital Circuit IC Design

82

HDL硬體描述語言

• HDL : Hardware Description Language

– VHDL

– Verilog HDL

– AHDL (for Altera)

– ABEL-HDL (for Xilinx and Lattice)

2016/3/23

Digital Circuit IC Design

83

Introduction to VHDL

VHDL :Very High Speed Integrated Circuit Hardware Description

Language

1970-1980

美國國防部開始發展

VHDL 成為IEEE制定的標準,稱為IEEE 1076

IEEE : Institute of Electrical and Electronics Engineer, 電機暨電子工程師學會

修改為IEEE 1164

將電路合成的程式標準與規格加入到VHDL電路設計語言中,稱之為 IEEE 1076.3

VHDL可依據的標準:

(1) std_logic_1164:std_logic、std_logic_vector

follow IEEE std 1164-1993

(2) standard:bit、bit_vector

follow IEEE std 1076-1987

(3) std_logic_arith:signed、unsigned

MAX+Plus II VHDL on-line help

menu \ help \ VHDL \ VHDL 1993 syntax

www.altera.com

2016/3/23

Digital Circuit IC Design

84

VHDL基本語法架構:

library ieee;

use

ieee.std_logic_1164.all ;

entity 單體名稱 is

port ( 訊號 A

: 模式

訊號 B

: 模式

訊號 N

end 單體名稱 ;

: 模式

-- library declaration

-- used package, IEEE standard

資料型別 ;

資料型別 ;

…

…

資料型別

);

architecture 架構名稱 of 單體名稱 is

{ 架構之宣告區 }

begin

{ 電路描述…

…..

}

end 架構名稱 ;

P.S. port的模式共定義了四種 in、out、buffer、inout。

2016/3/23

Digital Circuit IC Design

85

與儲存檔名

相同

entity 宣告

entity 單體名稱 is

port (訊號 A : 模式

訊號 B : 模式

訊號 N

end 單體名稱 ;

: 模式

資料型別 ;

資料型別 ;

…

…

資料型別 ) ;

-------------------------------------------------------------entity up_cnt4 is

port(

CLK

: in bit ;

QD

: out bit_vector(3 downto 0)

);

end up_cnt4;

2016/3/23

Digital Circuit IC Design

86

識別字 identifier

•

•

•

•

第一個字必須為英文字母

最後一個字不可以為底線 ”_”

不可以連續兩個底線 ”__”

不可以為保留字(reversed word)

– and, or, not, if, else, in, out, is, case, for, function…

• 可以是英文大寫(A~Z)、英文小寫(a~z)、數字(0~9)或者底

線 ”_”

• 不分大小寫

2016/3/23

Digital Circuit IC Design

87

保留字 reserved word (1/2)

ABS

ACCESS

AFTER

ALIAS

ALL

AND

ARCHITECTURE

ARRAY

ASSERT

ATTRIBUTE

BEGIN

BLOCK

BODY

BUFFER

BUS

CASE

COMPONENT

CONFIGURATIO

N

CONSTANT

DISCONNECT

DOWNTO

ELSE

ELSIF

END

ENTITY

EXIT

FILE

FOR

FUNCTION

GENERATE

GENERIC

GROUP

GUARDED

IF

IMPURE

IN

INERTIAL

INOUT

IS

LABEL

LIBRARY

LINKAGE

LITERAL

LOOP

MAP

MOD

NAND

NEW

NEXT

NOR

NOT

NULL

OF

ON

OPEN

2016/3/23

Digital Circuit IC Design

88

保留字 reserved word (2/2)

OR

OTHERS

OUT

PACKAGE

PORT

POSTPONED

PROCEDURE

PROCESS

PURE

RANGE

RECORD

REGISTER

REJECT

REM

REPORT

RETURN

ROL

ROR

SELECT

SEVERITY

SIGNAL

SHARED

SLA

SLL

SRA

SRL

SUBTYPE

THEN

TO

TRANSPORT

TYPE

UNAFFECTED

UNITS

UNTIL

USE

VARIABLE

WAIT

WHEN

WHILE

WITH

XNOR

XOR

2016/3/23

Digital Circuit IC Design

89

port 模式

• in

– 輸入模式

• out

– 輸出模式

– 不可以回授到單體內部

• buffer

– 可以將訊號回授到單體內部的輸出模式

– 不能有多重驅動

– 只能回授至單體內部或其他同為buffer的單體

– 不可以接到其他單體電路的輸出(out)或雙向(inout)的接腳上

• inout

– 同時具有in、out、buffer三種工作模式

2016/3/23

Digital Circuit IC Design

90

port 模式

2016/3/23

Digital Circuit IC Design

91

port 資料型別

• type bit is ( ‘0’, ‘1’ ) ;

• type std_ulogic is ( ‘U’,

-- uninitialized, 未設定

‘X’, -- forcing unknown, 浮接不定

‘0’, -- forcing 0, ‘0’電位

‘1’, -- forcing 1, ‘1’電位

‘Z’, -- high impedance, 高阻抗

‘W’, -- weak unknown, 弱浮接

‘L’, -- weak 0, 弱低電位

‘H’, -- weak 1, 弱高電位

‘-’,

-- don’t care, 無在意

);

• Another types : bit_vector, std_ulogic_vector, std_logic,

std_logic_vector

2016/3/23

Digital Circuit IC Design

92

port 資料型別

2016/3/23

Digital Circuit IC Design

93

std_logic 資料型別

• Subtype std_logic is resolved std_ulogic

– 少了 ’-’

– 電位適當轉換, 參考IEEE std_logic_1164 package

– 常用 ‘0’, ‘1’, ‘z’

2016/3/23

Digital Circuit IC Design

94

Architecture body

structure style of modeling

•

In the structural style of modeling, an entity is described as a set of

interconnected components.

architecture 架構名稱 of 單體名稱 is

declaration part 宣告區

component declaration;

signal declaration;

constant declaration;

begin

statement part 敘述區

the interconnection of components;

end 架構名稱 ;

P.S. Signals, which represent wires, are used to connect the various

components.

2016/3/23

Digital Circuit IC Design

95

Architecture body

• 結構描述 Structure Description

– As a set of interconnected components (to represent structure)

• 資料流描述 Data Flow Description

– As a set of concurrent assignment statements (to represent

dataflow)

• 行為描述 Behavior Description

– As a set of sequential assignment statements (to represent

behavior)

• As any of combination of the above three

2016/3/23

Digital Circuit IC Design

96

Architecture body

• 結構描述 Structure Description

– As a set of interconnected components (to represent structure)

• 資料流描述 Data Flow Description

– As a set of concurrent assignment statements (to represent

dataflow)

• 行為描述 Behavior Description

– As a set of sequential assignment statements (to represent

behavior)

• As any of combination of the above three

2016/3/23

Digital Circuit IC Design

97

Architecture body

structure style of modeling 結構描述

U1

entity HALF_ADDER is

port ( A, B

: in bit;

SUM, CARRY

A

: out bit ) ;

end HALF_ADDER;

B

architecture HA_STRUCTURE of HALF_ADDER is

component AAA

port (

Y

Z

U2

: in bit;

L

Z

: out bit );

N

M

BBB

CARRY

: in bit;

: out bit );

U3

begin

C

U1 : AAA port map (A, B, SUM);

-- (X=>A, Y=>B, Z=>SUM);

U2 : BBB port map (A, B, CARRY);

D

-- (L=>A, M=>B, N=>CARRY);

end HA_STRUCTURE ;

SUM

AAA

X, Y

end component;

component BBB

port (

L, M

N

end component;

2016/3/23

X

X

Y

Z

F

AAA

U3 : AAA port map(C, D, F) ;

Digital Circuit IC Design

98

Architecture body

structure style of modeling 結構描述

library ieee;

use ieee.std_logic_1164.all ;

entity DECORDER2x4 is

port (

A, B, ENABLE

Z

);

end DECORDER2x4 ;

: in bit ;

: out bit_vector (3 downto 0)

-- (0 to 3)

A

B

DECODER2x4

ENABLE

Z(3)

Z(2)

Z(1)

Z(0)

P.S. -- 註解

2016/3/23

Digital Circuit IC Design

99

Architecture body

structure style of modeling 結構描述

architecture DEC_STR of DECORDER2x4 is

component INV

port ( PIN : in bit;

POUT : out bit );

end component;

component NAND3

硬體內部

port ( D0, D1, D2 : in bit;

元件的實

DZ

: out bit );

際接線

end component;

signal ABAR, BBAR : bit;

begin

I0 : INV port map (A, ABAR);

I1 : INV port map (B, BBAR);

N0 : NAND3 port map ( ENABLE, ABAR, BBAR, Z(0));

N1 : NAND3 port map (ABAR, B, ENABLE, Z(1));

N2 : NAND3 port map (A, BBAR, ENABLE, Z(2));

N3 : NAND3 port map (A, B, ENABLE, Z(3));

end DEC_STR ;

2016/3/23

Digital Circuit IC Design

100

訊號的連結 (1/2)

•

•

•

•

signal

signal

signal

Signal

Z : bit_vector (3 downto 0);

A : bit_vector (3 downto 0);

B : bit_vector (0 to 3);

O,P,Q,R : bit ;

• A <= Z;

Z(3)

Z(2)

Z(1)

Z(0)

B <= Z;

• A <= (O,P,Q,R);

O

P

Q

R

2016/3/23

Z(3)

Z(2)

Z(1)

Z(0)

A(3)

A(2)

A(1)

A(0)

or

A <= O&P&Q&R;

B(0)

B(1)

B(2)

B(3)

-- & 連結運算子

A(3)

A(2)

A(1)

A(0)

Digital Circuit IC Design

101

訊號的連結 (2/2)

•

•

•

•

signal

signal

signal

Signal

Z : bit_vector (3 downto 0);

A : bit_vector (3 downto 0);

B : bit_vector (0 to 3);

O,P,Q,R : bit ;

• Z <= A and B;

–

–

–

–

Z(3) <= A(3) and B(0) ;

Z(2) <= A(2) and B(1) ;

Z(1) <= A(1) and B(2) ;

Z(0) <= A(0) and B(3);

•

2016/3/23

Digital Circuit IC Design

102

Architecture body

structure style example 結構描述

keyin

clock

除10000

Disbounce

4-bit

Up counter

LED(3)

LED(2)

LED(1)

LED(0)

(O.S.C

10MHz)

2016/3/23

Digital Circuit IC Design

103

VHDL for LED example

library

use

ieee;

ieee.std_logic_1164.all;

entity LED_EXAMPLE is

port (

KEYIN, CLOCK : in bit;

LED

: out bit_vector(3 downto 0);

LED_COM

: out bit );

end LED_EXAMPLE;

architecture A_STRUCTURE of LED_EXAMPLE is

component

DIV10000

port (

CLKIN

CLKOUT

end component;

component

DISBOUNCE

port (

CLOCK, KEYIN

KEYOUT

end component;

component UP_CNT4

port (

CLK

QD

end component;

signal

CLK_DIV10000,

: in bit;

: out bit );

: in bit;

: out bit );

: in bit;

: out bit_vector(3 downto 0) );

KEY_DISBOUNCE

: bit ;

Begin

LED_COM <= ‘1’ ;

U1 : DIV10000

U2 : DISBOUNCE

U3 : UP_CNT4

port map (CLOCK, CLK_DIV10000);

port map (CLK_DIV10000, KEYIN, KEY_DISBOUNCE);

port map (KEY_DISBOUNCE, LED);

end A_STRUCTURE;

2016/3/23

Digital Circuit IC Design

104

Architecture body

• 結構描述 Structure Description

– As a set of interconnected components (to represent structure)

• 資料流描述 Data Flow Description

– As a set of concurrent assignment statements (to represent

dataflow)

• 行為描述 Behavior Description

– As a set of sequential assignment statements (to represent

behavior)

• As any of combination of the above three

2016/3/23

Digital Circuit IC Design

105

Architecture body

dataflow style of modeling

library ieee;

use

ieee.std_logic_1164.all;

entity HALF_ADDER is

port ( A, B

SUM, CARRY

end HALF_ADDER;

: in bit;

: out bit );

architecture HA_CONCURRENT of HALF_ADDER is

begin

SUM <= A xor B after 8 ns;

CARRY <= A and B after 4 ns;

end HA_CONCURRENT;

P.S.

2016/3/23

In a signal assignment statement, the symbol <= implies an assignment of a

value to a signal.

Delay information is included in the signal assignment statements used after

clause.

Digital Circuit IC Design

106

Simulation result of Half-Adder

A

B

CARRY

SUM

0

0

0

0

0

1

0

1

1

0

0

1

1

1

1

0

2016/3/23

Digital Circuit IC Design

107

邏輯運算子

• 七種邏輯運算子

–

–

–

–

AND / NAND

OR / NOR

XOR / XNOR

NOT

2016/3/23

Digital Circuit IC Design

108

Half / Full Adder

B

A

A

B

+

CARRY

Half Adder

SUM

CARRY

CARRY2

+

2016/3/23

SUM

Bi Ai

CARRY1

CARRY0

A2

A1

A0

B2

B1

B0

SUM2

SUM1

SUM0

Digital Circuit IC Design

CARRYi-1

Full Adder

CARRYi

SUMi

109

Simulation result of DECODER2x4

2016/3/23

Digital Circuit IC Design

110

Architecture body

dataflow style of modeling

architecture DEC_DATAFLOW of DECODER2x4 is

signal ABAR, BBAR : bit;

begin

ABAR <= not A;

BBAR <= not B;

Z(3) <= not (A and B and ENABLE);

Z(2) <= not (A and BBAR and ENABLE);

Z(1) <= not (ABAR and B and ENABLE);

Z(0) <= not (ABAR and BBAR and ENABLE);

end DEC_DATAFLOW ;

2016/3/23

Digital Circuit IC Design

111

Architecture body :

dataflow style of modeling

library ieee;

use ieee.std_logic_1164.all ;

entity DECORDER2x4 is

port (

A, B, ENABLE

Z

);

end DECORDER2x4 ;

: in bit ;

: out bit_vector (3 downto 0)

-- (0 to 3)

A

B

DECODER2x4

ENABLE

Z(3)

Z(2)

Z(1)

Z(0)

P.S. -- 註解

2016/3/23

Digital Circuit IC Design

112

TTL 74139 / 74138 decoder

解碼器

P.S. 必需使用

altera.maxplus.all 的 library

2016/3/23

Digital Circuit IC Design

113

Architecture body :

dataflow style example

VCC

DFF1

DFF2

Q0

CLOCK

Q1

KEYOUT

KEYIN

INV_KEY

2016/3/23

Digital Circuit IC Design

114

VHDL for disbounce circuit

定義 DFF

library

use

library

use

altera;

component

altera.maxplus2.all;

ieee;

ieee.std_logic_1164.all;

entity

DISBOUNCE is

port (

KEYIN, CLOCK

KEYOUT

);

end DISBOUNCE;

: in std_logic;

: out std_logic

architecture A of DISBOUNCE is

signal VCC, INV_KEY

: std_logic ;

signal Q0, Q1

: std_logic ;

begin

VCC <= '1' ;

INV_KEY <= not KEYIN ;

DFF1 : DFF port map (d =>VCC , q => Q0 , clk => CLOCK , clrn => INV_KEY , prn => VCC);

DFF2 : DFF port map (d =>VCC , q => Q1 , clk => CLOCK , clrn => Q0 , prn =>VCC);

KEYOUT <= not Q1 ;

end A;

2016/3/23

Digital Circuit IC Design

115

Architecture body :

dataflow style example

2016/3/23

Digital Circuit IC Design

116

Architecture body

• 結構描述 Structure Description

– As a set of interconnected components (to represent structure)

• 資料流描述 Data Flow Description

– As a set of concurrent assignment statements (to represent

dataflow)

• 行為描述 Behavior Description

– As a set of sequential assignment statements (to represent

behavior)

• As any of combination of the above three

2016/3/23

Digital Circuit IC Design

117

Architecture body

behavioral style of modeling

[label :] process (sensitivity list)

declaration part (before the keyword begin)

begin

statement part (between the keywords begin and end process)

end process [label] ;

P.S.

2016/3/23

(1) The behavior of an entity as a set of statements that are executed

sequentially in the specified order. This set of sequential statements,

which are specified inside a process statement.

(2) The process statement is invoked whenever there is an event on any

signal in the sensitivity list.

(3) The statements appearing within the process statement are executed

sequentially.

Digital Circuit IC Design

118

Architecture body

behavioral style of modeling

[process-label:] process [(sensitivity list)] [is]

[process-item-declaration]

begin

Sequential-statements; there are -->

variable-assignment-statement

signal-assignment-statement

wait-statement

if-statement

case-statement

loop-statement

null-statement

exit-statement

next-statement

assertion-statement

report-statement

procedure-statement

return-statement

end process [process-label];

2016/3/23

Digital Circuit IC Design

119

Architecture body

behavioral style of modeling

architecture DEC_SEQUENTIAL of DECORDER2x4 is

begin

process (A, B, ENABLE)

begin

if ENABLE = ‘1’ then

Z(0) <= not ((not B) and (not A) ) ; -- 00

Z(1) <= not ((not B) and A ) ;

-- 01

Z(2) <= not (B and (not A));

-- 10

Z(3) <= not (B and A);

-- 11

else

Z <= “1111”;

end if;

end process;

end DEC_SEQUENTIAL ;

2016/3/23

Digital Circuit IC Design

120

Architecture body

behavioral style of modeling

[process-label:] process [(sensitivity list)] [is]

[process-item-declaration]

begin

Sequential-statements; there are -->

variable-assignment-statement

signal-assignment-statement

wait-statement

if-statement

case-statement

loop-statement

null-statement

exit-statement

next-statement

assertion-statement

report-statement

procedure-statement

return-statement

end process [process-label];

2016/3/23

Digital Circuit IC Design

121

if statement

if (boolean-expression) then

sequential-statements

{ elsif (boolean-expression) then

sequential-statements }

[else

sequential-statements]

end if;

Ex:

if (X = ‘1’)

then

elsif (X=‘0’) then

else

end if;

2016/3/23

Y=A;

Y=B;

Y=C;

Digital Circuit IC Design

122

A level-sensitive flip-flop example

Type-D Flip Flop design

entity MY_DFF is

port ( CLK, D: in bit;

Q

: out bit );

end MY_DFF;

architecture ARCH_DFF of MY_DFF is

begin

Level-sensitive

process (CLK)

begin

if (CLK’event and CLK = ‘1’) then Q <= D;

end if ;

end process;

end ARCH_DFF ;

2016/3/23

Digital Circuit IC Design

123

Mod-10 up-counter

• level-trigger 準位觸發

– high-level trigger

• clk = ‘1’

– low-level trigger

• clk = ‘0’

• edge-trigger 邊緣觸發

– rising-edge (positive-edge) trigger 正緣觸發

• clk’event and clk=‘1’

– falling-edge (negative-edge) trigger負緣觸發

• clk’event and clk=‘0’

2016/3/23

Digital Circuit IC Design

124

A level-sensitive flip-flop example

Type-JK Flip Flop design

entity MY_JKFF is

port ( CLK, J, K, PRn, CLRn : in bit;

Q

: out bit );

end MY_JKFF;

architecture ARCH_DFF of MY_JKFF is

begin

Level-sensitive

process (CLK)

begin

if (CLK’event and CLK = ‘1’) then Q <= D;

end if ;

end process;

end ARCH_DFF ;

2016/3/23

Digital Circuit IC Design

125

Architecture body

mixed style of modeling

entity FULL_ADDER is

port ( A, B, CIN : in bit; SUM, COUT : out bit);

end FULL_ADDER;

architecture FA_MIXED of FULL_ADDER is

component XOR2

port (P1, P2 : in bit; PZ : out bit);

end component;

signal S1 : bit;

Begin

X1 : XOR2 port map (A, B, S1); -- structure

process (A, B, CIN)

-- behavior

variable T1, T2, T3 : bit;

begin

T1 := A and B;

T2 := B and CIN;

T3 := A and CIN;

COUT <= T1 or T2 or T3;

end process;

SUM <= S1 xor CIN;

-- dataflow

2016/3/23

Digital Circuit

IC Design

end LS_DFF ;

126

Mod-10 up-counter

•

•

•

•

•

•

•

library ieee;

use

ieee.std_logic_1164.all;

entity UP_CNT4 is

port(

CLK

: in bit;

Qd

: out integer range 0 to 9 );

end UP_CNT4;

CLK

•

architecture A of UP_CNT4 is

•

begin

•

-- An up counter

•

process (CLK)

•

variable CNT : integer range 0 to 9;

•

begin

•

if (CLK'event and CLK=’1’) then

•

if (CNT = 9) then

CNT := 0;

•

else

CNT := CNT + 1;

•

end if;

•

end if;

•

--Generate outputs

•

Qd <= CNT;

•

end process;

•

end A;

2016/3/23

Digital Circuit IC Design

UP_CNT4

Qd(3)

Qd(2)

Qd(1)

Qd(0)

127

Simulation result of Mod-10 up-counter

2016/3/23

Digital Circuit IC Design

128

wait until

process (CLK)

variable CNT : integer range 0 to 9;

begin

if (CNT = 9) then

CNT := 0;

else

CNT := CNT + 1;

end if;

Qd <= CNT;

wait until (CLK'event and CLK=’1’) ;

end process;

2016/3/23

Digital Circuit IC Design

129

除10電路

•

•

library ieee ;

use

ieee.std_logic_1164.all ;

DIV10

CLKIN

•

entity DIV10

is

•

port (

CLKIN

: in std_logic ;

•

CLKOUT : out std_logic );

•

end DIV10 ;

•

architecture A of DIV10 is

•

begin

•

process (CLKIN)

•

variable CNT1: integer range 0 to 4 ;

•

variable CNT2: std_logic ;

•

begin

•

if (CLKIN'event and CLKIN='1')

then

•

if (CNT1=4) then

CNT1:= 0 ;

•

CNT2 := not CNT2 ;

•

else

CNT1 := CNT1 +1 ;

•

end if ;

•

end if ;

•

CLKOUT <= CNT2 ;

•

end process ;

•

end A ;

2016/3/23

Digital Circuit IC Design

CLKOUT

130

除10電路 模擬結果

2016/3/23

Digital Circuit IC Design

131

除 10,000 電路

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

architecture A of MY_DIV10000 is

begin

process (CLKIN)

variable CNT1: integer range 0 to 9999 ;

variable CNT2: std_logic ;

begin

if (CLKIN'event and CLKIN='1') then

if (CNT1=9999) then

CNT1:= 0 ;

else

CNT1 := CNT1 +1 ;

end if ;

if (CNT1=5000 or CNT1=0) then

CNT2 := not CNT2;

end if;

end if ;

CLKOUT <= CNT2 ;

end process ;

end A ;

2016/3/23

Digital Circuit IC Design

132

除 10,000 電路

2016/3/23

Digital Circuit IC Design

133

除 5 電路

2016/3/23

Digital Circuit IC Design

134

exercise

• clear=‘0’ QD(7:0) = 0;

• load=‘1’ QD(7:0) = D(7:0)

• up_down ‘0’ : down counter

‘1’ : up counter

2016/3/23

Digital Circuit IC Design

135

Multi-features counter

ENTITY counters IS

PORT(

d

: IN INTEGER RANGE 0 TO 255;

clk : IN BIT;

clear : IN BIT;

load : IN BIT;

up_down : IN BIT;

qd

: OUT INTEGER RANGE 0 TO 255);

END counters;

ARCHITECTURE a OF counters IS

BEGIN

-- An up/down counter

PROCESS (clk)

VARIABLE cnt

: INTEGER RANGE 0 TO 255;

VARIABLE direction : INTEGER;

BEGIN

IF (up_down = '1') THEN --Generate up/down counter

direction := 1;

ELSE

direction := -1;

END IF;

IF (clk'EVENT AND clk = '1') THEN

IF (load = '1') THEN

--Generate loadable

cnt := d;

--counter. Take these

ELSE

--lines out to increase performance.

cnt := cnt + direction;

END IF;

--The following lines will produce a synchronous

--clear on the counter

IF (clear = '0') THEN

cnt := 0;

END IF;

END IF;

qd <= cnt; --Generate outputs

END PROCESS;

END a;

2016/3/23

Digital Circuit IC Design

136

七段顯示器

• CA : Common Anode, 共陽極

–

COM接VCC, low-active

• CC : Common Cathode, 共陰極

–

COM接GND, high-active

– P.S. 實驗板上的七段顯示器為共陰極。

2016/3/23

Digital Circuit IC Design

137

BCD to 7-segment driver circuit

Input

output

8

4

2

1

Dp

g

f

e

d

c

b

a

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

1

0

0

0

0

0

1

1

0

1

0

0

1

0

0

1

0

1

1

0

1

1

2

0

0

1

1

3

0

1

0

0

4

0

1

0

1

5

0

1

1

0

6

0

1

1

1

7

1

0

0

0

8

1

0

0

1

9

1

0

1

0

A

1

0

1

1

B

1

1

0

0

C

1

1

0

1

D

1

1

1

0

E

1 1 1 1

2016/3/23

DigitalFCircuit IC Design

SEG7

138

BCD to 7-segment driver circuit

SEG7

2016/3/23

Digital Circuit IC Design

139

VHDL for Truth Table

library ieee ;

use

ieee.std_logic_1164.all ;

entity SEG7 is

port ( DIN

: in std_logic_vector( 3 downto 0) ;

SEGOUT

: out std_logic_vector ( 6 downto 0) ) ;

end SEG7 ;

architecture SEG7_CC of SEG7 is

signal Q

: std_logic_vector ( 6 downto 0) ;

-=Q0=

high-active

-- Q5|

|Q1

-=Q6=

-- Q4|

|Q2

-=Q3=

begin

process (DIN)

begin

case DIN is

when "0000" =>

Q <= "0111111" ;

when "0001" =>

Q <= "0000110" ;

when "0010" =>

Q <= "1011011" ;

when "0011" =>

Q <= "1001111" ;

when "0100" =>

Q <= "1100110" ;

2016/3/23

Digital Circuit IC Design

-- 0

-- 1

-- 2

-- 3

-- 4

140

VHDL for Truth Table

when "0101" =>

when "0110" =>

when "0111" =>

when "1000" =>

when "1001" =>

when "1010" =>

when "1011" =>

when "1100" =>

when "1101" =>

when "1110" =>

when "1111" =>

when OTHERS =>

end case;

end process;

SEGOUT <= Q ;

end SEG7_CC ;

2016/3/23

Q <= "1101101" ;

Q <= "1111101" ;

Q <= "0000111" ;

Q <= "1111111" ;

Q <= "1101111" ;

Q <= "1110111" ;

Q <= "1111100" ;

Q <= "0111001" ;

Q <= "1011110" ;

Q <= "1111001" ;

Q <= "1110001" ;

Q <= "0000000" ;

Digital Circuit IC Design

-- 5

-- 6

-- 7

-- 8

-- 9

-- A

-- B

-- C

-- D

-- E

-- F

--very important

141

case syntax (1)

case 物件 is

when

數值1

when

數值1

when

數值1

...

when others

end case

2016/3/23

=>

=>

=>

敘述1

敘述2

敘述3

=>

其他敘述

Digital Circuit IC Design

142

case syntax (2)

process (A, B, C, X)

begin

case X is

when

0 to 4

=>

when 5

=>

when

7 | 9

when others

end case

end process

2016/3/23

Digital Circuit IC Design

Z <= A ;

Z <= B ;

=>

Z <= C ;

=>

Z <= 0 ;

143

with … select… when syntax (1)

with

物件 is

when

數值1

when

數值1

when

數值1

...

when others

end case

2016/3/23

=>

=>

=>

敘述1

敘述2

敘述3

=>

其他敘述

Digital Circuit IC Design

144

case syntax (1)

with 選擇訊號 select

訊號 X <= 訊號 A when

訊號 A when

選擇訊號的值為P,

選擇訊號的值為P,

訊號 A when 選擇訊號的值為P,

when

數值1

when

數值1

...

when others

end case

2016/3/23

=>

=>

敘述2

敘述3

=>

其他敘述

Digital Circuit IC Design

145

一位數七段顯示器顯示

div1000

disbounce

UP_CNT4

SEG7

共陰極

COM

2016/3/23

Digital Circuit IC Design

146

一位數七段顯示器顯示

OSC

SW1

CLOCK

KEYIN

A

B

C

D

E

F

G

dp

COM

COM

COM

DE1

DE2

DE3

pin assignment

A B C D E F G dp DE1 DE2 DE3

23 26 27 28 29 30 31 32 33 36 37

2016/3/23

OSC SW1

Digital Circuit IC Design

55

47

147

Function of 74138

3-8 decoder

Input

2016/3/23

output

C

B

A

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

0

0

0

0

1

1

1

1

1

1

1

0

0

1

1

0

1

1

1

1

1

1

0

1

0

1

1

0

1

1

1

1

1

0

1

1

1

1

1

0

1

1

1

1

1

0

0

1

1

1

1

0

1

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

0

Digital Circuit IC Design

148

多工器 Multiplex (MUX)

MUX 2x1

•

•

•

-- 2 to 1 multiplex

library ieee;

use

ieee.std_logic_1164.all;

•

•

•

•

entity MUX2x1 is

port (

A, B, SEL

Y

end MUX2x1;

•

•

•

•

•

•

•

•

•

Architecture MUX2x1 of MUX2x1 is

begin

mux : process(A, B, SEL)

begin

if SEL=‘0‘ then

Y <= A;

else

Y <= B;

end if;

end process mux;

end MUX2x1 ;

2016/3/23

: in std_logic;

: out std_logic );

Digital Circuit IC Design

A

Y

B

SEL

149

Simulation result of MUX2x1

2016/3/23

Digital Circuit IC Design

150

when…else

MUX 2x1

library ieee ;

use ieee.std_logic_1164.all ;

entity

MUX2x1 is

port

(

A, B, SEL

Y

);

end MUX2x1 ;

A

Y

B

: in std_logic ;

: out std_logic

SEL

architecture

MUX of MUX2x1 is

begin

Y <= A when SEL='0' else

B;

end MUX ;

2016/3/23

Digital Circuit IC Design

151

VHDL syntax

when…else

• 單行敘述

訊號 Y <= 訊號 A when 條件 else 訊號 B;

• 多行敘述

訊號 Y <= 訊號 A when 條件 1 else

訊號 B when 條件 2 else

׃

訊號 E when 條件 5 else

訊號 F ;

2016/3/23

Digital Circuit IC Design

152

truth table

MUX 2x1

Input

2016/3/23

Output

A

B

SEL

Y

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

1

1

0

1

0

1

1

0

1

1

1

1

1

Digital Circuit IC Design

153

when…else

MUX 4x1

library ieee;

use ieee.std_logic_1164.all;

entity MUX4x1 is

port( A, B, C, D

S

Y

end MUX4x1 ;

: in std_logic ;

: in integer range 0 to 3 ;

: out std_logic ) ;

architecture MUX of MUX4x1 is

begin

Y <= A when S=0 else

B when S=1 else

C when S=2 else

D when S=3 ;

end MUX ;

2016/3/23

Digital Circuit IC Design

A

B

C

D

Y

S

154

if…elsif…else

MUX 4x1

library ieee;

use ieee.std_logic_1164.all;

entity

MUX4x1 is

port ( d

: in std_logic_vector(3 downto 0);

sel

: in integer range 0 to 3;

y

: out std_logic );

end

MUX4x1;

architecture

A of MUX4x1

begin

process (d, sel)

begin

if

sel = 0 then

elsif

sel = 1 then

elsif

sel = 2 then

else

end if;

end process;

end A;

2016/3/23

is

y <= d(0);

y <= d(1);

y <= d(2);

y <= d(3);

Digital Circuit IC Design

155

Simulation of MUX4x1

2016/3/23

Digital Circuit IC Design

156

Behavior description (case…when)

MUX 4x1

library ieee;

use ieee.std_logic_1164.all;

entity

MUX4x1 is

port ( d

: in std_logic_vector(3 downto 0);

sel

: in integer range 0 to 3;

y

: out std_logic );

end

MUX4x1;

architecture

A of

begin

process (sel)

begin

case sel is

when

when

when

when

end case;

end process;

end

A;

2016/3/23

MUX4x1 is

0

1

2

3

=>

=>

=>

=>

y <= d(0);

y <= d(1);

y <= d(2);

y <= d(3);

Digital Circuit IC Design

157

Architecture body

behavioral style of modeling

[process-label:] process [(sensitivity list)] [is]

[process-item-declaration]

begin

Sequential-statements; there are -->

variable-assignment-statement

signal-assignment-statement

wait-statement

if-statement

case-statement

loop-statement

null-statement

exit-statement

next-statement

assertion-statement

report-statement

procedure-statement

return-statement

end process [process-label];

2016/3/23

Digital Circuit IC Design

158

VHDL syntax

when…else

case 物件 is

when

數值1

when

數值2

…..

when others

end case ;

2016/3/23

=>

=>

statement 1;

statement 2;

=>

statement N;

Digital Circuit IC Design

159

case statement

case expression is

when choices => sequential-statements

when choices => sequential-statements

-- can have any number of branchs.

[ when others => sequential-statements ]

end case;

2016/3/23

Digital Circuit IC Design

-- branch #1

-- branch #2

-- last branch

160

Interconnect components

MUX 4x1 (interconneted components)

A

E

B

S(0)

Y

F

C

S(1)

D

S(0)

2016/3/23

Digital Circuit IC Design

161

Interconnect components

MUX 4x1

library ieee;

use

ieee.std_logic_1164.all ;

entity MUX4x1 is

port( A, B, C, D

S

Y

end MUX4x1 ;

: in std_logic ;

: in std_logic_vector(1 downto 0);

: out std_logic ) ;

architecture a of MUX4x1 is

COMPONENT mux2x1

port(

A, B ,S : in std_logic;

Y

: out std_logic );

end COMPONENT;

SIGNAL

E, F : std_logic ;

begin

C1 : mux2x1 port map (A => A, B => B, S => S(0), Y => E );

C2 : mux2x1 port map (A => C, B => D, S => S(0), Y => F );

C3 : mux2x1 port map (A => E, B => F, S => S(1), Y => Y );

end

a;

2016/3/23

Digital Circuit IC Design

162

when…else

MUX 2x1Bus

library ieee ;

use ieee.std_logic_1164.all ;

entity MUX2x1Bus is

port

(

A, B

SEL

Y

);

end MUX2x1Bus ;

: in std_logic_vector(3 downto 0);

: in std_logic ;

: out std_logic_vector(3 downto 0)

architecture

MUX of MUX2x1Bus is

begin

Y <= A when SEL='0' else

B;

end MUX ;

2016/3/23

Digital Circuit IC Design

163

Simulation result of MUX 2x1 (Bus)

MUX 2x1Bus

2016/3/23

Digital Circuit IC Design

164

2-digit 7-segment display experience

O.S.C.

10MHz

按鍵

除頻

disbounce

Mod-10

up counter

MUX

Mod-10

up counter

2016/3/23

Digital Circuit IC Design

7-seg

COM

COM

165

PWM (Pulse Width Modulation)

比較器

library ieee ;

use ieee.std_logic_1164.all ;

entity COMPARATOR is

port( A,B

: in std_logic_vector(3 downto 0);

less

: out std_logic );

end COMPARATOR ;

architecture A of COMPARATOR is

begin

process(A, B)

begin

if A<B then

less <= '1';

else

less <= '0';

end if;

end process;

end A ;

2016/3/23

Digital Circuit IC Design

166

PWM (Pulse Width Modulation)

simulation result of comparator

2016/3/23

Digital Circuit IC Design

167

PWM (Pulse Width Modulation)

driver circuit

DC 72V

Motor

2016/3/23

Digital Circuit IC Design

168

PWM (Pulse Width Modulation)

duty-cycle

duty-cycle : 責任週期,在一個週期內,訊號ON的比率。

ON的時間越長,馬達轉速越快;約成正比。

PWM : Pulse Width Modulation,脈波寬度調變。

2016/3/23

Digital Circuit IC Design

169

PWM (Pulse Width Modulation)

直流馬達驅動電路

160KHz

clock

PWM

duty-cycle

setting

2016/3/23

up_cnt4

comparator

4-bit mod-16

Up-counter

range 0 to 15

10KHz

PWM wave

4-bit

comparator

Digital Circuit IC Design

170

PWM (Pulse Width Modulation)

直流馬達PWM控制電路

•

architecture A of PWM_DRIVER is

component up_cnt4

port ( clk

: in std_logic;

Qd

: out std_logic_vector(3 downto 0);

end component;

component comparator

port ( A,B

: in std_logic_vector(3 downto 0);

less

: out std_logic);

end component;

signal

counter : integer range 0 to 15;

begin

X1 : up_cnt4 port map (clk=>clock, Qd=>counter);

A1 : comparator port map (A=>counter, B=>setting, less=>PWM);

end A ;

2016/3/23

Digital Circuit IC Design

171

PWM (Pulse Width Modulation)

driver circuit

DC 72V

PWM+

PWM-

Motor

PWM-

2016/3/23

PWM+

Digital Circuit IC Design

172

Finite State Machine(狀態機)

分類(Moore and Mealy)

2016/3/23

Digital Circuit IC Design

173

Finite State Machine(狀態機)

設計步驟

• Step 1 : 在VHDL中宣告一個列舉(enumeration)型態來

當作狀態向量,宣告狀態機中有幾個狀態。

• Step 2 : 將狀態機的VHDL描述成二個process敘述,一

個是組合邏輯敘述,另一個是循序邏輯敘述。

• Step 3 : 在狀態機中指定一個預設的狀態,因為假如沒

有任何狀態被啟動,我們可以直接進入idle狀

態。

2016/3/23

Digital Circuit IC Design

174

Enumeration types

An enumeration type declaration defines a type that has a

set of user-defined values consisting of identifiers and

character literals.

examples :

type MVL is (‘U’, ‘0’, ‘1’, ‘Z’);

type MICRO_OP is (load, store, add, sub, mul, div);

subtype ARITH_OP is range add to div;

signal CLOCK : MVL range ‘0’ to ‘1’;

2016/3/23

Digital Circuit IC Design

175

Finite State Machine (狀態機)

Moore狀態機 example-1

ena=0

ena=0

S0

Y=0

ena=1

S1

Y=0

ena=1

ena=1

ena=0

ena=0

S3

Y=1

2016/3/23

ena=1

S2

Y=0

Digital Circuit IC Design

176

Finite State Machine (狀態機)

Moore狀態機 example-1

architecture A of FSM is

type state is (S0, S1, S2, S3);

signal

present_state, next_state

: state;

begin

sync : process(clk)

begin

if clk’event and clk=‘1’ then

present_state <= next_state;

end if;

end process sync;

comb : process(ena, present_state)

begin

case present_state is

when S0 =>

if ena=‘0’ then

else

end if;

Y <= ‘0’;

2016/3/23

Digital Circuit IC Design

next_state <= S0;

next_state <= S1;

177

Finite State Machine (狀態機)

Moore狀態機 example-1

when S1 =>

when S2 =>

when S3 =>

if ena=‘0’ then

else

end if;

Y <= ‘0’;

if ena=‘0’ then

else

end if;

Y <= ‘0’;

if ena=‘0’ then

else

end if;

Y <= ‘1’;

next_state <= S1;

next_state <= S2;

next_state <= S2;

next_state <= S3;

next_state <= S3;

next_state <= S0;

end case;

end process comb;

end A;

2016/3/23

Digital Circuit IC Design

178

Finite State Machine (狀態機)

Moore狀態機 example-2

U_d =0

ena=1

S0

Y=0

U_d =0

U_d =1

U_d =1

S1

Y=0

U_d =1

U_d =0

U_d =1

S3

Y=1

2016/3/23

U_d =0

S2

Y=0

Digital Circuit IC Design

179

Finite State Machine (狀態機)

Moore狀態機 example-2

architecture A of FSM is

type state is (S0, S1, S2, S3);

signal

present_state, next_state

: state;

begin

sync : process(clk)

begin

if clk’event and clk=‘1’ then

present_state <= next_state;

end if;

end process sync;

comb : process(ena, present_state)

begin

case present_state is

when S0 =>

if u_d=‘0’ then

else

end if;

Y <= ‘0’;

2016/3/23

Digital Circuit IC Design

next_state <= S1;

next_state <= S3;

180

Finite State Machine (狀態機)

Moore狀態機 example-2

when S1 =>

when S2 =>

when S3 =>

if u_d=‘0’ then

else

end if;

Y <= ‘0’;

if u_d=‘0’ then

else

end if;

Y <= ‘0’;

if u_d=‘0’ then

else

end if;

Y <= ‘1’;

next_state <= S2;

next_state <= S0;

next_state <= S3;

next_state <= S1;

next_state <= S0;

next_state <= S2;

end case;

end process comb;

end A;

2016/3/23

Digital Circuit IC Design

181

Finite State Machine (狀態機)

Moore狀態機 mod-10 up/down counter

updown=‘0’

S0

Q=0000

S9

Q=1001

updown=‘1’

S1

Q=0001

S8

Q=1000

S2

Q=0010

S7

Q=0111

S3

Q=0011

S6

Q=0110

S4

Q=0100

S5

Q=0101

2016/3/23

Digital Circuit IC Design

182

Finite State Machine (狀態機)

Moore狀態機 mod-10 up/down counter

library ieee;

use ieee.std_logic_1164.all;

entity

mod10_updown_counter is

port( updown

: in bit;

clk

: in bit;

Q

: out bit_vector(3 downto 0) );

end mod10_updown_counter;

architecture A of mod10_updown_counter is

type state is (S0,S1,S2,S3,S4,S5,S6,S7,S8,S9);

signal present_state, next_state

: state;

begin

sync : process(clk)

begin

if clk'event and clk='1' then

present_state <= next_state;

end if;

end process sync;

2016/3/23

Digital Circuit IC Design

183

Finite State Machine (狀態機)

Moore狀態機 mod-10 up/down counter

comb : process(updown, present_state)

begin

case present_state is

when S0 =>

if updown='0'

then

else

end if;

Q <= "0000";

when S1 =>

if updown='0'

then

else

end if;

Q <= "0001";

when S2 =>

if updown='0'

then

else

end if;

Q <= "0010";

when S3 =>

if updown='0'

then

else

end if;

Q <= "0011";

when S4 =>

if updown='0'

then

else

end if;

2016/3/23

Circuit IC Design

Q <=Digital

"0100";

next_state <= S1;

next_state <= S9;

next_state <= S2;

next_state <= S0;

next_state <= S3;

next_state <= S1;

next_state <= S4;

next_state <= S2;

next_state <= S5;

next_state <= S3;

184

Finite State Machine (狀態機)

Moore狀態機 mod-10 up/down counter

when S5 =>

when S6 =>

when S7 =>

when S8 =>

when S9 =>

end case;

end process comb;

2016/3/23

end

A;

if updown='0'

else

end if;

Q <= "0101";

if updown='0'

else

end if;

Q <= "0110";

if updown='0'

else

end if;

Q <= "0111";

if updown='0'

else

end if;

Q <= "1000";

if updown='0'

else

end if;

Q <= "1001";

then

next_state <= S6;

next_state <= S4;

then

next_state <= S7;

next_state <= S5;

then

next_state <= S8;

next_state <= S6;

then

next_state <= S9;

next_state <= S7;

then

next_state <= S0;

next_state <= S8;

Digital Circuit IC Design

185

Finite State Machine (狀態機)

Moore狀態機 mod-10 up/down counter

2016/3/23

Digital Circuit IC Design

186

Finite State Machine (狀態機)

Mealy狀態機 example

ena=0 / Y=0

ena=0 / Y=0

S0

ena=1 / Y=0

S1

ena=1 / Y=1

ena=1 / Y=0

ena=0 / Y=0

ena=0 / Y=0

ena=1 / Y=0

S3

2016/3/23

S2

Digital Circuit IC Design

187

Finite State Machine (狀態機)

Mealy狀態機 example

architecture A of FSM is

type state is (S0, S1, S2, S3);

signal

present_state, next_state

begin

sync : process(clk)

begin

if clk’event and clk=‘1’ then

present_state <= next_state;

end if;

end process sync;

comb : process(ena, present_state)

begin

case present_state is

when S0 =>

if ena=‘0’ then

else

: state;

next_state <= S0;

Y<=‘0’;

next_state <= S1;

Y<=‘0’;

end if;

2016/3/23

Digital Circuit IC Design

188

Finite State Machine (狀態機)

Mealy狀態機 example

when S1 =>

if ena=‘0’ then

else

when S2 =>

end if;

if ena=‘0’ then

else

when S3 =>

end if;

if ena=‘0’ then

else

next_state <= S1;

Y <= ‘0’;

next_state <= S2;

Y <= ‘0’;

next_state <= S2;

Y <= ‘0’;

next_state <= S3;

Y <= ‘0’;

next_state <= S3;

Y <= ‘0’;

next_state <= S0;

Y <= ‘1’;

end if;

end case;

end process comb;

end A;

2016/3/23

Digital Circuit IC Design

189

Example of FSM application

Traffic light control

NG NY NR

EG EY ER

S0

Q=001 100

NG NY NR

S1

Q=001 010

ER

EY

S3

Q=001 001

EG

S4

Q=100 001

S5

Q=010 001

2016/3/23

S6

Q=001 001

Digital Circuit IC Design

190

Example of FSM application

Traffic light control

For the clock of FSM :

2016/3/23

Digital Circuit IC Design

191

Example of FSM application

步進馬達(stepping motor)

2016/3/23

Digital Circuit IC Design

192

Example of FSM application

driver circuit of stepping motor

激磁訊號

2016/3/23

A

Ā

B

B

Digital Circuit IC Design

193

Example of FSM application

stepping motor激磁方法

1 2 3 4 1 2 3 4

2016/3/23

1相激磁時序圖

2相激磁時序圖

每次會1個線圈通過電流,因此轉矩小

、振動較大,消耗電力小。

每次使2個線圈激磁,因此轉矩大

、振動小,是目前使用最多的方式。

Digital Circuit IC Design

194

Application example --- Stepping motor

激磁方法

1 2 3 4 5 6 7 8 1 2 3

1-2相激磁(半步激磁)時序圖

使1相和2相輪流激磁,因此解析度提高一倍,且運轉平順。

2016/3/23

Digital Circuit IC Design

195

Application example --- Stepping motor

2相激磁方法

Output = ABĀB

1 2 3 4

S0

Y=1100

S3

Y=1001

S1

Y=0110

S2

Y=0011

2016/3/23

Digital Circuit IC Design

196

Example of FSM application

Keypad scan circuit

row0

row1

row2

row3

col0

col1

col2

col3

2016/3/23

Digital Circuit IC Design

197

Example of FSM application

Keypad scan circuit

2016/3/23

1

1

1

0

C1

1

1

0

1

C2

1

0

1

1

C3

0

1

1

1

C4

Digital Circuit IC Design

198

Example of FSM application

Keypad scan circuit

Keypad scan

circuit

clk

4KHz

2016/3/23

Output = C1 C2 C3 C4

C1

C2

C3

C4

S0

Y=0111

1KHz

1

1

1

0

C1

1

1

0

1

C2

1

0

1

1

C3

0

1

1

1

C4

S3

Y=1110

Digital Circuit IC Design

S1

Y=1011

S2

Y=1101

199

Example of FSM application

Keypad scan circuit

Output = C B A

C1

C2

C3

C4

Keypad scan

circuit

(no 74138)

C

Keypad scan

circuit

(with 74138)

2016/3/23

B

A

S0

Y=000

S3

Y=011

74138

C

B

A

Y0

Y1

Y2

Y4

C1

C2

C3

C4

Digital Circuit IC Design

S1

Y=001

S2

Y=010

200

Example of FSM application

Keypad scan circuit

RK3

RK2

RK1

Keypad

detection

circuit

74138

Keypad scan

circuit

2016/3/23

C

B

A

Y0

Y1

Y2

Y4

C1

C2

C3

C4

Digital Circuit IC Design

201

Example of FSM application

Keypad scan circuit

Keypad

detection

circuit

7-seg

decoder

A

B

C

Input

2016/3/23

RK3

RK2

RK1

output

C

B

A

RK3

RK2

RK1

Q3

Q2

Q1

Q0

KeyPressed

0

0

0

1

1

0

‘1’

0

0

0

1

1

0

0

0

1

0

1

‘2’

0

0

1

0

1

0

0

0

0

1

1

‘3’

0

0

1

1

1

0

0

0

1

1

1

No key

0

0

0

0

1

0

0

‘1’ & ‘2’

0

0

0

1

1

1

0

‘4’

0

1

0

0

1

0

0

1

1

0

1

‘5’

0

1

0

1

1

Digital Circuit IC Design

202

8x8 點矩陣雙色LED

2016/3/23

Digital Circuit IC Design

203

8x8 點矩陣雙色LED

2016/3/23

Digital Circuit IC Design

204

8x8 點矩陣雙色LED

2016/3/23

Digital Circuit IC Design

205

8x8 點矩陣雙色LED

row (列) driver circuit (commom anode)

2016/3/23

Digital Circuit IC Design

206

8x8 點矩陣雙色LED

column (行) driver circuit (high-active)

2016/3/23

Digital Circuit IC Design

207

2016/3/23

Digital Circuit IC Design

208

Programming circuit

2016/3/23

Digital Circuit IC Design

209