Final Exam Review - CS Course Webpages

advertisement

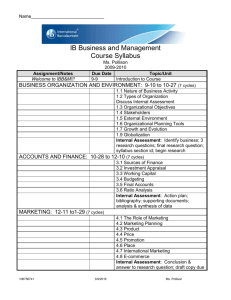

Final Exam Review Homework Notes • Pay attention to significant digits • Should not have more significant digits in answer than in problem • Example: HW1 #1.1 • 90% yield (1 significant digit), 80% fault coverage (1 significant digit), DPM = 20,000 or maybe 21,000, not 20,851.638! • Provide answers, not data dumps • Answers in HW3 problems 1 and 2 were far longer than necessary, correct, but unnecessary • Example: • Question: Explain how SCOAP metrics are related to combinational and sequential testability. • Key part of answer: Combinational SCOAP is roughly related to the number of necessary assignments for the test, and sequential scope is related to the number of time frames to sensitize and propagate the fault. A data dump on all SCOAP detail is not necessary. Homework Notes • Pay attention to what question is asked • Example: HW3 #3 • Question: What is the drawback of time-domain expansion for sequential ATPG of deeply sequential circuits? • The question is not asking about the difficulty of testing deeply sequential circuits (that is hard), or whether they are acyclic or cyclic, or have a reset state, but of using time-frame expansion for sequential test. • Obvious issues: 1) large numbers of time frames and large amounts of memory are required; 2) large state space to search; 3) large number of inputs (inputs in each time frame); 4) need to avoid fault site when sensitizing and propagating. • Many missed the issue of the size of the circuit representation. Remember my example of a testing a SA0 on the MSB of a 32bit counter. Homework Notes • Problem 1.11: How many mandatory and optional pins are required for IEEE 1500? • 8 mandatory – WSI, WSO, WRCK, WRSTN, SelectWIR, CaptureWR, ShiftWR • Optional – TransferDR, AUXCKn, WPI, WPC, WPO • It is IEEE 1149.1 that has 4 required pins – TCK, TMS, TDI, TDO, and optional TRST* Homework Notes • Question 2.18(c): How many errors can be detected by the X-compactor? • Solution: Theorem 2.2 • Errors from 1, 2, or odd # of scan chains at the same scan-out cycle are guaranteed to produce errors if every row of the matrix is non-zero, distinct and contains an odd number of 1s. • True for this matrix • Total errors = C(8,1)+C(8,2)+C(8,3)+C(8,5)+C(8,7) = 156 • Looking at columns in matrix gets 8x3 = 24, but ignores combinations • At most 7 faulty scan chains can be detected in one cycle • Over multiple cycles, an infinite number of faults can be detected Final Exam 2013 • More up-to-date on coverage than practice exams Question 1 • In a regular SOC, a TAM is used to deliver test patterns and collect test results from the cores. Suppose you have a TAM that has 10 data lines, and all cores have MISRs so that test results do not have to be read while the test patterns are delivered. We will ignore the time to read back the MISRs. Consider an SOC with 4 cores. Core 1 has test patterns that can be delivered on 3 lines in 10000 cycles with 400 mW power dissipation, 6 lines in 5000 cycles and 750 mW, or 10 lines in 3000 cycles and 1000 mW. Core 2 has test patterns that can be delivered on 3 lines in 20000 cycles and 300 mW, 4 lines in 15000 cycles and 400 mW or 5 lines in 12000 cycles and 500 mW. Cores 3 and 4 each have test patterns that can be delivered on 2 lines in 20000 cycles and 300 mW or 4 lines in 10000 cycles and 600 mW. Question 1(a) • (10 pts) Draw the shortest test schedule you can find. What is the maximum power dissipation during this schedule? • Solution 1: Test core 1 with 6 lines in 5k cycles, then core 2 with 5 lines in 12k cycles, so 17k cycles total. At the same time test core 3 and core 4 with 2 lines in 20k cycles, so the total time is 20k cycles. So using initially 9 lines for 5k cycles, then 9 lines for 12k cycles, then 4 lines for 3k cycles. This uses a peak power of 750mW + 300mW + 300mW = 1350mW, which drops to 500mW + 300mW + 300mW = 1100mW. • Solution 2: Test core 1 with 3 lines in 10k cycles, core 2 with 3 lines in 20k cycles, core 3 and 4 with 2 lines each and 20k cycles. So total time is 20k cycles, with peak power of 400mW+300mW+300mW+300mW = 1600mW. • Note that we are assuming that you cannot vary the number of TAM wires used by a core during the test, since not enough information has been given to assume the transitions between the number of TAM wires (e.g. is the total number of bits conserved). Question 1(b) • (10 pts) Draw the shortest test schedule you can find that dissipates no more than 1000 mW. • Solution 1: Test core 1 with 10 lines for 3k cycles @ 1000 mW, then core 2 with 3 lines and 20k cycles @ 300mW, and cores 3 and 4 with 2 lines and 20k cycles @ 300 mW. So total time is 23k cycles. Power is 1000 mW for the first 3k cycles, then 300mW+300mW+300mW = 900mW for the next 20k cycles. • Solution 2: Test core 3 with 4 lines and 10k cycles @ 600mW and then core 4 with 4 lines and 10k cycles @ 600mW, while at the same time test core 2 with 3 lines and 20k cycles @ 300mW. Then test core 1 with 10 lines and 3k cycles @ 1000mW. So total time is 23k cycles. The power is 900mW for the first 20k cycles, then 1000mW for the last 3k cycles. • There are other 23k cycle schedules. Question 2(a) • (10 pts) In the figure below, show the test for a SA0 on the output of gate 11 that will be generated by the PODEM algorithm. Write on the figure and explain the sequence of decisions. • Combinational controllability values shown on relevant parts of the circuit. To set 1 on G11, set 1 on G9 since has lower CC1, then set 1 on inputs of G9, set 0 on input of G8, which propagates a 1 on G7, which is consistent. Therefore C=0 and the test is generated. Question 2(b) • (5 pts) List the stuck-at faults (e.g. gate 1 SA0, gate 2 SA1,…) that are fortuitously detected by the resulting test. Assume an X value does not sensitize or propagate a fault. • The output of G6 is an X. Normally that means the output of G10 is an X, so SA1 on C, SA0 on G7, SA0 on G8, and SA0 on G9 cannot be detected, using the D algebra. However, if there is a SA0 on G7, then both G9 and G10 will be 0, so G11 will be 0, in contrast to the fault-free value of 1. So the SA0 on G7 will be detected. (4,2) (1,1) (5,5) (5,5) (2,3) (1,1) (6,8) (7,2) SA0 (7,2) (1,1) (1,1) 1 1 (4,2) 1 (1,1) (2,2) 0 (1,1) (3,5) 1 (10,6) Question 3 • (15 pts) For the circuit below, FFs 7 and 8 are connected together in a scan chain (the scan chain is from 7 to 8). Their D inputs can be directly observed as PPOs. FF outputs Q1 and Q2 are PPIs. You wish to generate a launch-on-capture test to detect a slow-to-rise (STR) transition fault on Z. We assume Z can be directly observed by a tester. What scan pattern (each bit is 0, 1, or X) and value on R (0, 1, X, the value is not allowed to change) will detect the TF? Draw on the diagram as necessary to explain your answer. For example, you can show 0 → 1 for a 0 to 1 transition on a line. If the STR fault on Z is untestable, explain where the conflict is located. Extra copies of the circuit are attached to work out your solution. 0 0 1→0 0→1 0→1 0→1 STR 0→1 0→1 1 1 0→1 0 0 1→0 1→0 0→1 1 Detecting a STR on Z requires a 0 → 1 on G5. Working backwards, this requires R=0, Q1=0 and Q2=1. Question 4 • (5 pts) What is the basic idea of testing a source synchronous high-speed I/O? • In a source synchronous I/O, the signal and clock both come from the output, and then drive a flipflop at the receiver. To test it, the clock can be skewed early or late relative to the data, to verify that the flip-flop setup and hold times will be met given jitter between the clock and data. Question 5 • (10 pts) In time frame expansion in sequential testing, we “unroll” the circuit in time. Show this for the circuit in Problem 3, for 2 time frames. Assume there is a SA0 fault on the output of gate 1. SA0 SA0 Question 6 • (10 pts) Consider an embedded core with 8 functional inputs a[0:7], 11 functional outputs z[0:10], 9 internal scan chains of lengths 12, 12, 8, 8, 8, 6, 6, 6 and 6 scan cells each, and a scan enable SE. The test wrapper for the core will be connected to two TAMs – a 4-bit TAM and a 6-bit TAM. A signal c selects between them. Present a table for each TAM. In each table, for each wrapper scan chain, list the scan chains (# scan cells), wrapper input cells (# cells), wrapper output cells (# cells) that are included, along with its scan-in length (excludes wrapper outputs), and scan-out length (excludes wrapper inputs). What is the speedup in test time by using the 6-bit TAM instead of the 4-bit TAM? • Using TAM4, in the worst case we need 20+21 = 41 cycles to scan in the input and scan out the results. Using TAM6, in the worst case we need 14+14 = 28 cycles to scan in the input and scan out the results. The speedup by using TAM6 is 41/28 = 1.46x. Scan chains # input cells 1 12+8 =20 0 TAM4 2 3 12+8 8+6 =20 =14 0 6 4 6+6+6 =18 2 1 12 2 12 0 0 TAM6 3 4 8+6 8+6 =14 =14 0 0 5 8+6 =14 0 6 6 8 # output cells 0 1 7 3 2 1 0 0 0 8 Scan-in length 20 20 20 20 12 12 14 14 14 14 Scan-out length 20 21 21 21 14 13 14 14 14 14 Question 7 • (5 pts) How can one assign values to don’t care (X) bits in a scan pattern to reduce power dissipation during scan testing? • If we copy the previous bit in the chain, known as adjacent filling, then the scan chain shift will only produce transitions where bits are changing from 0 to 1 or 1 to 0. Since the typical pattern has only about 1% care bits, then only about 1% of the scan cells will generate an input transition on each shift. • Example: 101XXXX0110XXX 10111110110000 – 5 transitions per shift • For capture cycles, we can attempt to fill the X bits so that they have the same value on launch and capture. Question 8 • (5 pts) Why is it easier to detect bridging faults with IDDQ test instead of detecting erroneous logic values? • IDDQ provides 100% observability if the bridged fault has a 0-1 or 1-0 across it. There is no need to propagate the value to an output, so no need to set necessary assignments for observability. It is only necessary to set the 0-1 or 1-0 sensitization. This means that more faults can be detected per pattern. • Another interpretation is that it can detect bridges that do not cause a logic fault. These might be delay faults or IDDQ-only failures. Question 9 • (5 pts) What is the key assumption we usually make about failures when building fault-tolerant systems? • We assume a single fault in the system. For example, triple modular redundancy will always correct any single fault, but cannot handle more than one. • We also assume that the faults are independent. Question 10 • (5 pts) How do X values on a circuit output cause problems in logic BIST? • If using a MISR on the output, each captured X means the MISR could be in two possible states, so for n X outputs, the MISR could be in 2n states, and one of those states could alias to the fault-free state. Question 11 • (5 pts) What is the basic idea in using BIST to test reconfigurable FPGAs? • We can have the FPGA test itself. Some logic blocks can be configured as LFSRs and others as MISRs, to test the logic or the interconnect in between. The configuration is changed to move the LFSRs and MISRs around and their connectivity to test everything.