EE 5342 Lecture - The University of Texas at Arlington

advertisement

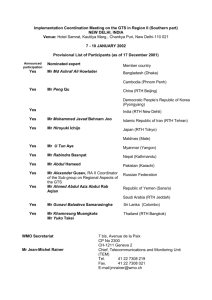

Semiconductor Device Modeling and Characterization – EE5342 Lecture 37 – Spring 2011 Professor Ronald L. Carter ronc@uta.edu http://www.uta.edu/ronc/ SPICE mosfet Model Instance CARM*, Ch. 4, p. 290 M MOSFET General Form M<nam e> < drain node> <gate node> < source node> + <bulk /subs trate node> <model nam e> + [L=< value>] [W=< value> ] L = Ch. L. [m] + [AD= <value>] [AS= <value>] W = Ch. W. [m] + [PD= <value>] [PS= <value>] + [NRD=< value>] [NRS=<value>] AD = Drain A [m2] + [NRG=<v alue>] [NRB= <value>] AS = Source A[m2] + [M= <value>] Examples NRD, NRS = D and S diff in squares M1 14 2 13 0 PNOM L=25u W=12u M13 15 3 0 0 PSTRONG M = device multiplier M16 17 3 0 0 PSTRONG M=2 ©rlc L37M28 0 2 100 100 NWEAK L=33u W=12u 04May2011 CARM*, Ch. 4, p. 99 Model Forms .MODEL <model name> NMOS [model parameters] .MODEL <model name> PMOS [model parameters] As shown in Figure 11, the MOSFET is modeled as an intrinsic MOSFET with ohmic resistances in series with the drain, source, gate, and bulk (substrate). There is also a shunt resistance (RDS) in parallel with the drain-source channel. [L=<value>] [W=<value>] cannot be used in conjunction with Monte Carlo analysis . The simulator provides four MOSFET device models, which differ in the formulation of the I-V characteristic. The LEVEL parameter selects between di fferent models : LEVEL=1 LEVEL=2 LEVEL=3 LEVEL=4 LEVEL=5 LEVEL=6 is the Shichman-Hodges model (see reference [1]) is a geometry-based, analytic model (see reference [2]) is a semi-empirical, short-channel model (see reference [2]) is the BSIM model (see reference [3]) is the BSIM3 model (see reference [7] Version 1.0) is the BSIM3 model (see reference [7] Version 2.0) L and W are the channel length and width, and are decreased to get the effective channel length and width. L and W can be specified in the device, model, or .OPTIONS statements. The value in the device statement supersedes the value in the model statement, which supersedes the value in the .OPTIONS statement. ©rlc L3704May2011 SPICE mosfet model levels • Level 1 is the Schichman-Hodges model • Level 2 is a geometry-based, analytical model • Level 3 is a semi-empirical, shortchannel model • Level 4 is the BSIM1 model • Level 5 is the BSIM2 model, etc. ©rlc L3704May2011 SPICE Parameters Level 1 - 3 (Static) Param. Parameter Description Def. Typ. Units 1 1 V VTO Zero-bias Vthresh KP Transconductance GAMMA Body-effect par. 0.0 0.35 V^1/2 PHI Surface inversion pot. 0.6 0.65 V 0.0 0.02 1/V LAMBDA Channel-length mod. 2.E-05 3.E-05 A/V^2 TOX Thin oxide thickness NSUB Substrate doping 0.0 1.E+15 cm^-3 NSS Surface state density 0.0 1.E+10 cm^-2 LD Lateral diffusion 0.0 8.E-05 m ©rlc L3704May2011 1.E-07 1.E-07 m SPICE Parameters Level 1 - 3 (Static) Param. Parameter Description Def. Typ. 1 1 600 700 Units TPG Type of gate material* UO Surface mobility IS Bulk jctn. sat. curr. JS Bulk jctn. sat. curr. dens. PB Bulk junction potential 0.8 0.75 V RD Drain ohmic resistance 0 10 Ohms RS Source ohmic resistance 0 10 Ohms RSH S/D sheet ohmic res. 0 10 Ohms/sq 1.E-14 1.E-15 cm^2/V-s A A/m^2 * 0 = aluminum gate, 1 = silicon gate opposite substrate type, 2 = silicon gate same as substrate. ©rlc L3704May2011 SPICE Parameters Level 1 - 3 (Q & N) Param. Parameter Description Def. Typ. Units 0 1.E-09 Fd/m^2 CJ Zero-bias bulk cap./A MJ Bulk jctn. grading coeff. 0.5 0.5 CJSW Zero-bias perimeter C/l 0 1.E-09 MJSW Per. C grading coeff. 0.5 0.5 FC For.-bias cap. coeff. 0.5 0.5 CGBO Gate-bulk overlap C/L 0 2.E-10 Fd/m CGDO Gate-drain overlap C/L 0 4.E-11 Fd/m CGSO G-S overlap C/L 0 4.E-11 Fd/m AF Flicker-noise exp. 1 1.2 KF Flicker-noise coeff. 0.0 1.E-26 ©rlc L3704May2011 Fd/m Level 1 Static Const. For Device Equations Vfb = -TPG*EG/2 -Vt*ln(NSUB/ni) - q*NSS*TOX/eOx VTO = as given, or = Vfb + PHI + GAMMA*sqrt(PHI) KP = as given, or = UO*eOx/TOX CAPS are spice pars., technological constants are lower case ©rlc L3704May2011 Level 1 Static Const. For Device Equations b = KP*[W/(L-2*LD)] = 2*K, K not spice GAMMA = as given, or = TOX*sqrt(2*eSi*q*NSUB)/eOx 2*phiP = PHI = as given, or = 2*Vt*ln(NSUB/ni) ISD = as given, or = JS*AD ISS = as given, or = JS*AS ©rlc L3704May2011 Level 1 Static Device Equations vgs < VTH, ids = 0 VTH < vds + VTH < vgs, id = KP*[W/(L-2*LD)]*[vgs-VTH-vds/2] *vds*(1 + LAMBDA*vds) VTH < vgs < vds + VTH, id = KP/2*[W/(L-2*LD)]*(vgs - VTH)^2 *(1 + LAMBDA*vds) ©rlc L3704May2011 SPICE Parameters Level 2 Param. Parameter Description Def. Typ. 1 5 NEFF Total channel chg coeff. UCRIT Critical E-field for mob. UEXP Expon. coeff. for mob. 0 0.1 UTRA Transverse field coeff. 0 0.5 ©rlc L3704May2011 1.E+04 1.E+04 Units V/cm SPICE Parameters Level 2 & 3 Param. Parameter Description Def. Typ. Units NFS Surface-fast state dens. 0.0 1.E+10 cm^-2 XJ Metallurgical jctn. depth 0.0 1.E-06 m VMAX Max. drift v of carr. 0.0 5.E+04 m/s XQC Coeff. of ch. Q share 0.0 0.4 DELTA Width eff. on Vthresh 0.0 1.0 ©rlc L3704May2011 Level 2 Static Device Equations Accounts for variation of channel potential for 0 < y < L For vds < vds,sat = vgs - Vfb - PHI + g2*[1-sqrt(1+2(vgs-Vfb-vbs)/g2] id,ohmic = [b/(1-LAMBDA*vds)] *[vgs - Vfb - PHI - vds/2]*vds -2g[vds+PHI-vbs)1.5-(PHI-vbs)1.5]/3 ©rlc L3704May2011 Level 2 Static Device Eqs. (cont.) For vds > vds,sat id = id,sat/(1-LAMBDA*vds) where id,sat = id,ohmic(vds,sat) ©rlc L3704May2011 Level 2 Static Device Eqs. (cont.) Mobility variation KP’ = KP*[(esi/eox)*UCRIT*TOX /(vgs-VTH-UTRA*vds)]UEXP This replaces KP in all other formulae. ©rlc L3704May2011 SPICE Parameters Level 3 Param. Parameter Description Def. Typ. KAPPA Saturation field factor 0.2 1.0 ETA Stat. feedbk on Vthresh 0.0 1.0 THETA Mobility modulation 0.0 0.05 DELTA Width eff. on Vthresh 0.0 1.0 ©rlc L3704May2011 Units 1/V BJT Self-heating • Self heating of the transistor is proportional to the power dissipated. • Temperature Rise = ΔT = Rth ∙Power • The VBIC model was developed to simulate the BJT such that the device temperature tracked power dissipation in real time. • Other circuit simulators which accommodate thermal resistance are – HICUM – MEXTRAM ©rlc L3704May2011 Rth Estimation for a Small Diode-isolated BJT Device VBE=0.87 V and VCE=20 V, RTH = 341 C/W ©rlc L3704May2011 VBIC Model Highlights dt tl ©rlc L3704May2011 Self-heating effects included Improved Early effect modeling Quasi-saturation modeling Parasitic substrate transistor modeling Parasitic fixed (oxide) capacitance modeling An avalanche multiplication model included Base current is decoupled from collector current 2-D Isotherm Plot- Lines Connecting Points of Equal Temperature 2-D Isotherm plots for a structure scaled to be the same as the P10 1X2X1 device. ©rlc L3704May2011 Thermal Model of a SiGe HBT • The structure of a typical SiGe HBT (Heterojunction Bipolar Transistor) [1] Oxide • The Electrical circuit topology (Cauer network) for the thermal analogy model ©rlc L3704May2011 2 ©rlc L3704May2011 SILICON •A silicon structure can be sub-divided into several silicon slabs. •Each section contributes to the total Rth and Cth of the structure. If each section is of equal volume, their individual Rth and Cth should be equal in value. •To correspond to uniform heat flow, each section can be represented by a thermal resistance and half the total capacitance on each node of the resistor. Cth SILICON One Dimensional Heat Flow in Silicon HEAT AMBIENT Rth Cth 2 The Distributed Nature of the Heat Flow •The corresponding CTh /2 capacitors are aggregated at each node. •Note that the “ambient end” CTh /2 is short-circuited. •The distributed equivalent circuit analogy simulation is obtained from the following network. Rth n Cth 2n Rth n Cth n Cth n Rth = Total Thermal resistance for the silicon structure Cth= Total Thermal capacitance of the silicon structure n = number of sections A=area t= thickness cp= thermal capacitance kp= thermal conductance ρ=density ©rlc L3704May2011 Rth n Rth n Cth n t k A p Cth ρ c t A p Rth Comparison of Circuit Analogy to Davinci Simulation of the Heat Flow Considering a silicon structure of size 3.7umx2.5um x10um Rth t 6989 Cth ρ c t A 18.2n Tau Rth Cth 1.26u p k A p Dividing the structure into 10 sections. Rth Cth where i=1,2,3…n, Rth Cth n= number of sections i i n n Dotted line=Davinci simulation measurement Solid line = equivalent circuit simulation ©rlc L3704May2011 Approximating the Distributed Circuit With a Single Pole Model •Converting the 10 element distributed model to a 1 pole model: RTotal=Rth at ‘dc’ ΔQTotal =(cp)(ρ)Tavg For total heat consumption. n Rth 1 pole Rthi Rth i 1 Rth n Cth 2n ©rlc L3704May2011 Cth n Rth n Cth n Heat stored corresponds to charge stored for the equivalent circuit. n V1pole C1pole Vi Ci i1 For n , the limit is C1pole CTh 2 Rth n Cth n Rth n Comparison of Circuit Analogy to Davinci Simulation for Heat Flow RTh(W/K) 1.E+04 1.E+03 30um slab davinci 30um slab circuit simulation 20um slab davinci 20um slab simulation 1.E+02 10um slab davinci 10um slab simulation 1.E+01 1.E-08 ©rlc L3704May2011 1.E-07 1.E-06 1.E-05 Time 1.E-04 1.E-03 (cont’d) Rth(k/W) 1.E+04 1.E+03 1.E+02 1.E-07 1.E-06 1.E-05 1.E-04 1.E-03 Time Results from equivalent circuit simulations Results from Davinci Simulation Results from device measurement Foster network Results from device measurement Cauer network ©rlc L3704May2011 Top of the tub Top of the oxide Top of the wafer Circuit used for simulations ©rlc L3704May2011 dt for VBIC-R1.5 model • Model: VBIC-R1.5. • “selft” flag set to 1. • No optimization done. • No external circuit connected. • Rth=5.8E+0 • Cth=96E-12 ©rlc L3704May2011 VBIC-R1.5 Y11 plot (standard data) ©rlc L3704May2011 VBIC-R1.5 Y11 plot (standard data) ©rlc L3704May2011 VBIC-R1.2 Y11 plot (optimized data) • For optimized data refer slide “Model Parameters”. • Circuit used is shown in “Circuit for Y parameters (optimized data)” slide. fc Τ fc1= 2E3 7.962E-05 fc2= 9.25E4 1.721E-06 fc3= 3.2E6 4.976E-08 Fc4=2E3 7.962E-05 Fc5=1E5 1.592E-06 Fc6=4E6 3.981E-08 fc7= 2E3 7.962E-05 fc8= 1E5 1.592E-06 fc9=4E6 3.981E-08 ©rlc L3704May2011 Spreadsheet for Calculating the Rth and Cth • Calculations mentioned in the previous slides have been implemented in an Excel spreadsheet. • The Cauer to Foster network transformation is done. Fig. 7. Electrical equivalent Cauer network of the HBT Fig. 8. Electrical equivalent Foster network of the HBT • The spreadsheet takes the dimensions of different layers of the devices and gives corresponding Cauer and Foster network values. This enables the calculation of time constants which can be converted into a single pole. The characteristic times for the Foster network appear on a impulse response plot. ©rlc L3704May2011 Effect of Rth on current feedback op-amp settling time 500 500 W W - vOUT + 100 W vIN = 1 V P-P, t = 200 m-sec Offset ©rlc L3704May2011 vOUT ,max vOUT t AvIN,max Current Feedback Op Amp Data (LMH6704) Switching Offset Thermal switching offset as % of Vp 1.00% cfoa model 0.39% e t / 13.4 0.16% e t / 3.3 y = 0.0039e-0.0749x Offset = .39% Tau = 13.4 u-sec 0.10% y = 0.0055e-0.1416x Offset = 0.16% Tau = 7.1 u-sec Tau 0.01% ©rlc L3704May2011 0 5 0.16% 3.3 0.55% / 7.7 0.39% / 13.4 10 15 20 25 Time after switching (u-sec) 30 LMH6550 impulse thermal characteristics • LeCroy sampling oscilloscope (1MW input mode) • Maximum averaging (10000) • Input nominally +/- 1V with 50 micro-sec period and 50% duty cycle. • Fractional Gain Error = FGE vOUT (t) FGE ©rlc L3704May2011 vOUT ,max vIN (t) vIN,max 1 vIN Rising Response 1.2 10.00% vIN 1.0 0.8 FGE vOUT 0.6 0.4 0.2 1.00% y = 0.0362e-111568x R2 = 0.9707, Tau = 9 micro-sec 0.0 0.0E+00 ©rlc L3704May2011 5.0E-06 1.0E-05 1.5E-05 0.10% 2.0E-05 vIN Falling Response 0 10.00% -0.2 vOUT -0.4 y = 0.0373e-148345x R2 = 0.9257 Tau = 6.7 micro-sec -0.6 1.00% -0.8 -1 -1.2 0.0E+00 ©rlc L3704May2011 FGE vIN 5.0E-06 1.0E-05 1.5E-05 0.10% 2.0E-05 Current Feedback Op-Amp (CFOA) with Simple Current Mirror (CM) Bias VCC Q3 Q4(stk2pnp-cm) Q9 Q10 Q17 Q7(stk3-npn-bf) 200 μA +1 V Q6 Q14 VEE VP VCC VEE Z VN Q5 -1 V Q 15 RF Q13 Q8(stk3-pnp-bf) Q1 Q2 Q11 VO VCC Q12 Q 16 Q18 sup VEE ©rlc L3704May2011 STICK1 STICK2 STICK3 STICK4 STICK5 STICK6 Large-signal Output Voltage Transient Analysis for CFOA with Simple CM Biasing Voltage (mV) -968 High-to-Low area x1 High-to-Low area x8 -970 TT=-5311 mV -972 -974 TT=-789 mV -976 -978 0 5 10 15 20 25 30 35 40 45 Time (ms) Voltage (mV) 1028 1026 Low-to-High area x1 Low-to-High area x8 TT=5313 mV 1024 1022 TT=789 mV 1020 0 ©rlc L3704May2011 5 10 15 20 25 Time (ms) 30 35 40 45 Hypothesis: The Thermal Tail is a Linear Superposition of the Contribution from each Individual Circuit Stick • The contribution of individual transistor to the total thermal tail. • Used six stick classifications according to transistor type and functionality. i.e. Q10stk3-pnp-bf and Q11stk4-npn-cm • Enabled the self-heating effect in the stick of interest and disabled the self-heating effect of the remaining transistors. • Simulated the contribution of each individual stick. • The total thermal tail simulated is essentially the sum of the individual thermal tail contributions of each circuit stick. ©rlc L3704May2011 The Hypothesis Supported Area x1 Thermal Tail (uV/V) ©rlc L3704May2011 Area x8 High-to-Low Low-to-High High-to-Low Low-to-High stk2-npn-bf (Q5) -822 842 -124 128 stk2-pnp-bf (Q6) -727 712 -101 98 stk2-npn-cm (Q2) -89 91 -11 12 stk2-pnp-cm (Q4) -91 89 -10 9 stk3-npn-bf (Q7) -877 850 -111 106 stk3-pnp-bf (Q8) -783 808 -111 115 stk4-npn-cm (Q12) -1213 1217 -172 173 stk4-pnp-cm (Q10) -1075 1073 -159 158 stk5-npn-bf(Q13) 13 -13 2 -2 stk5-pnp-bf(Q14) -4 4 -1 1 stk5-npn-cm(Q18) 16 -15 2 -2 stk5-pnp-cm(Q17) -5 2 0 0 stk6-npn-bf(Q15) 0 1 0 0 stk6-pnp-bf(Q16) -1 0 0 0 added total -5658 5661 -796 796 simulated total -5311 5313 -789 789 References • • • • • Fujiang Lin, et al, “Extraction Of VBIC Model for SiGe HBTs Made Easy by Going Through Gummel-Poon Model”, from http://eesof.tm.agilent.com/pdf/VBIC_Model_Extractio n.pdf http://www.fht-esslingen.de/institute/iafgp/neu/VBIC/ Avanti Star-spice User Manual, 04, 2001. Affirma Spectre Circuit Simulator Device Model Equations Zweidinger, D.T.; Fox, R.M., et al, “Equivalent circuit modeling of static substrate thermal coupling using VCVS representation”, Solid-State Circuits, IEEE Journal of , Volume: 2 Issue: 9 , Sept. 2002, Page(s): 1198 -1206 ©rlc L3704May2011 Thermal Analogy References [1] I.Z. Mitrovic , O. Buiu, S. Hall, D.M. Bagnall and P. Ashburn “Review of SiGe HBTs on SOI”, Solid State Electronics, Sept. 2005, Vol. 49, pp. 1556-1567. [2] Masana, F. N., “A New Approach to the Dynamic Thermal Modeling of Semiconductor Packages”, Microelectron. Reliab., 41, 2001, pp. 901–912. [3] Richard C. Joy and E. S. Schlig, “Thermal Properties of Very Fast Transistors”, IEEE Trans. ED, ED-1 7. No. 8, August 1970, pp. 586599. [4] Kevin Bastin, “Analysis and Modeling of self heating in SiGe HBTs” , Aug. 2009, Masters Thesis, UTA. [5] Rinaldi, N., “On the Modeling of the Transient Thermal Behavior of Semiconductor Devices”, IEEE Trans-ED, Volume: 48 , Issue: 12 , Dec. 2001; Pages:2796 – 2802. ©rlc L3704May2011 Simulation … References • • [1] E. Castro, S. Coco, A. Laudani, L. LO Nigro and G. Pollicino, “A New Tool For Bipolar Transistor Characterization Based on HICUM”, Communications to SIMAI Congress, ISSN 1827-9015, Vol. 2, 2007. [2] K. Bastin, “Analysis And Modeling of Self Heating in Silicon Germanium Heterojunction Bipolar Transistors”, Thesis report, The University of Texas at Arlington, August 2009. ©rlc L3704May2011 AICR Team at University of Texas Arlington - Electrical Engineering Earlier Contributors Current • Ronald L. Carter, Professor • W. Alan Davis, Associate Professor • Howard T. Russell, Senior Lecturer • Ardasheir Rahman1 • Xuesong Xie3 • Arun Thomas-Karingada2 • Sharath Patil2 • Valay Shah2 ©rlc L3704May2011 • • • • • • Kevin Bastin, MS Abhijit Chaugule, MS Daewoo Kim, PhD Anurag Lakhlani, MS Zheng Li, PhD Kamal Sinha, PhD 1PhD Student 2MS Student 3Post-doctoral Associate References • CARM = Circuit Analysis Reference Manual, MicroSim Corporation, Irvine, CA, 1995. • M&A = Semiconductor Device Modeling with SPICE, 2nd ed., by Paolo Antognetti and Giuseppe Massobrio, McGraw-Hill, New York, 1993. • **M&K = Device Electronics for Integrated Circuits, 2nd ed., by Richard S. Muller and Theodore I. Kamins, John Wiley and Sons, New York, 1986. • *Semiconductor Physics and Devices, by Donald A. Neamen, Irwin, Chicago, 1997 ©rlc L3704May2011