In-System Programming of the AT17C65(A)/128(A)/256(A)

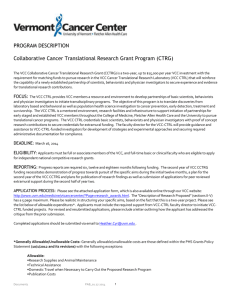

advertisement

AT17 Series EEPROM Configuration Memories Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 Hotline (408) 436-4119 fpga@atmel.com OR configurator@atmel.com Slide 1 AT94 Training 2001 Configurator Download Board Layout Behavioral VHDL/Verilog Synthesis Macro Generators architecture behave of CNT6 is signal SQA, SQB : integer range 0 to 6 := 1; Tpd = 10 ns Fm ax = 100 MHz Size = 12x8 Cells Icc = .2mA/MHz begin Program Configuratio n Memory QA <= To_Vector(3,SQA); Place & Route 10100010 01101001 11101011 Schematic Timing Analysis Design Entry & Simulation ATDH2200 ATDH2225 Third Party Programmer Physical Design (Including synthesis compiler) Libraries & Interface Slide 2 AT94 Training 2001 FPGA/FPSLIC ISP Configuration Memories 65K, 128K, 256K, 512K, 1M, 2M & 4M Serial EEPROMs (Direct Xilinx & Altera OTP Replacement) • 7 Sizes – – – – – – – AT17C65 - 65K Version (8/20 pins) AT17C128 - 128K Version (8/20 pins) AT17C256 - 256K Version (8/20 pins) AT17C512 - 512K Version (8/20 pins) AT17C010 - 1Meg Version (8/20 pins) AT17C020 - 2Meg Version (20 pins) AT17C040 - 4Meg Version (44 pins) Q3/2001 Configurator SRAM-Based FPGA/FPSLIC - Atmel - Altera - Lucent - Xilinx • Interface with any Atmel or other SRAM FPGA & FPSLIC - AT6000/AT40K (Atmel FPGA) - AT94K (Atmel FPSLIC) - XC2000/3000/4000/5200 - Xilinx Vertex XCV - OR2/3/4Cxx (ORCA) - Altera 1K/6K/8K/10K/20K (Flex) - Spartan XCS - Cypress Delta39K • Up to 15 MHz configuration rate • Fast, ISP via 2-wire interface • 3V (17LV) & 5V (17C) options Slide 3 AT94 Training 2001 Key Features and Benefits • ISP 5V or 3.3V • Fast programming up to 15MHz • Cascade – Multiple devices can be cascaded. • Reconfigurable FPGA Memory – EEPROM is priced competitively with OTP products • Two Parts in One – AT17Cxxx can also emulate 24Cxxx parts • In System (Re)Programmable Easy system hook-up for ISP operation – Can be soldered to PCB - no socket required Slide 4 AT94 Training 2001 Two Parts in One • Use ‘spare’ memory like a 24Cxxx device. 0000 – Save on cost/Board space/Power consumption. – Use ISP interface mux to enable 2-wire SEEPROM capability. 17CXXX 1AD7 1B00 24CXXX 1FFF AT17 Device Address space. Slide 5 FPGA Configuration memory requirements are stored from zero page to 1AD7 Hex. This memory space is accessed in AT17Cxxx mode by the FPGA (SerEn =1) ‘Unused’ memory at the end of the AT17Cxxx can be accessed in 24Cxxx mode (SerEn=0). Information such as last number redial/PCI I.D. Plug and Play/IP address etc. can easily be stored or retrieved using a micro-controller. AT94 Training 2001 New Parts / Old Parts Design Differences Configurators ISP OSC WP Ready Cascade Package Low Density(Old) Mux N RESET/OE N Low Density(New) Simple N RESET/OE N High Density(Old 512/010) Simple Y WP1/WP2 Y High Density(Old 020) High Density(New 002) 4M 8M/16M(AT17C/F)) 2M/4M/8M(AT18F) Simple Simple Simple Simple JTAG ISP Y Y Y Y Y N WP1/WP2 Y Y Y Y Y Y Y Y OSC : Internal Oscillator function available WP : Write Protect, this feature allows portions of the memory to be blocked during Write instructions. Slide 6 Y(Except 65) 8 DIP, 8/20 SOIC, 20 PLCC Y, using A2 8 DIP, 8/20 SOIC, 20 PLCC Y, using A2 20 PLCC, 8 DIP N 20 PLCC Y, using A2 20 PLCC Y 44 TQFP/PLCC Y 44 TQFP/PLCC Y 44 TQFP/PLCC AT94 Training 2001 Configurator Availability Atmel & Xilinx Versions Slide 7 Device 8-DIP 8-SOIC 20-PLCC 20-SOIC 44 TQFP JTAG 17C65 17C128 17C256 Now Now Now Now Now Now Now Now Now Now Now Now ---- ---- 17C512 17C010 17C020 Q3/01 Q3/01 -- ---- Now Now Now ---- ---- ---- 17C002 17C040 17F080 17F016 ----- ----- Q2/01 ---- ----- -Q3/01 H2/01 H2/01 ----- 18F020 18F040 18F080 ---- ---- H2/01 H2/01 H2/01 ---- -H2/01 H2/01 Yes Yes Yes • AT17C/F series = 2-wire serial ISP • AT18F series = JTAG ISP AT94 Training 2001 Configurator Availability Altera Versions Slide 8 Device 8-DIP 8-SOIC 20-PLCC 20-SOIC 32 TQFP JTAG 17C65A 17C128A 17C256A ---- ---- Now Now Now ---- ---- ---- 17C512A 17C010A 17C020A Q2/01 Q2/01 -- ---- Now Now Now ---- ---- ---- 17C002A 17C040A 17F080A 17F016A ----- ----- Q2/01 ---- ----- Q3/01 Q4/01 H2/01 H2/01 ----- 18F020A 18F040A 18F080A ---- ---- ---- ---- H2/01 H2/01 H2/01 Yes Yes Yes • AT17C/F series = 2-wire serial ISP • AT18F series = JTAG ISP AT94 Training 2001 ISP Programming Use Mux for ISP circuit Simple ISP circuit AT17C65/128/256 AT17LV65/128/256 CLK DATA RESET/OE CE 4 7 9 VCC VCC DATA SCLK CEO (A2) 12 SER_EN 1Y 2Y 3Y 4Y 74HC(T)157 E 15 1 2 3 5 6 11 10 14 VCC RESET DATA SCLK AT40K M2 M1 M0 D<0> CCLK CON INIT GND Figure 1: In-System Programming of AT17C/LV65/128/256 (old) EEPROM in AT40K FPGA Application Slide 9 8 10 VCC VCC 13 GND RESET 6 7 9 SER_EN VCC GND AT17C65/128/256 AT17LV65/128/256 AT40K RESET 2 4 5 GND S 1A 1B 2A 2B 3A 3B 4A 4B 1 3 1 3 5 7 9 2 4 6 8 10 RESET M2 M1 M0 D<0> CCLK CON INIT DATA CLK CE RESET/OE SER_EN GND GND SER_EN RESET/OE CE Figure 2: In-System Programming of AT17C/LV65/128/256 (new) EEPROM in AT40K FPGA Application AT94 Training 2001 ‘A’ Vs ‘Non A’ EEPROM High Density EEPROM AT17(A) Internal oscillator is enabled by default • 'A' part is recommended for Altera users • Pin out is different • Oscillator must be enabled for Altera’s Flex 1K,10K & 6K family, disabled for Altera’s Flex 8K family Slide 10 AT17(Non A) Internal oscillator is disabled by default • Non-A part is recommended for Atmel, Xilinx, and Lucent users AT94 Training 2001 Programming Options • ATDH2200 board for ISP and stand-alone device programming • ATDH2225 for ISP - Recommended for Atmel custom board layout - Allows cascading controlled by software • Broad third party programmer support – Faster to program than OTP parts • Source Code is available - For development of Microcontrolled programming Slide 11 AT94 Training 2001 ATDH2200E • PC Programmer kit for ALL AT17 Series EEPROMs – Standalone programming of Configuration EEPROM, OR – Interface to target board for In-System Programming – Supports .pof, .rbf, .hex, .mcs and .bst file formats • Takes files straight from Atmel/Xilinx/Altera/Lucent software – 5V and 3.3V operation (from supply or target board) – Choice of 20pin PLCC or SOIC socket adapter • ATDH2221 for all 20 pin SOIC • ATDH2222 for all 20 pin PLCC (incl. Altera, 2M) • ATDH2223 for all 8 pin SOIC • ATDH2224 for 44 pin TQFP • ATDH2226 for 32 pin TQFP • ATDH2227 for 44 pin PLCC – Directly supported by Atmel’s IDS FPGA software CPS (Configurator Programming System) software – Quick start user’s guide Slide 12 AT94 Training 2001 ATDH2200 Stand-alone Device Programming Parallel Cable DB-25M ATDH2200 Parallel Port DB-25F PC AT17CXXX Configurator Socket Slide 13 AT94 Training 2001 ATDH2200 In-System Programming Parallel Cable DB-25M 10-pin Ribbon Cable Target System ATDH2200 Parallel Port FPGA FPGA DB-25F PC In-System Programming Connector Header Slide 14 In-System Programming AT17CXXX Configurator Connector Header AT94 Training 2001 ATDH2225 In-System Programming Cable Target System DB-25M ATDH2225 Parallel Port FPGA FPGA PC Programming Dongel Slide 15 In-System Programming AT17CXXX Configurator Connector Header AT94 Training 2001 CPS Configurator Programming Software • • • • • • • • • • Slide 16 AT17 Configurator Programming System s/w Clear and compact GUI Windows 95/98/NT/2000 support 2Meg device support Partitions Altera bitstream files for use in third party programmers Reset polarity verification (on ATDH2200E only) Download data rate calibrated to PC processor Save and restore settings between sessions Enable/Disable internal clock for Altera ‘A’ parts Online help and link to WWW-based FAQ AT94 Training 2001 CF.EXE (Windows 3.1/95/98 DOS software) • Program from Atmel .bst file format [AT40K] CF /P /I input_file.bst /S code /Z LPT1] • Program from Altera .pof or .hex file formats CF /A /I input_file.pof /S code /Z CF /A /I input_file.hex /S code /Z • Program from Xilinx .mcs file format CF /E /I input_file.mcs /S code /Z • Density ‘codes’ are 65, 128, 256, 512, 010 level [/G] [/D level [/D LPT1] level [/D LPT1] level [/D LPT1] – 2Meg part supported in CPS (GUI version of CF) only • Reset ‘levels’ are L (active low) or H (active high) • Altera file conversion for 3rd party programmers CF /B /I input_file.pof /O output_file.bst /F HEX CF /B /I input_file.hex /O output_file.bst /F HEX • Source code for CF available on request (cf.c) Slide 17 AT94 Training 2001 AT40K Configuration Statistics Device AT40K05 AT40K10 AT40K20 AT40K40 AT40K80 AT40K125 Configuration Bits* Configurator 63K 135K 236K 521K 916K 1419K AT17C/LV65 AT17C/LV256 AT17C/LV256 AT17C/LV512 AT17C/LV010 AT17C/LV020 Configurator AT40K Slide 18 * = Can be reduced by using bit-stream compression option AT94 Training 2001 FPSLIC Configuration Statistics Device Configuration Bits* Configurator* AT94K10 AT94K20 AT94K40 423K 524K 809K AT17LV512 AT17LV010 AT17LV010 Configurator AT94K * = Can be reduced by using bit-stream compression option Slide 19 AT94 Training 2001 Drop-In of AT17C65/128/256 AT40K FPGA Application VCC AT17C65/128/256 AT17LV65/128/256 AT40K RESET RESET M2 M1 M0 D<0> CCLK CON INIT DATA CLK CE RESET/OE VCC SER_EN GND Note: Slide 20 1. 4.7k ohm resistors used unless otherwise specified. 2. Reset polarity must be set to active low. AT94 Training 2001 ISP of AT17C/LV65/128/256(Old Vs New) EEPROM Old (using Multiplexor) New (No Multiplexor) VCC AT17C65/128/256 AT17LV65/128/256 CLK DATA RESET/OE CE 4 7 9 CEO (A2) VCC DATA SCLK 12 SER_EN 1Y 2Y 3Y 4Y 74HC(T)157 E 15 5 6 11 10 14 VCC GND VCC M2 M1 M0 GND Slide 21 RESET DATA SCLK AT40K VCC SER_EN VCC AT17C65/128/256 AT17LV65/128/256 AT40K RESET 8 10 13 GND RESET 6 7 9 GND 1 3 2 4 5 S 1A 1B 2A 2B 3A 3B 4A 4B 2 1 3 D<0> CCLK CON INIT 1 3 5 7 9 2 4 6 8 10 RESET M2 M1 M0 D<0> CCLK CON INIT DATA CLK CE RESET/OE SER_EN GND GND SER_EN RESET/OE CE AT94 Training 2001 Drop-In of AT17C512/010/002 AT40K FPGA Application AT17C512/010/020 AT17LV512/010/020 AT40K RESET RESET M2 M1 M0 D<0> CCLK CON INIT DATA CLK CE RESET/OE VCC SER_EN READY GND Note: Slide 22 1. 4.7k ohm resistors used unless otherwise specified. 2. Use of the READY pin is optional. 3. Reset polarity must be set to active low. AT94 Training 2001 In-System Programming of the AT17C/LV512/010/002 AT40K FPGA Application VCC VCC DATA SCLK 1 2 3 4 5 6 7 8 9 10 VCC GND SER_EN AT17C512/010/002 AT17LV512/010/002 AT40K RESET RESET M2 M1 M0 D<0> CCLK CON INIT DATA CLK CE RESET/OE SER_EN READY GND Notes: 1. 4.7k ohm resistors used unless otherwise specified. 2. Use of the READY pin function is optional. 3. Reset polarity must to be set active low. Slide 23 AT94 Training 2001 ISP of New Low Density(AT17C/LV65/128/256) VS High Density(AT17C/LV512/010/002) VCC VCC VCC VCC DATA SCLK 1 3 2 4 5 6 7 8 9 10 DATA SCLK VCC 1 2 3 5 4 6 7 8 9 10 VCC GND GND SER_EN SER_EN AT17C65/128/256 AT17LV65/128/256 AT40K RESET RESET RESET M2 M1 M0 GND Slide 24 D<0> CCLK CON INIT AT17C512/010/002 AT17LV512/010/002 AT40K RESET DATA CLK CE RESET/OE SER_EN M2 M1 M0 D<0> CCLK CON INIT DATA CLK CE RESET/OE SER_EN Ready GND AT94 Training 2001 Drop-In of AT17C65/128/256 AT60xx FPGA Application VCC AT17C65/128/256 AT17LV65/128/256 AT60xx REBOOT M2 M1 M0 D0 CCLK CON DA TA CLK RESET/OE CE VCC SER_EN CS GND Notes: 1. 4.7k ohm resistors used unless otherwise specified. 2. Reset polarity must be set active high. Slide 25 AT94 Training 2001 In-System Programming of the AT17C65/128/256 (Old) RESET/OE Programming Arrangement AT60xx FPGA Application AT17C65/128/256 AT17LV65/128/256 CLK DATA RESET/OE CE Old Version 4 7 9 1Y 2Y 3Y CEO (A2) 12 SER_EN 74HC(T)157 E 15 VCC 4Y S 1 1A 1B 2A 2B 2 3 5 6 3A 11 3B 10 4A 14 4B VCC GND VCC VCC 13 GND DATA SCLK AT60xx REBOOT M2 M1 M0 D0 CCLK CON CS GND 1 3 5 7 9 2 4 6 8 10 GND SER_EN RESET/OE CE Notes: 1. 4.7k ohm resistors used unless otherwise specified. 2. Reset polarity must be set active high. Slide 26 AT94 Training 2001 In-System Programming of the AT17C65/128/256 (New) RESET/OE Programming Arrangement AT60xx FPGA Application VCC VCC New Version DATA SCLK 1 3 5 7 9 2 4 6 8 10 VCC GND SER_EN AT17C65/128/256 AT17LV65/128/256 AT60xx REBOOT M2 M1 M0 CS D0 CCLK CON DATA CLK CE RESET/OE SER_EN GND Note : Reset Polarity of the EEPROM is programmed HIGH for AT6K devices Slide 27 AT94 Training 2001 Drop-In Replacement of XC17/AT17 PROMs Xilinx/Lucent FPGA Application VCC VCC XC4000/OR3 PROGRAM PROGRAM CCLK DIN DONE INIT AT17Cxxx AT17LVxxx CLK DATA CE RESET/OE SER_EN READY M2 M1 M0 GND Notes: 1. 2. 3. 4. Slide 28 4.7k ohm resistors used unless otherwise specified. An optional internal pullup resistor is enabled here for DONE. Reset polarity must be set active low. Use of the READY pin is optional (available on AT17C512/010/020 only). AT94 Training 2001 In-System Programming of the AT17C65/128/256 RESET/OE Programming Arrangement Xilinx/Lucent FPGA Application AT17C65/128/256 AT17LV65/128/256 CLK DATA RESET/OE CE 4 7 9 CEO (A2) 12 SER_EN 1Y 2Y 3Y 4Y 74HC(T)157 E 15 S 1 1A 1B 2A 2B 3A 3B 4A 4B 2 3 5 6 11 10 14 VCC GND VCC VCC 13 VCC GND XC4000/OR3 PROGRAM PROGRAM DATA DCLK CCLK DIN DONE INIT 1 3 5 7 9 2 4 6 8 10 GND M2 M1 M0 SER_EN RESET/OE CE GND Notes: 1. 4.7k ohm resistors used unless otherwise specified. 2. An optional internal pullup resistor is enabled here for DONE. 3. Reset polarity must be set active low. Slide 29 AT94 Training 2001 In-System Programming of the AT17C512/010/002 Xilinx/Lucent FPGA Application VCC VCC DATA SCLK 1 3 2 4 5 6 7 9 8 10 VCC GND VCC SER_EN XC4000/OR3 PROGRAM PROGRAM CCLK DIN DONE INIT AT17C512/010/002 AT17LV512/010/002 CLK DATA CE RESET/OE SER_EN READY M2 M1 M0 GND Notes: 1. 2. 3. 4. 5. Slide 30 4.7k ohm resistors used unless otherwise specified. An optional internal pullup resistor is enabled here for DONE. Use of the READY pin function is optional. Reset polarity must be set active low. This schematic cannot be used with the AT17C020 device. AT94 Training 2001 In-System Programming of the AT17C512/010/002 Cascaded Arrangement Xilinx/Lucent FPGA Application VCC VCC DATA SCLK 1 3 2 4 5 7 6 8 9 10 VCC GND VCC SER_EN XC4000/OR3 PROGRAM PROGRAM CCLK DIN DONE INIT AT17C512/010/002 AT17LV512/010/002 Device 1 CLK DATA CE RESET/OE SER_EN CEO (A2) READY M2 M1 M0 GND AT17C512/010/002 AT17LV512/010/002 Device 2 CLK DATA CE RESET/OE SER_EN Notes: 1. 2. 3. 4. 5. Slide 31 VCC CEO (A2) READY 4.7k ohm resistors used unless otherwise specified. An optional internal pullup resistor is enabled here for DONE. Use of the READY pin function is optional. Reset polarity must be set active low. This schematic cannot be used with the AT17C020 device. AT94 Training 2001 In-System Programming of the AT17C/LV020 Xilinx/Lucent FPGA Application VCC VCC DATA SCLK 1 3 5 7 2 4 6 8 9 10 VCC GND VCC SER_EN VCC XC4000/OR3 PROGRAM PROGRAM CCLK DIN DONE INIT AT17C020 AT17LV020 CLK DATA CE RESET/OE SER_EN /CEO (A2) READY M2 M1 M0 GND Notes: 1. 2. 3. 4. 5. 6. Slide 32 4.7k ohm resistors used unless otherwise specified. An optional internal pullup resistor is enabled here for DONE. Use of the READY pin function is optional. Reset polarity must be set active low. This schematic can be used for AT17C512 and AT17C010 devices. A2 bit (device address bit) must be specified high in the software. AT94 Training 2001 Drop-In Replacement of the EPC1064/EPC1213 External Oscillator Arrangement Altera FPGA Application VCC VCC EXT_CLK VCC VCC EPF6K nCONFIG GND DCLK DATA0 CONF_DONE nSTATUS AT17C65(A)/128(A)/256(A) AT17LV65(A)/128(A)/256(A) DCLK DATA nCS OE SER_EN nCE MSEL GND Note: Slide 33 1. 1.0k ohm resistors and 0.1uF capacitor are used unless otherwise specified. 2. Reset polarity must be set active low. 3. RC filter recommended for input to nCONFIG to delay configuration until Vcc is stable. (nCONFIG can instead be connected to an active low system reset signal.) AT94 Training 2001 In-System Programming of Old Low Density(AT17C/LV65A/128A/256A) VS New Low Density(AT17C/LV65A/128A/256A) using Altera FPGA Old (using Multiplexor) New (No Multiplexor) VCC VCC EXT_CLK AT17C65(A)/128(A)/256(A) AT17LV65(A)/128(A)/256(A) DCLK DATA OE nCS 4 7 9 DATA DCLK nCASC (A2) 12 SER_EN 1 3 2 4 5 7 6 8 9 10 VCC 1Y 2Y 3Y 4Y 74HC(T)157 E 15 S SER_EN 2 3 5 6 11 10 14 VCC GND VCC VCC 13 VCC EPF6K VCC nCONFIG GND DATA DCLK EPF6K nCONFIG GND DCLK DATA0 CONF_DONE nSTATUS 1 3 5 7 9 GND nCE MSEL GND VCC 1 1A 1B 2A 2B 3A 3B 4A 4B VCC VCC EXT_CLK 2 4 6 8 10 GND nCE MSEL DCLK DATA0 CONF_DONE nSTATUS AT17C65/128/256A AT17LV65/128/256A Device 1 DCLK DATA nCS OE SER_EN GND SER_EN OE nCS GND Slide 34 AT94 Training 2001 Drop-In Replacement of the EPC1064/EPC1213 Altera FPGA Application VCC VCC VCC VCC VCC EPF8K nCONFIG DCLK DATA0 CONF_DONE nSTATUS AT17C65(A)/128(A)/256(A) AT17LV65(A)/128(A)/256(A) DCLK DATA nCS OE SER_EN nS/P MSEL0 MSEL1 GND Note: Slide 35 1. 1.0k ohm resistors used unless otherwise specified. 2. Reset polarity must be set active low. AT94 Training 2001 Drop-In Replacement of the EPC1441/EPC1/EPC2 Internal Oscillator Arrangement Altera FPGA Application VCC VCC VCC VCC EPF10K nCONFIG GND nCE MSEL0 MSEL1 DCLK DATA0 CONF_DONE nSTATUS AT17C512A/010A/020A AT17LV512A/010A/020A DCLK DATA nCS OE SER_EN READY GND Note: Slide 36 1. 2. 3. 4. 1.0k ohm resistors and 0.1uF capacitor are used unless otherwise specified. Applicable to EPF6K. Reset polarity must be set active low. RC filter recommended for input to nCONFIG to delay configuration until Vcc is stable. (nCONFIG can instead be connected to an active low system reset signal.) 5. Use of the READY pin is optional. AT94 Training 2001 Drop-In Replacement of the EPC1441/EPC1/EPC2 Internal Oscillator and Cascaded Arrangemen Altera FPGA Application VCC VCC VCC VCC VCC EPF10K nCONFIG GND nCE MSEL0 MSEL1 DCLK DATA0 CONF_DONE nSTATUS AT17C512A/010A/020A AT17LV512A/010A/020A Device 1 DCLK DATA nCS OE SER_EN nCASC AT17C512A/010A/020A AT17LV512A/010A/020A Device 2 DCLK DATA nCS OE SER_EN READY GND Notes: 1. 1.0k ohm resistors and 0.1uF capacitor are used unless otherwise specified. 2. Reset polarity must be set active low. 3. RC filter recommended for input to nCONFIG to delay configuration until Vcc is stable. (nCONFIG can instead be connected to an active low system reset signal.) 4. An additional pullup resistor on the nCS of Device 2 is only required if this device exhibits a sensitivity to the power-up ramp of VCC (i.e. it incorrectly powers up as a bus master thereby driving DCLK as well). 5. Use of the READY pin is optional. Slide 37 AT94 Training 2001 In-System Programming of the AT17C65(A)/128(A)/256(A) RESET/OE Programming Arrangement Altera FPGA Application AT17C65(A)/128(A)/256(A) AT17LV65(A)/128(A)/256(A) DCLK DATA OE nCS 4 7 9 nCASC (A2) 12 SER_EN 1Y 2Y 3Y 4Y 74HC(T)157 E 15 S 1 1A 1B 2A 2B 3A 3B 4A 4B 2 VCC VCC 3 5 6 11 10 14 VCC GND VCC 13 GND DATA DCLK VCC EPF8K nCONFIG VCC DCLK DATA0 CONF_DONE nSTATUS nS/P MSEL0 MSEL1 1 3 5 7 9 2 4 6 8 10 GND SER_EN OE nCS GND Notes: 1. 1.0k ohm resistors used unless otherwise specified. 2. Reset polarity must be set active low. Slide 38 AT94 Training 2001 In-System Programming of the AT17C65A/128A/256A(older version) RESET/OE Programming with External Oscillator Arrangement Altera FPGA Application AT17C65(A)/128(A)/256(A) AT17LV65(A)/128(A)/256(A) DCLK DATA OE nCS 4 7 9 1Y 2Y 3Y nCASC (A2) 12 SER_EN 74HC(T)157 E 15 VCC 4Y S 1 1A 1B 2A 2B 2 3 5 6 3A 11 3B 10 4A 14 4B VCC GND VCC VCC 13 VCC VCC GND DATA DCLK EPF6K nCONFIG GND DCLK DATA0 CONF_DONE nSTATUS 1 3 2 4 5 7 6 8 9 10 GND nCE MSEL EXT_CLK SER_EN OE nCS GND Notes: 1. 2. 3. 4. Slide 39 1.0k ohm resistors used unless otherwise specified. Applicable to EPF10K. Reset polarity must be set active low. RC filter recommended for input to nCONFIG to delay configuration until Vcc is stable. (nCONFIG can instead be connected to an active low system reset signal.) AT94 Training 2001 In-System Programming of the AT17C512A/010A/002A Altera FPGA Application VCC VCC DATA DCLK VCC VCC 1 3 2 4 5 7 9 6 8 10 VCC GND VCC SER_EN VCC EPF8K nCONFIG nS/P MSEL0 MSEL1 DCLK DATA0 CONF_DONE nSTATUS AT17C512A/010/002A AT17LV512A/010/002A Device 1 DCLK DATA nCS OE SER_EN READY GND Notes: 1. 2. 3. 4. 5. Slide 40 1.0k ohm resistors used unless otherwise specified. The internal oscillator of the AT17A Configurator is disabled. Reset polarity must be set active low. Use of the READY pin is optional. This schematic cannot be used with the AT17C020A device. AT94 Training 2001 In-System Programming of the AT17C512A/010/002A Internal Oscillator Arrangement Altera FPGA Application VCC VCC DATA DCLK VCC 1 2 3 5 4 6 7 9 8 10 VCC GND VCC SER_EN VCC EPF10K nCONFIG GND nCE MSEL0 MSEL1 DCLK DATA0 CONF_DONE nSTATUS AT17C512A/010A/002A AT17LV512A/010A/002A Device 1 DCLK DATA nCS OE SER_EN READY GND Note: Slide 41 1. 2. 3. 4. 5. 1.0k ohm resistors and 0.1uF capacitor are used unless otherwise specified. Applicable to EPF6K. Reset polarity must be set active low. Use of the READY pin is optional. RC filter recommended for input to nCONFIG to delay configuration until Vcc is stable. (nCONFIG can instead be connected to an active low system reset signal.) 6. This schematic cannot be used with the AT17C020A device. AT94 Training 2001 In-System Programming of the AT17C512A/010A/002A Internal Oscillator and Cascaded Arrangement VCC VCC Altera FPGA Application DATA DCLK VCC 1 2 3 4 5 7 6 8 9 10 VCC GND VCC SER_EN VCC EPF10K nCONFIG GND nCE MSEL0 MSEL1 DCLK DATA0 CONF_DONE nSTATUS AT17C512A/010A/002AVCC AT17LV512A/010A/002A Device 1 DCLK DATA nCS OE SER_EN nCASC (A2) READY GND AT17C512A/010A/002A AT17LV512A/010A/002A Device 2 DCLK DATA nCS OE SER_EN Notes: 1. 2. 3. 4. 1.0k ohm resistors and 0.1 uF capacitor are used unless otherwise specified. Use of the READY pin is optional. Reset polarity must be set active low. RC filter recommended for input to nCONFIG to delay configuration until Vcc is stable. (nCONFIG can instead be connected to an active low system reset signal.) 5. This schematic cannot be used with the AT17C020A device. Slide 42 AT94 Training 2001 In-System Programming of the AT17C512A/010A/002A External Oscillator Arrangement Altera FPGA Application VCC VCC EXT_CLK DATA DCLK VCC 1 3 5 7 9 2 4 6 8 10 VCC GND VCC SER_EN VCC EPF10K nCONFIG GND nCE MSEL0 MSEL1 DCLK DATA0 CONF_DONE nSTATUS AT17C512A/010A/002A AT17LV512A/010A/002A Device 1 DCLK DATA nCS OE SER_EN READY GND Note: Slide 43 1. 2. 3. 4. 5. 6. 1.0k ohm resistors and 0.1uF are used unless otherwise specified. Applicable to EPF6K. The internal oscillator of the AT17A Configurator is disabled. Reset polarity must be set active low. Use of the READY pin is optional. RC filter recommended for input to nCONFIG to delay configuration until Vcc is stable. (nCONFIG can instead be connected to an active low system reset signal.) 7. This schematic cannot be used with the AT17C020A device. AT94 Training 2001 In-System Programming of the AT17C/LV020A Internal Oscillator Arrangement Altera FPGA Application VCC VCC DATA DCLK VCC 1 2 3 4 5 7 9 6 8 10 VCC GND VCC SER_EN VCC EPF10K nCONFIG GND nCE MSEL0 MSEL1 DCLK DATA0 CONF_DONE nSTATUS AT17C020A AT17LV020A Device 1 VCC DCLK DATA nCS OE SER_EN /CEO (A2) READY GND Note: Slide 44 1. 2. 3. 4. 5. 1.0k ohm resistors and 0.1uF capacitor are used unless otherwise specified. Applicable to EPF6K. Reset polarity must be set active low. Use of the READY pin is optional. RC filter recommended for input to nCONFIG to delay configuration until Vcc is stable. (nCONFIG can instead be connected to an active low system reset signal.) 6. This schematic can be used with AT17C512A and AT17C010A devices. AT94 Training 2001