EECS 242 Lecture 26! Prof. Ali M. Niknejad

advertisement

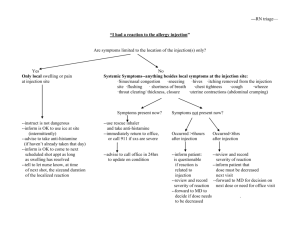

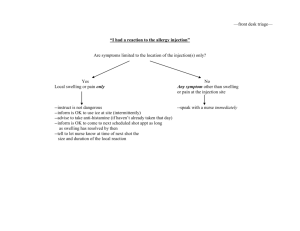

Injection Locking EECS 242 Lecture 26! Prof. Ali M. Niknejad Outline • Injection Locking! - Adler’s Equation (locking range) ! - Extension to large signals ! • Examples:! - GSM CMOS PA ! - Low Power Transmitter! - Dual Mode Oscillators ! - Clock distribution ! • Quadrature Locked Oscillators ! • Injection locked dividers Ali M. Niknejad University of California, Berkeley Slide: 2 Injection Locking http://www.youtube.com/watch?v=IBgq-_NJCl0 locking is also known as frequency entrainment or • Injection synchronization! • Many natural examples including! clocks on the same wall observed to synchronize - pendulum over time! - fireflies put on a good light show! • Injection locking can be deliberate or unwanted Ali M. Niknejad University of California, Berkeley Slide: 3 Injection Locking Video Demonstration http://www.youtube.com/watch?v=W1TMZASCR-I metronomes (similar to pendulums) are initially excited • Several in random phases. The oscillation frequencies are presumably • • Ali M. Niknejad very close but vary slightly due to manufacturing imperfections! When placed on a rigid surface, the metronomes oscillate independently. ! When placed on flexible table with “springs” (coke cans), they couple to one another and injection lock. University of California, Berkeley Slide: 4 A Study of Injection Locking and Pulling Unwanted Injection Pulling/Locking in Oscillators Behzad Razavi, Fellow, IEEE of the difficulties in designing a • One fully integrated transceiver is • • • Abstract—Injection locking characteristics of oscillators are derived and a graphical analysis is presented that describes injection pulling in time and frequency domains. An identity obtained from phase and envelope equations is used to express the requisite oscillator nonlinearity and interpret phase noise reduction. The behavior of phase-locked oscillators under injection pulling is also formulated. exactly due to pulling / pushing! If the injection signal is strong Index Terms—Adler’s equation, injection locking, injection enough, it will lock the source. pulling, oscillator nonlinearity, oscillator pulling, quadrature oscillators.it will “pull” the source Otherwise and produce unwanted modulation! NJECTION of a periodic signal into an oscillator leads to interesting locking orthe pullingtransmitter phenomena. Studied by In the I first example, Adler [1], Kurokawa [2], and others [3]–[5], these effects have is locked a XTAL whereas found to increasingly greater importance for theythe manifest themselvesis in many of today’s transceivers and frequency synthesis receiver locked to the data clock. techniques. Unwanted coupling This paper describes new(package, insights into injection locking and pulling Vdd/Gnd) and formulates the behavior of phase-locked oscillators substrate, can cause under injection. A graphical interpretation of Adler’s equation pulling.! illustrates pulling in both time and frequency domains while derived from the phase and envelope equations A PA isanexpresses aidentity classic source of trouble the required oscillator nonlinearity across the lock range. in a direct-conversion transmitter Section II of the paper places this work in context and Section III deals with injection locking. Sections IV and V respectively consider injection pulling and the required oscillator nonlinearity. Section VI quantifies the effect of pulling on phase-locked loops (PLLs) and Section VII summarizes the experimental results. Ali M. Niknejad Fig. 1. Source: [Razavi] Oscillator pulling in (a) broadband transceiver and (b) RF transceiver. Injection locking becomes useful in a number of applications, including frequency division [8], [9], quadrature generation [10], [11], and oscillators with finer phase separations [12]. Injection pulling, on the other hand, typically proves undesirable. For example, in the broadband transceiver of Fig. 1(a), , is lockedSlide: to University of California, Berkeley the transmit voltage-controlled oscillator, 5 I. GENERAL CONSIDERATIONS Injection Locking is Non-Linear Injection Locking VCO Vnoise Vin |Vout(w)| |Vnoise(w)| Vout W wo ! wo -Δw Δw Δw Noise close in frequency to VCO resonant frequency can cause VCO frequency to shift when its amplitude becomes high enough |Vout(w)| |Vnoise(w)| W wo wo Ali M. Niknejad W -Δw Δw Δw |Vout(w)| |Vnoise(w)| W wo wo W -Δw Δw Δw |Vout(w)| |Vnoise(w)| W wo Δw .H. Perrott W wo -Δw Δw W Source: M. Perrott! MIT OCW 6.976 MIT OCW • For weak injection, you get a response at both side-bands! • As the injection is increased, it begins to “pull” the oscillator! for large enough injection, the oscillation locks to the • Eventually, injection signal University of California, Berkeley Slide: 6 Injection Locking in LC Tanks 1416 IE (a) a free-running • Consider oscillator consisting of an ideal • positive feedback amplifier and an LC tank.! Now suppose (b) we insert a phase shift in the loop. We know this will cause the oscillation frequency to (c) shift since the loop gain has to have exactly 2π phase shift (or multiples) Gm ZT ( 0) = gm R = 1 Gm ej 0 ZT ( Gm ej 0 |ZT ( 1) 1 )|e ZT (⇥1 ) = Ali M. Niknejad =1 j 0 =1 Fig Source: Fig. 2. (a) Conceptual oscillator. (b) Frequency[Razavi] shift due to additional phase shift. (c) Open-loop characteristics. (d) Frequency shift by injection. wh 0 shift), and the ideal inverting buffer follows the tank to create a total phase shift of 360 around the feedback loop. What hap- if University of California, pens if Berkeley an additional phase shift is inserted in the loop, e.g.,Slide: as 7 Injection Locking in LC Tanks [cont] phase shift in the tank will cause the oscillation frequency to • Achange in order to compensate for the phase shift through the • • • tank impedance.! The oscillation frequency is no longer at the resonant frequency of the tank. Note that the oscillation amplitude must also change since the loop gain is now different (tank impedance is lower)! Maximum phase shift that the tank can provide is ± 90°! In a high Q tank, the frequency shift is relatively small since 1.5 1 ⇥0 d Q= 2 d⇥ 0.5 0 ⇥ ⇥0 2 Q -0.5 -1 -1.5 8 9.25 · 10 Ali M. Niknejad 8 9.5 · 10 University of California, Berkeley 8 9.75 · 10 1 · 10 9 9 1.025 · 10 1.05 · 10 9 9 1.075 · 10 1.1 · 10 9 Slide: 8 Phase Shift for Injected Signal interesting to observe that if a signal is • It’s injected into the circuit, then the tank current is • • • • Ali M. Niknejad a sum of the injected and transistor current.! Assume the oscillator “locks” onto the injected current and oscillates at the same frequency.! Since the locking signal is not in general at the Source: [Razavi] resonant center frequency, Fig. the2. tank introduces (a) Conceptual oscillator. (b) Frequency shift due to additional phase a phase shift! shift. (c) Open-loop characteristics. (d) Frequency shift by injection. In order for the oscillator loop gain to be equal shift),the and the idealofinverting to unity with zero phase shift, sum the buffer follows the tank to create a totalthe phase shift of 360 around the feedback loop. What hapcurrent of the transistor and injected pens if an additional phase shift is inserted in the loop, e.g., as currents must have the proper phase shift to depicted in Fig. 2(b)? The circuit can no longer oscillate at compensate for the tank phase becauseshift.! the total phase shift at this frequency deviates from 360 by . Thus,tank as illustrated in Fig. 2(c), the oscillation frequency We see that the oscillator current, current, such that the tank contributes change to a new value and injected current all havemust different phases enough phase shift to cancel the effect of . Note that, if the buffer and of tions. University of California, Berkeley Fig w if D be en contribute no phase shift, then the drain current m must remain in phase with under all condi- re Slide: 9ta Injection Locked Oscillator Phasors 0 Itank Vtank = Itank ZT (!1 ) Itank = Iosc + Iinj Itank j Iosc e Iosc 0 Iinj 6 Iosc = 6 Vtank = 6 Itank + 0 Iinj that the frequency of the injection signal determines the • Note extra phase shift Φ of the tank. This is fixed by the frequency 0 • • Ali M. Niknejad offset.! The current from the transistor is fed by the tank voltage, which by definition the tank current times the tank impedance, which introduces Φ0 between the tank current/voltage. ! The angle between the injected current and the oscillator current θ must be such that their sum aligns with the tank current. University of California, Berkeley Slide: 10 Injection Geometry sin 0 cos(⇥/2 = Itank Itank B ) = sin( ) = Iinj Iosc Iinj sin ⇥0 = sin( ) Itank Iinj sin( ) sin ⇥0 = = j |Iosc e + Iinj | B A B 0 Iinj sin( ) 2 + I 2 + 2 cos I Iosc osc Iinj inj Iinj geometry of the problem implies the following constraints • The on the injected current amplitude relative to the oscillation • amplitude.! The maximum value of the rhs occurs at: Iinj cos = Iosc Ali M. Niknejad sin = 2 Iosc 2 Iinj Iosc University of California, Berkeley sin 0,max Iinj = Iosc Slide: 11 Locking Range the edge of the lock range, the injected • At current is orthogonal to the tank current. ! phase angle between the injected current • The and the oscillator is 90° + Φ ! lock range can be computed by noting that • The the tank phase shift is given by 0,max tan tan 0 2Q = (⇥0 ⇥0 ( Ali M. Niknejad 0 0 2Q = (⇥0 ⇥0 ⇥inj ) Iinj ⇥inj ) = = Itank Iinj inj ) = 2Q Iosc Itank Iosc Iinj 2 Iosc 2 Iinj 0 1 0 1 2 Iinj 2 Iosc Maximum Locking Range Iinj University of California, Berkeley Slide: 12 Weak Injection Locking Range first derived these results in a celebrated paper [Adler] • Adler under the conditions of a weak injection signal. ! results for a large injection signal were first derived by • The [Paciorek] and then re-derived (as shown here) by [Razavi]! • Under weak injection:! I I ! inj ! Iinj sin( ) Iosc sin ⇥0 ! ! ! ! ! osc Iinj 2Q sin ⇥0 = sin( ) ⇥ tan ⇥0 = (⇤0 Itank ⇤0 2Q Itank sin( ) = (⇥0 ⇥0 Iinj ⇤inj ) ⇥inj ) the edge of the locking range, the angle reaches 90°, and the • At injected signal is occurring at the peaks of the output, which cannot produce locking (think back to the Hajimiri phase noise model) ( Ali M. Niknejad 0 Iinj inj ) = 2Q Itank 0 University of California, Berkeley Slide: 13 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 39, NO. 9, SEPTEMBER 2004 Injection Pulling Dynamics , and (15) Source: [Razavi] ains phase modula- Fig. 6. LC oscillator under injection. now that the oscillator is under injection so that phase shift can Suppose be oscillator signal feeding the tank can be written as ! antaneous input freEquating this result to , we obtain ! VX = Vinj,p cos ⇥inj t + Vosc,p cos(⇥inj t + ) ! VX = (Vinj,p + Vosc,p cos ) cos ⇥inj t Vosc,p sin sin ⇥inj t (23) (16) ! • This We canalso benote written as athat cosine with a phase shift! • from (19) slowly-varying ), ! ection phenomena. V = Vinj,p + Vosc,p cos cos(⇤ t + ⇥) X inj ! cos ⇥ Vosc,p sin tan ⇥ = Vinj,p + Vosc,p cos • Which allows us to write the output as m shown in Fig. 6, Vinj,p + Vosc,p cos Vout = cos ⇤inj t + ⇥ + tan e input. The output cos ⇥ having a carrier frewords, the output is Ali M. Niknejad University of California, Berkeley sibly time-varying) 1 ⇤ 2Q ⇤0 ⇤0 (24) ⇤inj (25) d⇥ dt ⇥⌅⇥ Slide: 14 Injection Pulling Dynamics [cont] have assumed that the phase shift through the tank is given • We by the simple expression derived earlier where the instantaneous frequency is! ! ! ! 2Q ⇥ ⇤0 tan ⇤0 ! d ⇥+ dt ⇥ d⇥ ⇤ dt • Ifto:!the injection signal is weak, then the previous result simplifies ! ! Vout = Vosc,p cos ⇥inj t + + tan 1 ⇤ 2Q ⇥0 ⇥0 ⇥inj d dt ⇥⌅⇥ must equal to the output voltage, or the phase shifts • Which must equal ⇥ + tan Ali M. Niknejad 1 ⇤ 2Q ⇤0 ⇤0 ⇤inj University of California, Berkeley d⇥ dt ⇥⌅ = Slide: 15 Pulling [cont] • These equations can be manipulated into a form of Adler’s equation:! ! ! d = ⇥0 dt ⇥inj ⇥0 Vinj,p sin 2Q Vosc,p ! ! ! d = ⇥0 dt ⇥inj ⇥L sin L Vinj,p 2Q Vosc,p 0 equation describes the dynamics of the phase change of the • This oscillator under injecting pulling. If we set the derivative to zero, • • we obtain the injection locking conditions (same as before).! Notice that maximum value of the rhs is quite small, which means that the rate of change of phase is slow ! This equation can be used to study the behavior of locking signals outside the lock range. Note that this equation agrees with our graphical analysis: d =0 dt Ali M. Niknejad University of California, Berkeley Slide: 16 Pull-In Process (t) = 2 tan 1 ⇤ 1 sin cot 0 tanh 0 0 ⇥L cos 2 = sin 1 ⇥0 0 (t ⇥⌅ t0 ) ⇥1 ⇥L the steady-state phase shift between the injected signal • θand0 isthe active device signal and t is an integration constant that 0 • depends on the initial phase shift.! From this equation the lock-in time can be computed (it’s approximately an exponential process): 2 tL = ⇥L cos Ali M. Niknejad tanh 0 1 ⇤ 1 sin 0 tan cos 0 University of California, Berkeley L 2 ⇥⌅ + t0 Slide: 17 Phase Noise in Injection Locked Systems IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 39, NO. 9, SEPTEMBER 2004 input frequency deviates uction becomes less proeither edge of the lock g the impedance seen by o rely on the phase noise g. Since the lock range is atural frequency of oscilocess variations and poor noise due [Razavi] to injection locking. he edge of the lock range, Fig. 14. Reduction of phaseSource: slightly. For example, if Under % and the natural fre- a lock, the phase of the oscillator follows the phase of the % with process and tem-injection signal. If a “clean” signal is used to lock a VCO, thenat the phase noise would improve up to the locking range.! njection locking occurs 37) and the above obserAt the edge of the lock, the injected signal cannot correct for e noise falls from infinity the phase noise since it injects energy at a 90° phase offset, degradation in the phase where the signal has a peak amplitude . • • LOCKED OSCILLATORS with pulling in nominally Ali M. Niknejad Fig. 15. PLL under injection pulling. University of California, Berkeley Slide: 18 Fig. 8. Microstrip balun. Example: GSM Class E PA 964 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 34, NO Fig. 10. Output power and PAE versus frequency for Fig. 9. Output power, efficiency, and PAE versus supply voltage. 10 and 5 mil, respectively. A single-ended signal at port 1 can be converted to differential signals at ports 2 and 3 or vice versa. The edge-coupled microstrip lines and the discrete tuning capacitors are shown in the enlarged portion of Fig. 8. and V. Fig. 5. Illustration of the mode-locking concept. B. Mode-Locking Technique Fig. 11. Amplified GMSK modulated signal ( spectral emission Modemask. locking refers to the ) and the GSM Source: [Tsai]condition in which an self-oscillating circuit is coupled and forced to of the same PAE infrequency this regionasis an dueinput to thesignal, progressively more resulting in a VI. MEASUREMENT RESULTS prominent input power in driving the PAErequirement. definition. At This 2-V is reduction in theterm input supply, the PAE was measured to be 48%. Fig. A. 4. Power-Amplifier Schematic of thePrototype complete power amplifier. each stage of the amplifier by a pair of cross-coupl Fig. 10 shows the output power and PAE at two different devices, as shown in Fig. The two where input the volta Large single-ended output stage is hard to drive capacitance).! voltages(large across the range of 5. frequencies A 10-dBm input device was converted to supply of is phase, are the two output The is load mode as locked successfully. Thisvoltages. locking range differential signals, using a commercial balun (Murata amplifier Use the and PAoutput toapplied drive an oscillator, right? ! such a at the nodes isYes. designed that measured to beoutput 490 MHz, centering at about 1.9 GHz. LDB20C500A1900), then to itself! the PA. capacitors RFThat’s power and inductors and equivalent load, and larger verify its potential in practical communication output ports. Fig. 9 maximized shows a was measured at 50- transistors in phase to control the composite switch.applicaAs far a switches. In fact,injection thethe switch areto often inTo modulation. Use locking inject phase Need “off” mode-locking class-Ethe PAoperation was tested is with a Gaussian , measured at tions, the typical plot of the output power versus circuit is concerned, similar to the si size to reduce the on-resistance loss. The input capacitance of switch to turn off transmission. shift keying (GMSK) [21] modulated input signal. 1.98 GHz. The output power increases from 49 mW to 1.0 minimum version as shown in Fig. 1, except for two feat these transistors is usually tuned out by inductors. However, W monotonically as the supply is swept from 0.6 to 2 V and GMSK and its close relative, Gaussian frequency shift keying thearecurrent circulating at each tuned lo at gigahertz frequencies, beyond transistor size the (GFSK), constantoriginally envelope modulation schemes in which . The maximum is approximately proportional to a certain to assist switching of the other circu inductance values for tuning may become smallinformation to utilized is carried in the phase variation of the half signal, used in this caserequired is determined by the peak drain too voltage capacitance input can now be significan makingthe them well suitedattoeach switching power amplification. on chip, which estimatedthe to be slightly above 5ofVCalifornia, at 2-VBerkeley be realizable. In is addition, large gate-to-drain capacitance Ali M. Niknejad University Slide: 19 • • • c in Section 3.2 and hence only the design of the power oscillator is elaborated here. Example: Low Power Transmitter 4.3.1 Efficient Power Oscillator Design The schematic of the power oscillator is shown in Fig. 4.4. Ref Osc PA Power Osc Vdd L1 + V0 - For this design, n = 1 to 4 / Power Control Data / Power Control odulation transmitter MA (b) Injection locked transmitter L2 RL M2n-1 " " " M1 M2 " " " M2n C1 MB Vinj+ Vinj- ock diagram of (a) direct modulation TX and (b) injection locked TX MC Vctrl,inj n locked transmitter, the power amplifier is replaced by an efficient """ V V1 . A power oscillator is necessary since the FBAR oscillator cannot the antenna without degrading its Q-factor substantially. The power Source: [Chee] Fig. 4.4: Schematic of the injection locked oscillator. 4.9: Output spectrum power the oscillator is (left) free running (right) locked. en into the Fig. voltage-limited regimewhen to allow output voltage to swing a low-power radio, the overall transmitter efficiency is very • Inimportant. The PA output power is modest (~1mW), but since 4.10 shows the single sided lock-in range fL as a function of the bias current of the ply. This Fig. reduces the device loss (Ids*Vds) and improves its efficiency. 71 injection locking transistor MA. A higher bias current increases the transconductance of llator is self-driven and hence does not load the reference oscillator the overall efficiency should be large, the entire transmitter this also increases theshould power consumption of transistor M and M whichmore degrades the than 2-3mW. ! not consume overall efficiency. To minimize efficiency degradation, the lock-in range f can be By using injection locking one can reduce the power chosen to be ~7 MHz and the peak efficiency is reduced by only by ~1%. nna loads the power oscillator’s output tank and degrades its Q-factor. consumption of the driver stages and end up with a minimal oscillator suffers from a poortransmitter phase noise performance and an imprecise architecture. transistor MA and MB, which increases the injected signal and lock-in range. However, hus the pre-PA power, consisting of the reference oscillator power, is d Lock-in Range fL (MHz) • A B L 45 34 40 32 30 28 reference oscillator, whose oscillation frequency is stabilized by a high or. Ali M. Niknejad 25 26 20 Transmitter Efficienc ency. To obtain a stable 35 RF carrier, the power oscillator is locked to an 30 University of California, Berkeley 24 Slide: 20 Consider interconnection of two from the locked half mode 4.8GHz reference. the locked half the mode 4.8GHz reference. A ALC tanks as conventional single mode VCO fabricated as hown insingle Fig. 1. Each tank isisa also parallel LCascircuit, but they ntional mode VCO is also fabricated Fig.1 Capacitive-coupled parallelLC LCtank tank Fig.1 Capacitive-coupled parallel reference to show the power saving advantage of the nce to show the power saving advantage of the re coupled together through a coupling capacitor C3. By structure. ure. The most important feature for this coupled LC tank Example: Dual Mode VCO The most important feature for this coupled LC tank arying the value of coupling capacitor, differentis dynamic that it inherently has two resonantfrequencies. frequencies.AAsimple simple is that it inherently has two resonant Index Term – Coupled LC tank, dual-mode, henomenon be observed. calculation yields the following expression for the two ndex Term – can Coupled LC tank, dual-mode, calculation yields the following expression for the two resonant frequencies e-controlled oscillator, injection locking. resonant frequencies K2 % ! K2 " ! I. INTRODUCTION Eq. 1 $ $ # # K " ! K L H 2 % ! 2 I. INTRODUCTION Eq. 1 $L # $H # 2K 3 2K 3 2K 3 2K 3 Generation of a low phase noise spectrally pure tone where 2 Generation of a low phase noise spectrally pure tone where has been a major challenge for communication circuits + C3 C3 C1 C22 ( C32 Eq. 2a en a majorinchallenge for communication !+#C)) C" C " C % ( && % 4C 2 fabricated CMOS technology. The lack circuits of a high Q Eq. 2a ! # )) *3 L"1 3 L"2 1 L%2 2L&&1 '% 4 L31L2 ated inresonator CMOS technology. The lack ofconsumption a high Q in stable necessitates high power * L1 C 3L2 C 3L2 C1L1 'C 2 L1L2 the form ofnecessitates a phase-locked frequency synthesizer. Eq. 2b resonator highloop power consumption in As voltage-controlled oscillator, injection locking. K2 # % % % C L C L CL CL K 2 # 3 %1 3 %2 1 %2 2 1 L22 % C1LC1 2 K3 L #1C3CL 2 C3C 1 % we move to higher frequencies, the problem is exacerbated m of a phase-locked loop frequency synthesizer. As Eq. 2b Capacitive-coupled parallel LC tank due theFig.1 increasing powerthe consumption the prescalar Eq. 2c ve totohigher frequencies, problem is of exacerbated frequency dividers in the frequency synthesizer. Since the increasing power consumption of the prescalar Eq. 2c Fig.2 K 3 shows # C3C1 the % Cdifferential 3C2 % C1C2 dual-mode LC tank used digital logic isinoften employed to perform thisSince task, the ncy dividers theimportant frequency synthesizer. this design. LC tank coredual-mode is simply the The most feature for this coupledinFig.2 LC tank shows The the differential LC differential tank used power consumption increases as we operate at a closer logic is often employed to perform this task, the version of Fig. 1. The components values are carefully in this design. The LC tank core is simply the differential sfraction that itofinherently has two resonant frequencies. A simple the process f . Injection locked dividers consumption increasesT as we operate at a closer calculated and1.selected for desired resonant frequencies. L1 version of Fig. The components values are carefully consume less power, but have narrow locking range and alculation yields the following expression forandtheL2 two are on chip spiral inductors. The center tap n of the process fT. Injection locked dividers calculated and selected for desired resonant frequencies. L1 require an additional oscillator. connection of the two inductors is used as the dc current esonant frequencies me less power, but have narrow locking range and While multimode oscillator have been proposed andpath L2 which are on chipthespiral The center allows activeinductors. circuits presented at the tap two ebefore an additional oscillator. (a) [1] [2], in this paper we present a coupled LC connection of the two inductors is used as the dc current K % ! " ! K ports to share the same dc current. By terminating each While multimode have beenthat proposed 2 2 Eq. 1 the resistance, oscillator with#dualoscillator frequency outputs naturally pathport which allows active circuits presented at the two $ $ # with a negative generated for example by a L H [1] [2], in this paper we present a coupled LC provides a technique for the VCO and a2K ports to share the same dc current. By terminating each 2Kcombining cross-coupled active device, both oscillation modes can be 3 3 tor with dual frequency outputs that naturally frequency divider in a phase-locked loop. Typically, we port with a negative resistance, generated for example by a where es athe technique for combining the VCO andlower a mode to activated at the same time. This is the basic idea behind the use higher mode to drive a mixer and the cross-coupled active device, both oscillation modes can be dual-mode oscillator. 2 ncy divider in a phase-locked loop. Typically, we drive the PLL dividers. 2 activatedThe at the same LC time. This iscan thealso basic idea behind the coupled network benefit phase noise + ( C C C C C 3 3 1 2 3 Eq. 2a e higher mode!to#drive a mixer and the lower mode to )) " " % && % 4 performance. Analytical analysis shows that this higher dual-mode oscillator. heII. PLL dividers. DUAL-MODE L2WITH L2 INJECTION L1 ' LOCK L1L2 order network can can enhance the equivalent tank * L1VCO The resonant coupled LC network also benefit phase noise quality factor thereby analysis improving the that phasethis noise. An performance. Analytical shows higher C 3 DESIGN C 3 C1 C 2 Eq. way 2bnetwork DUAL-MODE WITH I%NJECTION intuitive of understanding thisthe approach is that K 2 VCO # % % LOCK order resonant can enhance equivalent tanka (b) The authors are with the Department LESIGN L 2 Lof2 Electrical L1 Engineeringquality “zero” is designed at the vicinity ofthe the resonant frequency, 1 D factor thereby improving phase noise. An dual-mode LC tank (b) Fig. 2 (a) Differential and Computer Science, University of California at Berkeley, shownway in Fig. so that it increases the roll-offisrate from intuitive of2(b), understanding this approach that a over frequency Eq. 2c Berkeley, CA 94720 USA. Email: dengzm@eecs.berkeley.edu K # C C % C C % C C impedance 3 3 1 3 2 1 2 the peak resulting in avicinity sharper of transition and a frequency, narrower Ali M.are Niknejad of California, Berkeley Slide: 21 thors with the Department of Electrical Engineering University “zero” is designed at the the resonant coupled tank has two resonant modes. • AFrom each port of the oscillator, one mode is • • dominant.! In a fully differential version shown to the right, the impedance variation with frequency is shown.! Can we build an oscillator that sustains both modes? Dual Mode VCO (cont) Source: [Deng] cross-coupled pairs are used to sustain each mode by • Two providing sufficient negative resistance. The PMOS side is • Ali M. Niknejad running at a lower frequency whereas the NMOS side runs at the higher frequency.! Transistors M3a/M3b are used for injection locking. University of California, Berkeley Slide: 22 Dual Mode VCO Spectrum injection locking, each mode runs independently. The • Without frequencies are not integrally related, so the unlocked spectrum contains • • Ali M. Niknejad not only the two modes and harmonics, but also every intermodulation component.! When the modes are locked, the intermodulation components disappear. The high frequency VCO is divided by two in this configuration.! More on injection locking dividers to come... University of California, Berkeley Slide: 23 ter 2: Overview of Electrical Clock Distribution 14 Clock Distribution Chapter 2: Overview of Electrical Clock Distribution 16 PLL Figure 2.7: igure 2.6: A buffered H-tree. A clock grid driven by buffers. Source: [Mahony] 2.3.1.3 Local distribution is completely symmetric to simplify the design and provide nominally • source of power consumption. Figures of merit include skew, The final level topology of distribution network is the local which is the portion o a clock in acommonly large chip isa clock a major challenge andlevel, a big kew (assuming no Delivering loading variations). The most used is a buff- the network that follows the clock pin. This network drives the final loads of the clock dis H-tree [7] which is shown in Figure 2.6. H-trees are an extremely popular choice at jitter, and power.! tribution and hence consumes the most power. As a rule of thumb, the power at the loca evel of the clock distribution because they are a simple pattern that efficiently and level is about one order of magnitude larger than the power in the grid global and regional lev A buffered H-tree or a grid are common approaches. The metrically covers large H-trees distance fromwith thethe PLL to notable the fur-exceptions being clock networks that use a els combined, only hasareas. skew andminimize largerthe capacitance. • low-impedance grid atthe the interconnect regional level [2]. clock pins (without using diagonal traces) and thereby minimize The layout of the local is generally included in the design of the macro block and cy. The number of buffer levels within the global network − which alsogrid determines is not the responsibility of global and regional clock network designer. Because of its rela tency − depends on the signal dispersion, loss and on the required power fanout. Ali M. Niknejad tively limited span, it is sufficient to use automatic layout for this portion of the clock University of California, Berkeley Slide: 24 ould be expected based on the delay between points on the clock network. Despite vantages, however, an analysis of the relationship between skew and interconnect Clock Distribution: Distributed ndicates that wire loss will limit the use of standing-waves in an on-chip, global distribution. This type of clock distribution also requires limiting amplifiers to con2.5: Directions in global clock distribution 27 he sinusoidal standing waves to digital levels, which could add additional skew and 2.5: Directions in global clock distribution l << λ VCO and loop filter Phase detector Regional Clock Distribution ÷N System Clk PD, LPF & CP Vc (to VCOs) Clock load gure 2.12: Figure 2.13: Clock distribution using a coupled array of PLLs [44]. Source: [Mahony] Standing-wave clock distribution [41]. VCO algorithm is used to avoid instability during the phase locking process. There are two main Coupling wires advantages to this topology. First, the PLLs filter the noise of the global H-tree and Coupled oscillator arrays replace it with the noise of the local VCOs, thereby reducing the jitter that accumulates in wave oscillators tune out the • Standing capacitance of the line and form a resonant the H-tree. The second advantage is that, like in [44], the skew is a function of the error in Figure 2.15: the phase detectors rather than the accumulated skew between branches of the H-tree. This Clock distribution using a coupled array of VCOs [48]. he research that has been described to this point generally concentrates on minimiz- e skew of a global clock distribution. However, based on the scaling analysis in means that the scaling of this type of distribution does not depend on the latency of the on 2.4, it appears that jitter may be more difficult to reduce for future high-perfor- network. e microprocessors. Several clock distributions based!on coupled oscillator arrays been proposed that have the potential to reduce both jitter and skew by eliminating A distributed approach locks an array of amounts of latency from the clock network. Some also reduce skew and jitter by VCO’s to it’s neighbors.! ying a phase-averaging effect that tends to reduce the impact of uncorrelated static The neighbors can also be injection locked to one another to eliminate the phase detectors. • • H-tree but rather on the scaling of the VCO and phase detector. The presence of the global 2.5.3.3 Coupled distributed oscillators H-tree also allows for low-frequency testing by bypassing the PLLs. The only drawbacks The last type of coupled-oscillator clock distributions uses coupled arrays of distr to this approach are the additional resources necessary for multiple PLLs and the comuted oscillators. The oscillators are distributed in the sense that the coupling wires are p plexity of synchronization. This approach has not yet been prototyped so no measured of the oscillators themselves, so their free-running frequency depends to some degree data is available. the geometry of the interconnects. The cooperative ring oscillator (CRO) clock distri 2.5.3.2 VCO arrays tion described in [49] uses overlapping ring oscillators. The frequency of the oscillat depends on both the buffer and interconnect delays around the ring. Figure 2.16 show The global clock distributions described in [47] and [48] are similar to the PLL array CRO grid and its electrical equivalent. The oscillators are allowed to run op designs, except that they use a single control loop with multiple VCOs. three-phase The clock distribu- and theybasic phase lock to each other due to mutual coupling between rings, similar tion shown in Figure 2.15 and described in detail here is based on [48],loop, but the same andaround [48]. the concepts are used in [47]. A control voltage is distributed to all of the[47] VCOs die to set their frequency. A clock signal is fed back from a regional clock tap (driven approach by a A similar is proposed in [50], which implements coupled arrays of rot Ali M. Niknejad University of California, Berkeley oscillators (Figure 2.17). This oscillator is similar to a ring oscillator but instead of usin 25int series of inverter stages, it uses cross-coupled inverters to provide shuntSlide: gain. The of the“keep-out” PMOS andregions, areas where the signal amplitude is too low to be tapped b the line, so they are optimized for maximum gd/cd. The relative sizes ered buffers. Thetovoltage standing-wave pattern for a portion of the grid is shown in Figu NMOS devices can also be optimized, but a good rule of thumb is to size them be Standing Wave Oscillators (SWO) roughly equal. Note that the largest magnitude occurs around the square portion of the grid and t nodes of the standing-wave are pushed onto the stubs. 4.2.3 Design example Single SWO (folded) 63µm:0.18 µm Clkinj Differential interconnect Cross-coupled pair Injection-locked cross-coupled pair Clock buffer 63µm:0.18 µm 14µm 14µm Chapter 5: Standing-Wave Clock Distribution Network 3.5mA 3.5µm 4µm Figure 5.3: Figure 4.8: 5.1.1 SWO coupling A resonant clock grid of coupled SWOs. SWO and transmission line cross-section for design example. ccp ccpof theccp ccp ccp This clock grid of coupled oscillators solves two fundamental problem negative resistance to sustain • The oscillation is distributed along the line. ! disadvantage is that the amplitude of • One the clock varies along the line.! can be injection locked together • SWO’s to form larger clock trees. accumulation of timing uncertainty and sensitivity to buffer delay. A A SWO is straightforward to design from (4.11) and (4.2). Table 4.1H-trees: lists the the parame- in spaced Chapter 2, H-trees accumulate timing uncertainty because the clock si ters that will be used to design a SWO with five equally sized andcussed equally cross-coupled pairs. The transmission-line cross-section (Figure 4.8) is optimized generatedfor bymina single source and then regenerated by each ccp buffer along the tree. ccp ccp ccp ccp the ground plane. in the grid locally generates the clock signal and only uses the imum loss given a total track width of 32µm and a distance of 3.5µm totrast, each SWO A unit cross-coupled pair (ccp) is defined to have NMOS and PMOS devices that are 18µm wide and 0.18µm long and is optimized for maximum gd/cd with 1.0mA of bias cur- Figure 5.1: Two coupled SWOs. Source: [Mahony] Multiple SWOs can be coupled together by simply connecting their transmission l Two coupled SWOs are shown in Figure 5.1. Ideally, the two oscillators are matche frequency and a transient current between the two oscillators brings them into per phase lock. If the oscillators are detuned, they will still lock if they are within their mu Ali M. Niknejad University of California, Berkeley locking range. A steady-state coupling current will keep them frequencySlide: locked,26 altho ROUFOUGARAN et al.: SINGLE-CHIP 900-MHz SPREAD-SPECTRUM WIRELESS TRANSCEIVER IN Quadrature Locked VCOs (QVCO) 270° 90° 0° 180° 0° 180° Fig. 20. (a) Q showing the re across the reso Source: [Rofoug] Fig. 19.VCO’s Quadrature oscillator comprises of extra cross-coupled LC oscilTwo are coupled togethera pair using transistors as •lators synchronized in frequency. are identical, we expect that the shown. If the oscillators amplitude and frequency of oscillation should be identical.! Becausebalanced of the phase of the outputs coupling, be shown recently, quadrature areit can obtained from that two they lock in quadrature... • Ali M. Niknejad cross-coupled relaxation oscillators [30]. Another oscillator consists of two LC biquad inBerkeley feedback [31]. Four-stage Universityfilters of California, Slide: 27 UM WIRELESS TRANSCEIVER IN 1- m CMOS—PART I QVCO: Quadrature Lock 525 Source: [Rofoug] that the tank “A” (a) is driven by the tank voltage VA plus (b) • Note the tank voltage of “B”. ! Fig. 20. (a) Quadrature oscillator redrawn, emphasizing its symmetry and rightthe tank, though, is driven by the voltage V phases and voltage -V . ! • The showing resonator currents; and (b) relative of the voltages across the that resonators required forand symmetric operation. the LC tanks FETs are identical, then the • Assuming phasor currents flowing into the tanks must have equal B pled LC oscil- magnitude: |vA + vB | = | |1 + ej | = |1 d from two Ali M. Niknejad cos = 0 ⇥ A vA + VB | ej | = ±90 University of California, Berkeley Slide: 28 (a) (b) QVCO: Lead/Lag Ambiguity Fig. 20. (a) Quadrature oscillator redrawn, emphasizing its symmetry and showing the resonator currents; and (b) the relative phases of the voltages across the resonators required for symmetric operation. r of cross-coupled LC oscil- are obtained from two 30]. Another oscillator edback [31]. Four-stage at taps two stages apart lthough apparently not ite low phase noise in ture oscillator. It comSource: [Rofoug] d above, labeled A and ted in parallel with! the Oscillator A is directNoteFig.that the tank current/voltage has a 90° 21. Magnitude and phase of a realistic resonator’s impedance, show- relation, or the llator B, and the output ing three possible oscillation frequencies. The oscillator selects the highest of the impedance injection strength). Three because the feedback loop is gain±45° is largest (equal here. Oscillator A (Fig. phase 19). frequency frequencies satisfy this constraint, but f3 has the highest loop ctly the same frequency y the coupling topology. gain.!circuit impedance is and its phase is either 45 plains how, owing only or 45 (Fig. 20). In an LC resonator with series loss in the It’s clear that there are two possible solutions: lead or lag in n quadrature. inductor, these phases appear at three different frequencies, , phase between “A” and “B”.! ctively, are the steady, and (Fig. 21). However, among them only is stable, with reference polarities because at this frequency the impedance is largest, and thus the In any real oscillator, the two oscillators are not perfectly rrent into the tuned load feedback factor in the oscillator is strongest. At the phase symmetric, and it can be shown that there is into of the resonator’s impedance is 45 , which means that is only one unique solution (where the loop gain is highest and the net phase shift the differential average must lead by 90 , as is shown in Fig. 20. Note also that the ET’s. Arguing purely by oscillation frequency is higher than the resonance of the tuned Ali M. Niknejad University of California, Berkeley s in the two circuits are • • • Slide: 29 measurement results for a prototype of thethe S-QVCO fabricated natural tank resonance frequency Further, the same LC: noise also show an oscillation in a standard 0.35- m CMOS process which modulates Fig. 6. Fair phase-noise comparison between P-QVCO and S-QVCO. , whic YSIS AND DESIGN OF A 1.8-GHz CMOS LC QUADRATURE VCO frequency of 1.8 GHz, a tuning range of 18%, a phase noise of transconductance e P-QVCO,140 in thedBc/Hz presence ofor different . less values at a for 3-MHz offset frequency across the we obtain , tuning range, and an error ofoscillation at most 0.25 frequencies and , both differing f Linear model ofequivalent QVCO isphasepossible ption, there will be noconsumption doubt that theof LC: the natural tank resonance for ashown. current 25 mA from a 2-V power supply. frequency The loop gainS-QVCO is easily QVCO Loop Gain • m the P-QVCO.5 computed and the frequency at which the loop gain is zero is To estimate the effect on th APPENDIX A These equations can be simplified II. A SIMPLIFIED QVCO MODEL noting that the oscillation frequency.! appears squared in (17) duces a linear model for the P-QVCO, where that the is offoscillation frequencies to define InNotice this appendix, weoscillation find the possible in the expres the transconductance of the negative-resistance resonance. results higher for the linearized This QVCO circuit in in Fig. 7. The loop gain is easily d the transconductance of the coupling pair phase noise. calculated as ng to this figure and also in the following, we • nverted baseband signals and LO leakage at 1.75 GHz carrier Fig. 7. Linear model for a QVCO. URE56 VCO 1745 dB). ge and current signals to be fully differential: Source: [Andreani] wing into the tank is the difference between the These equations can be simplified noting that As shown in Appendix A, the oscillation frequency retwopossible branches of the differential stage. As a LC oscillation frequencies and , both differing from and therefore . Using (20), we can approxim and assuming that sults slightly displaced from the tank resonance isthe thenatural loss resistance of one half-tank. (17) LC: tank resonance frequency to ( inner square root in (18) asdepends on . According by anthe offset , whose magnitude . This can According to Barkausen’s criteria, thealso circuit oscillates when , which can be neglec this term is much than intuitive be explained in thelarger following, way. Referring to baseband and LO leakage at 1.75 GHz iscarrier satisfied; further, there are in two thesignals condition in Fig. 7,using the losses tankare balanced by a current in Finally, (19) and the approximation B). matters even further, an additional variable is the value of the phase , which is provided by withfor , , we arrive at valid or widths, . The results shown in . The tank is now lossless, and the current from acts on d when both P-QVCO and S-QVCO shared the same value ideal (18) LC-parallel. This second current, , is thus in quadrar, can be largely reduced for the P-QVCO, in which an . Using (20), we can approxim and assuming that e decreases by approximately 2 dB in the region, but ture with , which in turn implies that and are phase According to ( the inner in (18) l decibels in the region. It should be noted that a lower shifted . Fig.root 8 shows the as phasors of the. voltage across by square ows the P-QVCO to achieve maximum oscillation These equations can abehigher simplified noting that , tank. whichTocan betheneglec thistank, termand is of much larger than the the currents entering the find red to the S-QVCO, or, when the oscillation frequency and the which is the same as (2). Finally, using and the, we approximation M. Niknejad of California, Berkeley (19)and 30 consider the loop in Fig.Slide: 7 as eAli same for both P-QVCO and S-QVCO, the capacitance University in lation between Intuitive Derivation of Quadrature VCO important observation is that each VCO is loss-less due to • The the -Gm that balances the loss of the Rp. ! injected currents, therefore, see an ideal LC tank slightly off • The resonance, which implies an impedance with 90 degrees of phase • shift, which implies the tanks are in quadrature! To calculate the phase shift, we note the loop gain is unity 1 GM c =1 2| !|C GM c !=± 2C Ali M. Niknejad University of California, Berkeley Slide: 31 both transistors h Fig. 2. • • • Ali M. Niknejad QVCO in the Literature Schematic view of the quadrature VCO presented in [7]. To see how the (SSB) upconvers so that the overal very difficult to m into the ratio of th image band [to b In the case of the of 0.1% between IBR of 70 dB for and to 49 dB for Source: [Andreani] quickly larger wh is weak Several modifications to the QVCO have been proposed P-QVCO for Fig. 3. Schematic view of the quadrature VCO proposed in this work. improved performance! easy to check tha In particular, it has been shown that if a weaker coupling isdecreasing . Th The present analyzes alternative waycircuit [16] oflocks cross closer noise performanc introduced, thepaper phase noise an improves (the differential VCOs obtain a QVCO, in which quadrature the error performanc tocoupling the tanktworesonance), but attothe cost of imperfect is placed in series with , rather P-QVCO present coupling transistor generation! in parallel (Fig. quadrature 3). This choice is motivated by the connoise FoM, the h A than series connected generation scheme proposed in the phase P-QVCO is responsible for a large choosing that has better bysideration [Andreani] noise performance. contribution to the overall phase noise, and connecting to unity. Slide: 32 University of California, Berkeley in series with , in a cascode-like fashion, should greatly CK out,I Static Frequency Dividers Divide-by-2 Circuit (Johnson Counter) CK out,Q tD Q Register LATCH 1 LATCH 2 D D Q clk IN IN ( Q clk Q OUT Q OUT Fig. 5.22 (a) Typical static divider, (b) its waveforms TIN IN dition. As frequency goes up, the idle time d OUT VDD ! Achieves frequency division by clocking twoRlatches R This is a simple divider structure uses a • master/slave (i.e., a register) topology.in! negative feedback ! Latches may be implemented in various ways Two latches are cascaded into a • negative according speed/power requirements feedbacktoloop (the output will D • therefore toggle). ! Since two clock cycles are required to pass the data from one latch to the next, it naturally divides by 2. D in M 1 D M2 Dout M3 D in M4 CKin CKin M6 M5 M.H. Perrott Ali M. Niknejad RC CKin MIT OCW University of California, Berkeley (a) Slide: 33 device capacitance of the former can be absorbed as part of the latter. This topology thus becomes attractive and popular at moderate to high frequencies. Miller Divider (Regenerative) ω in , 3 ω in 2 x (t ) 2 LPF y (t ) ω in 2 output signal of the feedback loop is mixed with the input • The signal. The output of the (ideal) mixer has the sum and Fig. 5.25 Regenerative divider. components. ! Let usdifference first examine the division behavior and estimate the operation range. For the difference component (due to the LPF) the circuitOnly to divide properly, the loop gain atisωamplified in /2 must exceed unity. Redrawing and up. !with simple RC filter and input amplitude A, we have the divider in gained Fig. 5.26(a) • the loop gain is greater than one and the loop phase is zero • Ifdegrees, ! ! the system regenerates βA ! ω !the input.! )! ≥ 1, (5.36) !H( j • The output frequency2in steady2 state must therefore satisfy: in fout fout where β denotes the conversion gain= of f the It can be further derived that inmixer. " 1$ # 2 2fout = ωinfin 2 A≥ 1+ 2 ≥ . (5.37) β 2 ωc β Ali M. Niknejad University of California, Berkeley Slide: 34 β xy L C R ω in t = B cos M5 2/ β y (t ) ω in t M6 M ω in4 M3 Miller Divider Circuit Details ω in 2 2 Vin 2ω n Op. Range A B 190 (b) (a) VDD L1 C1 M2 M1 L L2 Vout Y X C2 (c) VDD Vout L L M 6 with bandpass filter; (b) its input sensitivity, (c) typical CMOS M 5 Regenerative divider Fig. 5.28 (a) M3 M4 M4 M3 realization. V M M5 in A M6 A B 5 B M4 −I inj M1 It is interesting to note input ports, that leads M 2that a mixer has two V M1 M 2 to two posVin in M 1 sible configurations of Miller dividers. As illustrated in Fig. 5.29, the output could (c) ( (a) 8 (a) Regenerative divider with bandpass filter; (b) its input sensitivity, (c) typical CMOS ion. Fig. 5.30 (a) Type II regenerative divider, (b) redrawn to shown injecti LO Port LO Port s interesting to note that ports, that leads V ina mixer has two input Filter V outto two V out be posredrawn as that inFilter Fig. 5.30(b). It in fact resembles an i onfigurations of Miller dividers. As illustrated in Fig. 5.29, the output(which could will be discussed in the next section): M3 and M4 for RF Port LO Port LO Port Filter V out (a) Filter and M5 and M6 appear as diode-connected transistors to lo RFincrease Port the locking range. The differential injection in and lieved to help V inenlarge the range of operation to some extent self-resonance frequency of the circuit if (W /L)3,4 > (W /L) V out (b) • Use a double-balanced Gilbert cell mixer to realize divider in Fig. 5.29 Regenerative divider with the output fed back to (a) RF port, (b) LO port. RF Port Ali M. Niknejad RF Port V in 5.8 Injection-Locked Dividers University of California, Berkeley Slide: 35 Injection Locked Dividers [IL-Div] Fig. 2. Model for a free-running LC oscillator. . terms with freq an th-order s intermodulation o equal to which is the co written as injection locked divider is nothing but an injection locked • An system where the input frequency is at a harmonic of the freeFig. 3. Model for an injection-locked oscillator. Using a com and applying th be written as running frequency of the oscillator.! Measurements on a single-ended ILFD (SILFD) are compared Model the system a non-linearity f(e) and a bandpass with simulations. The as simulation results of a differential ILFD transferare function H(ω).! (DILFD) reported as well. Assume that the free-running loop has a stable oscillation frequency. The system is injection locked to a super-harmonic NJECTION-LOCKED OSCILLATORS II. free-running MODEL FOR Ifrequency.! of the An non-linearity LC oscillator in can modeled as a nonlinear block The thebeloop must create intermodulation products thatby falla infrequency the passband of the loop. , followed selective block (e.g., an RLC or • • • Ali M. Niknejad , in a positive feedback loop as shown in Fig. 2. tank) The nonlinear block models all the nonlinearities in the oscillator, including any amplitude-limiting mechanism. To University of California, Berkeley Slide: 36 IL-Div Analysis the injection signal is a sinusoidal signal which is • Suppose added to the oscillator’s signal (at a sub-harmonic of the injection). The non-linearity acts on both signals and is filtered by the RLC circuit:! ! vi (t) = Vi cos(⇥i t + ) vo (t) = Vo cos( ! ! u(t) = f (e(t)) = f (vo (t) + vi (t)) ! o t) H0 H( ) = 1 + j2Q r r can be shown that if the output signal contains various • Itharmonics and intermodulation terms which can be written as:! ! ! u(t) = m=0 n=0 ! • where K m,n Ali M. Niknejad Km,n cos(m⇥i t + m ) cos(n⇥0 t) is the intermodulation component of f(vi+vo) University of California, Berkeley Slide: 37 IL-Div Fourier Analysis • To see this, write the signals in the following form:! ! vi = Vi cos( ) ! vo = Vo cos( ) ! f (e) = f (vi + vo ) ! means that f is periodic in α and β. For every β define a • which periodic function g(α) as follows! ! g( ) = f (vo + Vi cos( )) ! g( + 2⇥) = g( ) g( ) = g( ) • Note that:! ! • So that we can write: g( ) = Lm (⇥) cos(m ) m=0 Ali M. Niknejad 2 1 L0 (⇥) = f (Vo cos(⇥) + Vi cos( ))d 2⇤ 0 1 2 Lm (⇥) = f (Vo cos(⇥) + Vi cos( )) cos(m )d ⇤ 0 University of California, Berkeley Slide: 38 IL-Div [Fourier Analysis cont.] • But since L m is a periodic and even function of β we can write:! ! ! ! ! Lm ( ) = 2 1 Km,0 = Lm ( )d 2⇥ 0 1 2 Km,n = Lm ( ) cos(n )d ⇥ 0 Km,n cos(n ) n=0 ! • which results in:! ! ! f (vi + vo ) = Km,n cos(m ) cos(n⇥) m=0 n=0 ! that the tank filters out all frequencies except the • Assume ones around ω . That means that only intermodulation terms o that fall at ωo are relevant: |m Ali M. Niknejad i n 0| = 0 University of California, Berkeley Slide: 39 IL-Div [Fourier cont] the injection signal is an N’th superharmonic, then only the • Ifintermodulation terms! n = Nm ± 1 ! a frequency equal to 1/N the incident frequency. This • possess means that our summation can be written in terms of m as! ⇥ 1 u 0 (t) = K0,1 cos(⇥0 t) + Km,N m±1 cos(⇥o t + m ) 2 m=1 ! ! complex notation and applying the oscillation condition, • Using the output signal can be written as ⇥ ⇤ j⇥o t H e 1 0 j⇥0 t jm vo = Vo e = K + K e 0,1 m,N m±1 ⇥ 2 1 + j2Q ⇥r m=1 ⇤ ⌅ ⇥ ⇥ 1 ⇧ Vo 1 + j2Q = H0 K0,1 + Km,N m±1 ejm 2 m=1 r Real Part: Imag Part: Ali M. Niknejad ⇥ ⇤ ⇥ 1 Vo = H0 K0,1 + Km,N m±1 cos(m ) 2 m=1 ⇥ ⇥ H0 2Vo Q = Km,N m±1 sin(m ) ⇥r 2 m=1 University of California, Berkeley ⇥ Slide: 40 IL-Div Locking Range two equations can be solved for the unknown oscillation • The amplitude and phase for any incident amplitude and incident frequency, or any offset frequency:! ! = ( i /N ) ! r ! • The second equation can be re-written as:! ! ! ! ⇥= ⇥A H0 2Vi ⇥ ⇤ ⇥ Km,N m±1 sin(m ) m=1 • where Adler’s locking range has been identified:! ! ! ! A Vi = 2Q Vo r • Unlike static dividers, the locking range is limited. Ali M. Niknejad University of California, Berkeley Slide: 41 IL Divide by 2 Circuit equations can be solved analytically for a divide by 2 with • The cubic non-linearity! ! ! ! ! ! ! ! ! f (e) = a0 + a1 e + a2 e2 + a3 e3 2Q ⇥ sin( ) = H0 a2 Vi ⇥r ⇥ H0 a2 Vi | sin( )| < 1 < ⇥r 2Q ⇧ ⇤ ⇥⌅ 4 1 3 Vo = 1 H0 a1 + a3 Vi2 + a2 Vi cos( ) 3 a3 H0 2 range is improved by using a large H0/Q or a larger • Locking injection amplitude. For an LC oscillator, this is equivalent to using a larger inductor:! ! ! H0 = L Q impedance node is a convenient place to inject the signal • Ato high limit the injection power. Ali M. Niknejad University of California, Berkeley Slide: 42 Fig. 7. Schematic of the single-ended injection-locked frequency divider. IL-Div Circuit Details a first-order differential (23) to the output phase (23) ig. 6, it is clear that an ion as a first-order PLL. shaped by the low-pass unction, and the output he incident signal within . However, unlike a of an ILO is a function Fig. 8. Schematic of the differential injection-locked frequency divider. ger for a larger incident The injection signal is applied as a current to the tail of a cross• coupled differential oscillator. ! nsfer function is a little ity, the biasing circuitry is not shown in this figure. A Colpitts oscillator currents forms the core of the SILFD. incident signal is of M1/M2 are aThe non-linear function of e ILO itself. Within thetransistor • The injected into (feedback) the gate of M1. Transistors M1 and current M2 are used output signal and the injected of M3.! LO is suppressed the by the mainly to provide more isolation between the input dent power. Outside the in cascode, Interestingly, even in the absence of an injection signal, node • and output. Transistor M2 is sized to be smaller than M1 by n increases by 20 M3 dB per is moving at twice ω phase noise region is Ali M. Niknejad o almost a factor of three to reduce the parasitic capacitance at the output node (drain ofBerkeley M2). As a result, a larger University of California, Slide: 43 thebezero crossings theorinput at into to injection can obtained fromof(6) (8): fall on the peaks of the output, oscillator. If node and is equivalent switch abruptly and theofca little phase synchronization occurs. The lock range in this case nodeis the mixer conversion gain) at, and (9) can dir is neglected, then be NG IN OSCILLATORS 1417 can be obtained from (6) or (8): oscillator. If and switch abruptly and the c (9) , and (9) can b node is neglected, then IL-Div Intuitive Picture (9) The subtle difference between (6) and (9) plays a critical role in If referred to the input, this range must be doubled: quadrature oscillators (as explained below). The betweenphase (6) and (9) playsacross a critical Fig.subtle 4 plotsdifference the input-output difference the role lockin If referred to the input, this range must be doubled quadrature oscillators (as explainedinjection below). locking to range. In contrast to phase-locking, Fig. 4 plots the input-output phase difference across the lock mandates operation away from the tank resonance. range. In contrasttotoQuadrature phase-locking, injectionWith locking 1) Application Oscillators: the to aid of a mandates frommodel the tank resonance. feedback modeloperation [13] or aaway one-port [14], it can be shown Confirmed by simulations, (13) represents the upp 1) Application to Quadrature Oscillators: Withoscillators the aid of a that “antiphase” (unilateral) coupling of two identical the lock range of injection-locked dividers. feedback model [13] or a one-port model [14], it can be shown forces them to operate in quadrature. It can also be shown [14] Confirmed by simulations, (13) represents the up that “antiphase” (unilateral) coupling ofsee twoshifts identical oscillators that this type ofIntuitively coupling (injection locking) the the frequency we can that injection at the of the MOSdividers. the lock rangetail of injection-locked forces them tocross-coupled operate in quadrature. It can also be shown III. INJECTION PULLING from resonance so that each tank produces shift of [14] pair isa phase mixed due to the switching action of M1/ that this type of coupling (injection locking) shifts the frequency M2.! Fig. 5. (a) Injection-locked divider. (b) Equivalent Ifcircuit. the injected signal out of, but III. frequency INJECTIONlies PULLING from resonance so that each tank produces a phase shift of from the lock range,current the oscillator is “pulled.” W For a strong mixing signal, 2/π (10) component of this will If theby injected signalthe frequency lies out of,osci bu behavior computing output phase of an flow into the tank, at frequency shift of harmonics of ω o. In is “pulled.” W thealock range exceeds (9) by 3.3%. In other from the lock range, the oscillator low-level injection. (10) particular, a signal at 2 ω will be down-converted intotheω o o, phase of an os behavior by computing output phase difference between its input and output, words, for a 90 where denotes the current injected by one oscillator into where the tank has high impedance. This signal therefore low-level injection. an injection-locked oscillator need not operate at the edge of the a Tank the other and (5) is the current produced by the core of each A. Phase Shift Through . Equations experiences a large loop gain and can lock the oscillator. where Usedenotes the current injected by one oscillatorshift into lock range. oscillator. of (5) therefore gives the required frequency For subsequent derivations, we need an expres A. Phase ShiftanThrough a Tank is the current produced by the core of each the other and as 2) Application to Dividers: Fig. 5(a) shows injecphase shift introduced by a tank in the vicinity of re oscillator. Use of (5)tion-locked therefore givesoscillator the required frequency shift stage [15]. While operating as a second-order For subsequent derivations, we need parallel tank consisting of ,an ,expre and as shift nonlinear function by to a tank in the vicinity of (11) as aaphase (8) previous work has treated the circuit phase shift introduced of parallel tank consisting of , , and derive the lock range [15], it is possible tosecond-order adopt a time-variant (11) aat phase shift of to the Ali M. Niknejad University of California, Berkeley Slide: 44 view to simplify the analysis. Switching a rate equal Interestingly, (9) would imply that each oscillator is pushed • • Miller Divider / Injection Locked Divider 190 Jri Lee VDD VDD L Vout L L M4 M3 M4 M5 M6 A M5 B Vin M 1 M2 (a) L M3 M6 −I +I inj M1 inj M2 Vin (b) Fig. 5.30 (a) Type II regenerative divider, (b) redrawn to shown injection locking. same circuit topology can be seen to be an injection • The locked divider or a Miller divider.! devices M5/M6 are not needed in the normal injection • The locked divider, but here they act to lower the Q of the tank, be redrawn as that in Fig. 5.30(b). It in fact resembles an injection-locked divider (which will be discussed in the next section): M3 and M4 form a cross-coupled pair, and M5 and M6 appear as diode-connected transistors to lower the Q of the tank and increase the locking range. The differential injection in such a manner is believed to help enlarge the range of operation to some extent. It is possible to find a self-resonance frequency of the circuit if (W /L)3,4 > (W /L)5,6 [22]. • Ali M. Niknejad increasing the lock range.! A Miller divider can be designed so that it does not oscillate in 5.8 Injection-Locked the absence of an inputDividers signal. The operation speed of dividers can be further boosted up if we simplify the structure at the circuit level. Since a cross-coupled VCO provides ultimate simplicity in generating differential oscillation, one may think of injecting a periodic signal (apUniversity of California, Berkeley proximately twice the VCO free-running frequency) into the common-mode point Slide: 45 References [Razavi] B. Razavi, “A Study of Injection Locking and Pulling in Oscillators,” IEEE J. of Solid-State Circuits, vol. 39, no. 9, Sept. 2004, pp. 1415-1424. ! [Adler] R. Adler, “A Study Locking Phenomena in Oscillators,” Proc. of the I.R.E. and Waves and Electronics, June 1946, pp. 351-357. [Paciorek] Ali M. Niknejad L. J. Paciorek, “Injection Locking of Oscillators,” Proc. of the IEEE, vol. 53, no. 11, Nov. 1965, pp.1723-1728. [Tsai] K.-C. Tsai and P. R. Gray, “A 1.9-GHz, 1-W CMOS Class-E Power Amplifier for Wireless Communications,” JSSC, vol. 34, July 1999 [Chee] Y. H. Chee, Ultra Low Power Transmitters for Wireless Sensor Networks, Ph.D. Dissertation, U. C. Berkeley, Spring 2006. [Deng] Z. Deng, A.M. Niknejad, “9.6/4.8 GHz dual-mode voltage-controlled oscillator with injection locking,” Electronics Letters, vol. 42, Nov. 9 2006, pp. 1344-1343. [Mahony] Frank P. O’Mahony, 10GHZ GLOBAL CLOCK DISTRIBUTION USING COUPLED STANDING-WAVE OSCILLATORS, Ph.D. Dissertation, 2003, Stanford University [Rofoug] A. Rofougaran et al, “A Single-Chip 900-MHz Spread-Spectrum Wireless Transceiver in 1- m CMOS—Part I: Architecture and Transmitter Design,” IEEE J. of Solid-State Circuits, vol. 33, no. 4, April 1998, pp. 515-533. [Andreani] P. Andreani et al, “Analysis and Design of a 1.8-GHz CMOS LC Quadrature VCO”, IEEE J. of Solid-State Circuits, vol. 37, no. 12, Dec. 2002, pp. 1737-1747. [Rategh] H. Ratech and T. H. Lee, “Superharmonic Injection-Locked Frequency Dividers,” IEEE J. of Solid-State Circuits, vol. 34, no. 6, June 1999, pp. 813-821. University of California, Berkeley Slide: 46