Chapter 3 - Access IC Lab

advertisement

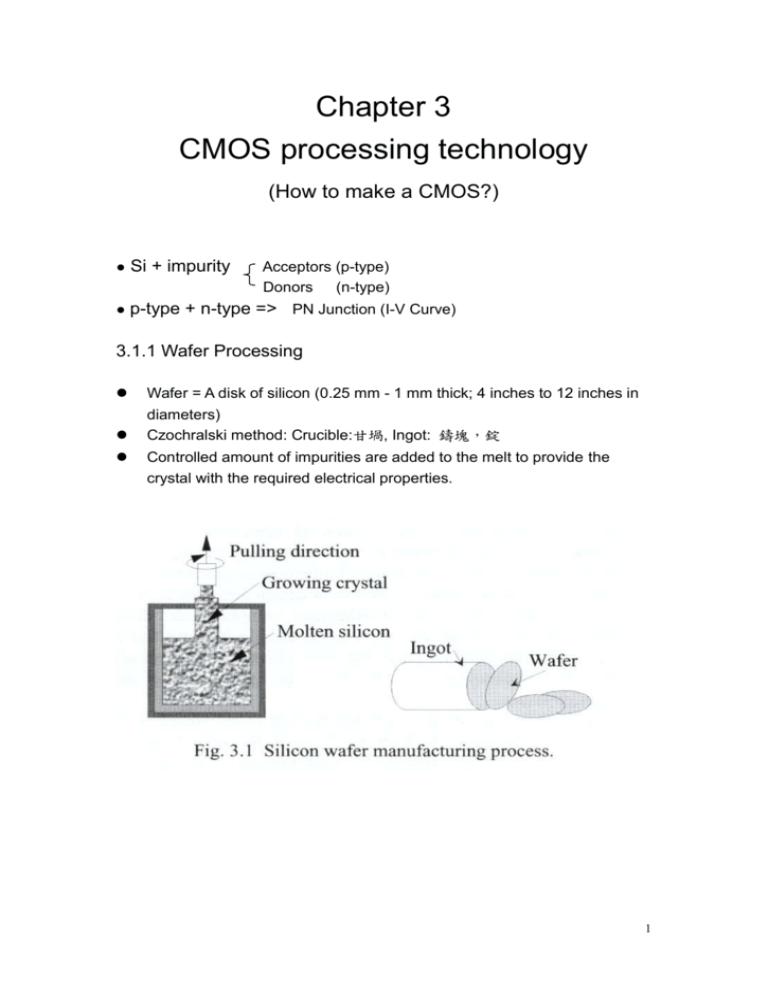

Chapter 3 CMOS processing technology (How to make a CMOS?) ● Si + impurity Acceptors (p-type) Donors (n-type) ● p-type + n-type => PN Junction (I-V Curve) 3.1.1 Wafer Processing Wafer = A disk of silicon (0.25 mm - 1 mm thick; 4 inches to 12 inches in diameters) Czochralski method: Crucible:甘堝, Ingot: 鑄塊,錠 Controlled amount of impurities are added to the melt to provide the crystal with the required electrical properties. 1 3.1.2 Oxidation (Produce Isolation Layer SiO2) Oxidation of silicon is achieved by heating silicon wafer in an oxidizing atmosphere such as oxygen or water vapor. - Wet Oxidation: Water Vapor -> rapid process (900º-1000ºc) - Dry Oxidation: Pure oxygen -> slow process (1200ºc) SiO2 layer grows almost equally in both vertical directions. 3.1.3 Epitaxy, Deposition, Ion-implantation, and Diffusion ● To generate silicon that contains varying portions of donor or acceptor impurities. A. Epitaxy (長晶): grow a single crystal film on the silicon surface. B. Deposition: Evaporate dopant material onto the silicon surface followed by a thermal cycle (to drive the impurity from the Si surface into the bulk) C. Ion implantation: subject the Si substrate to highly energized donor or acceptor atoms. The injected impurities will travel below the surface of the Si, forming regions with varying doping concentration. D. Diffusion: At temp. > 800ºc, Impurities will diffuse from areas of high concentration to area of low concentration. =>It's important once the doped areas have been put in place, to keep the remaining process steps at as low a temperature as possible. 2 ● Impurities: Boron: Acceptors Arsenic, phosphorous: Donors ● Amount is controlled by 1. Energy and time of “Ion implantation”. 2. Time and temperature of “deposition” and “diffusion”. ● Mask: Implantation Occurs/Not occurs Deposition A. Common materials used as masks include: 1. Photoresist 2. Polysilicon (polycrystalline silicon) 3. Silicon dioxide (SiO2) 4. Silicon Nitride (Si3N4) B. Function: Form a barrier against doping impurities (selective diffusion). Steps: 1. Patterning "windows" in a mask material on the surface of the wafer. 2. Subjecting exposed areas to a dopant source. 3. Remove any undesired mask materials. SiO2 is removed using an Etching Technique. A. Use an acid resistant coating (photoresist) (PR) which can be polymerized by ultraviolet (UV) light. B. The polymerized areas may be removed with an organic solvent. C. Etching of exposed SiO2 then may proceed. D. Steps of A-B-C is called “Positive resist" E. "Negative resist" = Unexposed PR is dissolved by the solvent. Diffraction around the edges of the mask patterns and alignment tolerances limit line widths to around 0.8 um. Alternative approaches: A. Electron Beam Lithography (EBL): High cost but very precise. Advantage: - Patterns are derived directly from digital data. - No intermediate hardware images such at recticles or masks; that is, the process can be direct. - Different patterns may be accommodated in different sections of the wafer without difficulty. - Changes of patterns can be implemented quickly. 3 B. DSP Approach (Numerical Technologies Inc. founded by Stanford people). - Use de-convolution techniques to solve the diffraction problem. Change Mask shapes so that desired etching patterns can be shown on wafer. 4 3.1.4 Silicon Gate Process Si Single-crystal form Poly crystalline form (Polysilicon) Polysilicon is used as interconnect wires in silicon IC's and as the gate electrode on MOS transistors => Can be used as the "mask" for MOS Drain and Source (Self-aligned process) Polysilicon is formed when silicon is deposited on SiO2 or other surfaces. For example, in CMOS, undoped polysilicon is deposited on the gate insulator. 5 Function of SiO2 1. 2. 3. 4. Gate-oxide (thinox) Field-oxide (thick) Self-aligned process (source & drain donor extend over the gate) "Field device" or "Parasitic MOS transistors" 6 3.2 CMOS Process Technology 1. n-well process 2. p-well process 3. Twin-tub process 4. Silicon-on-insulator (SOI) 3.2.1 Basic n-well CMOS process 1. Start with a lightly doped p-type substrate (wafer) 2. Create the n-type well for the p-channel device. 3. Build the n-channel transistor in the "native" p-substrate (watch Fig.3.6 & Fig.3.7) 4. CMOS process and layout drawing conventions 7 (a) Define n-well (n-tub) - n-well for PMOS - n-well-shallow is better - Well is extended by lateral diffusion (b) Define Active Region - Grow SiO2/Si3N4 (c) Channel-stop Implant: - Use p-well Mask - Dope the p-sub with p+ in areas where no NMOS using photoresisit - Prevent conduction between unrelated transistor source/drain - Strip Photoresist - Grow thick field oxide where Si3N4 layer is absent - (LOCOS) (Bird’s break): Final field oxide and Gate Oxide interface is very planar --> smaller L (e) Define Polysilicon gate - Lead to “Self-aligned” Source/Drain Region 8 (f) Define NMOS - Use N+ mask - Poly is doped (g) Light-Doped Drain (LDD) (h) P+ mask - (LDD is not required), - Less Hot-carrier susceptibility. (i) - Grow SiO2 - Define contact cut: Etch SiO2 down to surface to be conducted. (j) Metallization: Add metal to produce circuit connectivity 9 ● Substrate contact (well contacts, body ties, tub ties) 1. Place n+ region in the n-well (VDD contacts) 2. Place p+ region in the p-type substrate (Vss contacts) 10 ● p-well process 1. 2. 3. 4. n-well process is more popular in recent years (p-well process is popular in the past) n-well <-> p-well in process The device in the substrate has better characteristics - p-well process has better p devices than the n devices - note p-devices have lower gain than the n devices - n-well process exacerbates the difference <-> p-well process can balance the diffusion ● Twin-tub CMOS process 1. Provide separate optimization of the n-type and p-type transistors 2. Make it possible to optimize "Vt", "body effect", and the "gain" of n, p devices independently. 3. Steps: A. Starting material: an n+ or p+ substrate with lightly doped -> "epitaxial" or "epi" layer -> to protect "latch up" B. Epitaxy" a. Grow high-purity silicon layers of controlled thickness b. With accurately determined dopant concentrations c. Electrical properties are determined by the dopant and its concentration in Si C. Process sequence a. Tub formation b. Thin-Oxide construction c. Source & drain implantations d. Contact cut definition e. Metallization ● Balanced performance of n and p devices can be constructed. 11 (Substrate contacts are included in Fig.3.10) 12