Introduction to Xilinx Lab

advertisement

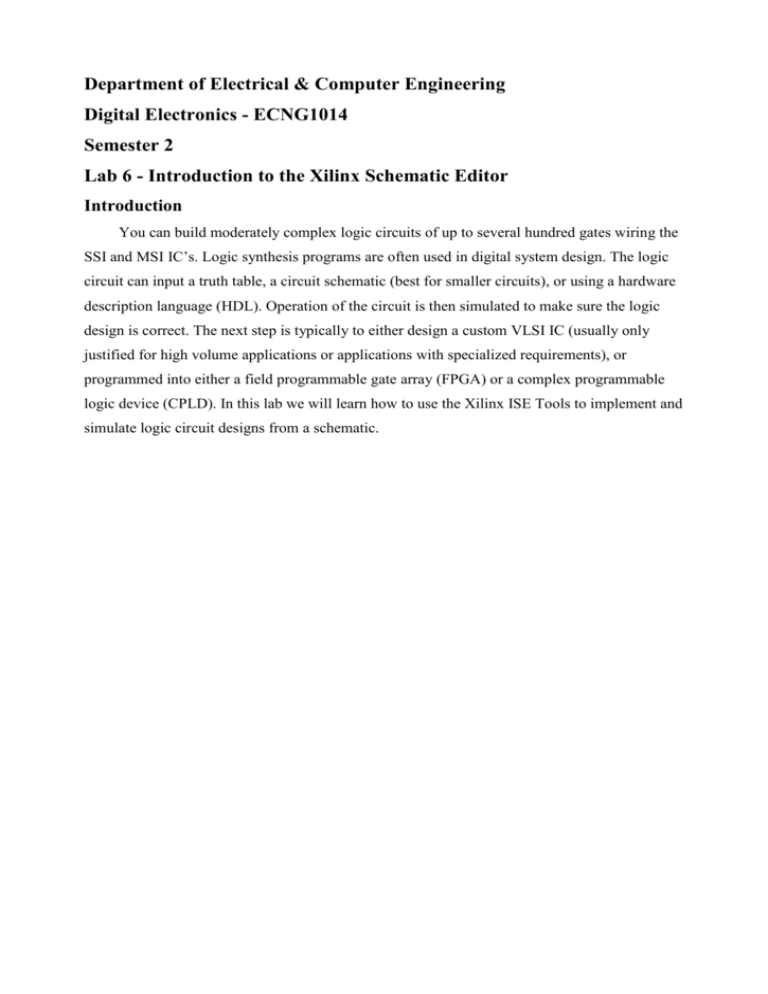

Department of Electrical & Computer Engineering Digital Electronics - ECNG1014 Semester 2 Lab 6 - Introduction to the Xilinx Schematic Editor Introduction You can build moderately complex logic circuits of up to several hundred gates wiring the SSI and MSI IC’s. Logic synthesis programs are often used in digital system design. The logic circuit can input a truth table, a circuit schematic (best for smaller circuits), or using a hardware description language (HDL). Operation of the circuit is then simulated to make sure the logic design is correct. The next step is typically to either design a custom VLSI IC (usually only justified for high volume applications or applications with specialized requirements), or programmed into either a field programmable gate array (FPGA) or a complex programmable logic device (CPLD). In this lab we will learn how to use the Xilinx ISE Tools to implement and simulate logic circuit designs from a schematic. Objectives This laboratory exercise provides students with a comprehensive introduction to digital system design and implementation using the Xilinx Schematic Editor. At the end of this exercise students will be able to: Create a new project in Xilinx ISE Understand the basics of Xilinx Schematic Editor - Selection of macros for the creation of schematics - Search for macros using the ‘symbol name filter’ feature - Create a schematic using macros selected - Add wires to the schematic to interface macros - Add I/O markers to the design - Observe the internal structure of macros available from the Xilinx symbol library. - Obtain the datasheets for macros used in the editor using the ‘symbol info’ feature. Create macros using the editor Create a 1-bit adder macro and use it to create a 4-bit adder macro. Synthesis a digital system implemented in Xilinx ISE View the RTL Schematic of the system implemented. Perform both functional simulation(Simulate Behavioural Model) and timing simulation(Simulate Post-Translate VHDL Model) for a digital system using Modelsim 6.0SE/XE. Create an implementation Constraints file for the design and assign package pins and downloading the implementation onto the FPGA development board. 1. Creating a New Project A project in ISE is a collection of all files necessary to create and download a design to the selected device. To create a new project: 1. Select File New Project. 2. In the New Project Wizard dialog box, enter the project name ‘My_4bit_Adder_’ in the diagram below. You can browse to the desired directory using the browse button next to the Project Location field. Now Click Next. 3. In the New Project Wizard Device and Design Flow dialog box, use the pull-down arrow to select the Value for each Property Name. Click in the field to access the pull down list. Change the values as follows: Device Family: Spartan2 Device: xc3s400/xc3s1000 Package: pq256 Speed Grade: -5 Synthesis Tool: XST (VHDL/Verilog) Simulator: Modelsim Generated Simulation Language: VHDL Click Next 5. This will open a New Project dialog box. Click on ‘New Source’ to create a new source to be added to the project. Click Next! Then click Next again! Then click Finish. 6. In the New Source dialog box select Schematic from the list. Name the file as MyFullAdder in the File Name field. Verify that the Add to project check box is selected. Click Next. Then click Finish! This will launch Engineering Capture System (ECS). You may have to choose the tab labeled MyFullAdder and close other windows in the left side (don’t close the Sources window). A blank sheet opens in an ECS schematic window. In ECS, you can create a schematic diagram from scratch. 2. Creating a Schematic On the left side of the screen you will see two small windows, Categories & Filter. This is where we will find all the components we will need to assemble our full adder. 1. Select Logic in the Categories window. What this does is to only display logic gates in the Symbols window. From the Filter window select a NAND2 and drop three of these gates onto your workspace. Also grab two XOR2 gates. 2. Click on the Add Wire icon . This will allow you to connect the components together. Click on the lead of one gate then on the lead of the next and a wire will be drawn that connects the two together. Note that S=A⊕B⊕C Cout = (A ⊕ B) C + AB After the wires have been connected your circuit should look at follow. Make sure to add wires to outputs S and Cout. Now we need to add I/O Markers. These markers will help Xilinx determine where the inputs/outputs are when it converts this schematic into a macro. 3. Click the I/O Marker icon . Place markers on each input and output by clicking on the terminal that you wish to place the marker. Your schematic should look like this with the markers in place. Xilinx automatically assigns names to the markers, but remembering the names can get confusing really fast. 4. For clarity, change the names. Right click on the marker and rename. Alternatively, you can select the pointer tool and double click on the marker you wish to rename. In the Object properties dialog box change the name of the marker by changing the name in the Value field. Click Ok! Similarly rename all your markers. When you are done the schematic will appear as follow. 3. Creating a Macro Now that our schematic is complete we would like to create a macro. A macro is user created symbol that can be used just like a component. The advantage of creating a macro is that once you have a macro for your full adder you can use the same macro over and over again. First, save your schematic! Then from the tool bar select Tools > Symbol Wizard. Select Using Schematic. Click Next! A dialog box with the input and output ports of the schematic open up. Check whether the input and output ports are defined as you intended. Click Next! In this dialog box you can change some appearance properties of the symbol being created. In this dialog box you can change some appearance properties of the symbol being created. Click Next! You can see your symbol on a symbol wizard dialog box. Click Finish! Now close the Symbol editor. Close the schematic we had just been working on, and return to the project navigator. In the Project Navigator, on the left we can see, under the device, is a symbol has been created representing the schematic you just finished working on. Now lets create a new Schematic. 1.Right click on the Device -> New Source… Select Schematic from the list and name it My_4bit_Adder_Chip. Next! Finish! This will reopen the schematic editor (ECS). Now select the symbols tab and look in the Categories Window, a new category has been added. <E:/…./My_4bit_Adder> In this category you can also find your full adder. You have just completed creating your first macro! Mini-Exercise for section 3 Use the full adder macro created previously to create a 4-bit adder. You can select copies of this adder from the new category create and connect them together as shown in the diagram below to create the 4-bit adder. The result must look like the 4-bit adder macro shown in the next diagram. 4. Synthesizing & Implementation of the design Synthesize the design by double clicking on the ‘Synthesize - XST’ section of the Process View window as shown in the diagram below. Implement the system by double clicking on the ‘Implement Design’ section of the Process View window as shown in the diagram below. 5. Obtaining the RTL Schematic for the system Obtain the RTL Schematic for the system by double clicking on the ‘View RTL Schematic’ section of the Process View window as shown in the diagram below. 6. Simulation of the design using Modelsim 6.0SE/XE In the New Source dialog box select Test Bench Waveform from the list. Name the file as My_4bit_Adder_tb in the File Name field. Verify that the Add to project check box is selected. Click Next! Attach the test bench waveform file to the top level schematic module ‘My_Adder_test’ and click Next! Then click Finish! Set the test bench waveform with the following test cases as shown in the table below. A3 0 0 0 1 A2 0 1 0 0 A1 1 0 0 0 A0 1 0 1 0 B3 0 0 0 1 B2 0 0 0 0 B1 0 1 0 0 Table 1: Test cases for simulation B0 1 0 0 0 Cin 0 0 1 0 Now save the design, highlight the test bench waveform in the Module View window, then double click ‘Simulate Behavioral Model’ from the process window. The Modelsim 6.0SE/XE GUI loads automatically. Verify that the system is functional by thoroughly analyzing the timing diagram generated in the Modelsim window. Repeat the simulation using ‘Simulate Post-Translate VHDL Model’. 7. Programming the FPGA development board The first step to programming the FPGA development board is to create the implementation constraints file. This is done by selecting Implementation Constraints File from the New Project dialog window. The file must then be given the name My_4bit_Adder_ucf. We then click Next. Ensure that the implementation constraint file created is connected to the top level schematic ‘My_Adder_test’ as shown in diagram below. Then click Next. Then click Finish. We then double click the Implementation Constraints File from the Module View and then assign package pins using the table below. Design Port FPGA Pin Assigned A3 A2 A1 A0 B3 B2 B1 B0 Cin S3 S2 S1 S0 Cout K13 K14 J13 J14 H13 H14 G12 F12 M13 N14 L12 P14 K12 P11 Table 2: Pin assignments for the Implementation After assigning package pins, save the changes made and double click ‘Configure Device iMPACT’ under the Generate Programming File tab from the Process Window as shown in the diagram below. Click Next! Click Finish! Click OK! Click Open! You are now prompted for a PROM programming file as shown in the figure below. We are not programming the PROM at this time, therefore select Bypass. Finally, you will reach the point shown in Figure 1.31. iMPACT is ready to program the FPGA. Select the FPGA icon in the window and then use the right mouse button to activate the menu as shown and select the Program option.