Supplementary information_revised

advertisement

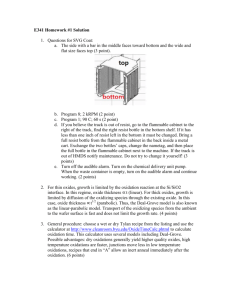

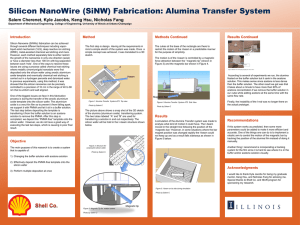

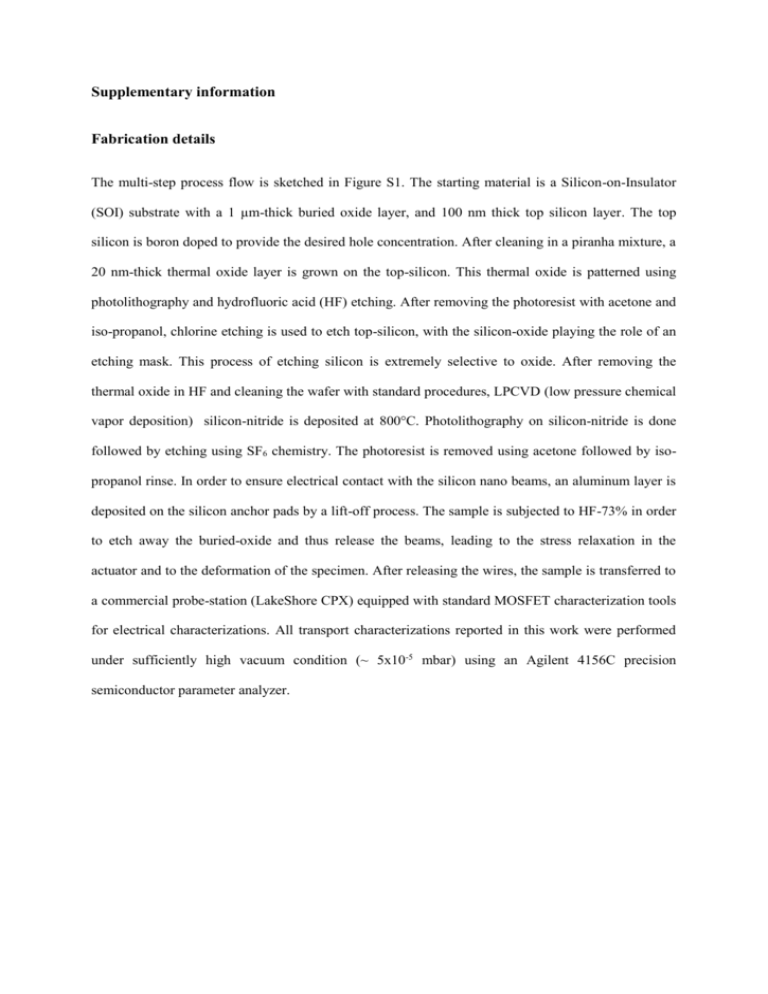

Supplementary information Fabrication details The multi-step process flow is sketched in Figure S1. The starting material is a Silicon-on-Insulator (SOI) substrate with a 1 µm-thick buried oxide layer, and 100 nm thick top silicon layer. The top silicon is boron doped to provide the desired hole concentration. After cleaning in a piranha mixture, a 20 nm-thick thermal oxide layer is grown on the top-silicon. This thermal oxide is patterned using photolithography and hydrofluoric acid (HF) etching. After removing the photoresist with acetone and iso-propanol, chlorine etching is used to etch top-silicon, with the silicon-oxide playing the role of an etching mask. This process of etching silicon is extremely selective to oxide. After removing the thermal oxide in HF and cleaning the wafer with standard procedures, LPCVD (low pressure chemical vapor deposition) silicon-nitride is deposited at 800°C. Photolithography on silicon-nitride is done followed by etching using SF6 chemistry. The photoresist is removed using acetone followed by isopropanol rinse. In order to ensure electrical contact with the silicon nano beams, an aluminum layer is deposited on the silicon anchor pads by a lift-off process. The sample is subjected to HF-73% in order to etch away the buried-oxide and thus release the beams, leading to the stress relaxation in the actuator and to the deformation of the specimen. After releasing the wires, the sample is transferred to a commercial probe-station (LakeShore CPX) equipped with standard MOSFET characterization tools for electrical characterizations. All transport characterizations reported in this work were performed under sufficiently high vacuum condition (~ 5x10-5 mbar) using an Agilent 4156C precision semiconductor parameter analyzer. Figure S1 Schematic illustration of the fabrication of elementary tensile test structures with on-chip application of the loading through the release of the internal stress present in a silicon nitride “actuator” beam. Figure S2 Optical microscopy image of two mutually opposite array designed to minimize dispersions from process variations to be mis-interpreted as piezo-resistance. Figure S3 The output characteristics for (a) FW array and (b) REV array for Na ~ 1 × 1019 cm-3.