Foundry Design Kit

advertisement

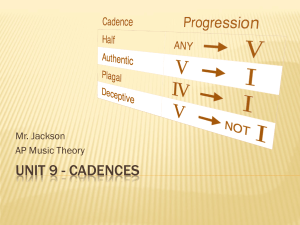

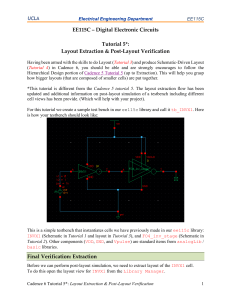

Process design environment a sub-project under the parent Angstrem-T project Content and structure of the Process Design Kit • Design rules and specification Process Design Kit (PDK) process •Process files • Device models • Device library • Skill (Pcell skill code) • Physical verification Process design environment • Combinational logic Standard Cell Libraries (SC) • Trigger logic • Special cells • Clock cells • Delays • Signal IO Cell Libraries (IO) • Analog • Oscillator • Power cells • Earth cells • Special cells • SRAM, single-port Memory Compilers (МЕМ) • SRAM, dual-port • Register files (1 and 2 ports) • ROM • САМ 2 Standard Cell Libraries (SC) Long experience – it has more than a dozen standard cell libraries developed for foreign and domestic semiconductor manufacturers. Cell layout Design flow – it is based on the usage of Cadence licensed software and ensures the library development within a short period of time. • Circuit and layout design (Cadence Virtuoso®); • Extraction of cell schemes from layout with RC-parameters (Cadence Assura); • Characterization of library cells (Cadence Encounter® Library Characterizer); • Creation of library views (doc, gds, cdl, lib, verilog, vhdl, etc.). Inverter Cell composition – it is defined on the basis of analysis of the standard cell libraries of world leaders in ASIC-libraries development and consultations of leading domestic design centers, it has more than 500 elements including: • Combinational logic: Inverter, Buffer, AND, OR, XOR, AND-OR-Inverter, OR-AND-Inverter, Multiplexer, Half Adder, Full Adder, Compressor; • Trigger elements: Transparent Latch, D Flip-Flop (scan, enable), JK Flip-Flop, RS latch; • Special elements: Delay cells, Clock Gating cells, Tie off cell (logic 1 or 0), Bus Holder cells, Fillers cells, Filler Cap cells, Antenna Cell. 2AND-NOT Front Set-Reset Flip-Flop 3 IO Cell Libraries (IO) Purpose – input-output pad libraries have a full set of elements to digital and analog interface design of the chip with 3.3 V and 2.5 V supply voltage. Input/output element layout Design flow – it is based on the usage of Cadence licensed software and ensures the library development within a short period of time. • Circuit and layout design (Cadence Virtuoso®); • Extraction of cell schemes from layout with RC-parameters (Cadence Assura); • Characterization of library cells (Cadence Encounter® Library Characterizer); • Creation of library views (doc, gds, cdl, lib, verilog, vhdl, etc.). Features: • Optimization with consideration of the requirements to noise level for power and earth buses • Imbedded ESD protection circuits (4kV level) • Programmable values of output power (8 levels in 2mA – 24mA range) • Programmable values of output front time • Programmable values of the input signal switching threshold (CMOS/TTL) • Hysteresis • Current shifting to power and earth buses Power pad (P60VIO_D) Output pad (P60O33_D1) 4 Memory Compilers Design flow – a library approach to the creation of compiler database has been realized, including: - database structure development; - in-house design procedure for library cells; - development of design rules for library cells; - in-house internal format for compilation algorithm description. Memory block architecture – an original mechanism of frequency control has been realized which ensures the exact correspondence between design and actual parameters of compiled memory blocks. A patent for memory block architecture with a system of reading speed automatic adjustment has been received. SRAM architecture Patents Characterization – a unique in-house characterization system for compiler cell library has been developed, including: - block library preparation procedure; - mathematical technique; - an in-house CAD software kit. 5 User Library Views A wide range of views of the standard cell library ensures a Advanced CAD simple and easy project design procedure with the use of advanced computer-aided design tools. Library views: • Cell library catalogue (PDF) • Schematic circuit diagram (CDL-netlist) • Symbolic representation of cells (Symbol) • Layer-by-layer description of cell layout (GDSII) • Physical model of cell layout (LEF) • Library characterization in Liberty format • Library characterization in TLF format • SYNOPSYS system database (Milkyway) • Behavioural description of cells in Verilog language • Behavioural description of cells in VHDL language 6