PowerPoint

advertisement

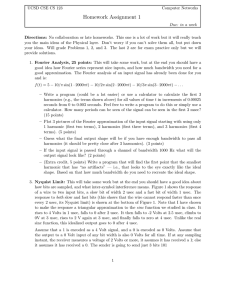

Checkpoint 3 • To Do • Hints • General Debugging To Do: Before Lab • Plan layout of chips • Wire sync separator, A/D, op amp and RC network • Enter and simulate FSM to store one video frame in SRAM (either 196x210 or 14x10) Video Signal Video Signal • Begin frame: “Wait 17 horizontal periods after vertical sync. goes low.” – VBLANK.H = active high VERT_SYNC • Begin row: “Wait 9.5 usec after composite sync. goes low” – 9.5 usec = 4.7 usec + 4.8 usec • Ex: 52.4 usec / 14 = sample every 3.75 usec • Ex: 241 lines / 10 = sample every 24 lines From wvlib\cs150\check3.sch Two Cycle Write • 52.4 usec / 196 = 0.27 usec • 10 MHz CLK = 0.1 usec per cycle • Only have 1/2 cycle for stable ADDR OFD_1 WE D Q WE_OUT OPAD LOC=P14 CLK OE, UART_OE, AD_OE • Now have three registers on D bus • Add separate UART_OE. Change: Old lab9pinout.sch Change lab9pinout.sch: OE, UART_OE, AD_OE, cont. • Add OFD to OE (if you haven’t already) • Add AD_OE (already in check3.sch): Processing A/D data • While reading A/D: send directly to SRAM • During PWM: shift from 8 bit to 5 bit • Also, adjust to min/max A/D values To Do: In Lab • Test camera on television • Look at video signal on oscilloscope • Test bit file u:wvlib\cs150\check3.bit To Do: Check Your Circuit • View comp. sync. and WE – should see 14 or 196 WE per comp.sync. • View vert. sync., WE and ROW_INC – should see WE pulse block between syncs. – should see 10 or 210 ROW_INC per vert sync. To Do: Checkoffs • Valid comp. and vert. sync. from LM1881 • Show A/D CLK and D[7:0] and SRAM WE on oscilloscope Hints • Save CLBs: remove LED_BLOCK, ROM • Modularize each FSM: reset, enable, done: UART_RESET RESET UART_ENABLE ENABLE DONE DATA[7:0] UART_DONE UARTDATA[7:0] FDRE CLK SERIAL_CLEAN CLK SERIAL_CLEAN NS0 ENABLE RESET D CE Q R CLK PS0 General Debugging • Get simplest part working: • Example: checkpoint 2 – Light up all LEDs on row 3 – Light up all LEDs with intensity 16 – receive one byte from PTEST.EXE (^A = 0x01) and light up all LEDs General Debugging • Implementation log: – “No load on xxx” is OK – “No driver on xxx” not OK • “I can’t find the part giving the error!”: – 1. Make a copy of schematics – 2. Rip out sections and re-implement until error goes away – 3. Add sections back in: ISOLATE. General Debugging • Don’t assume equipment works: – “This pin is always zero”: Does the oscilloscope even work? Try touching +5V – “My RS232 Rout has no output”: Does it have an input? Is anything coming down the serial cable? (Test just the serial cable (after testing your scope probe on +5V (after testing that your power supply puts out +5V))) General Debugging • Make the simulation work first • Use NUMLED1 to watch counters • Make a new counter and watch on NUMLED1 • Use the oscilloscope! – Send signals to ERROR, NUMLED1 pins – Use “single” trigger to catch event General Debugging • Make sure you read about Xilinx part before you use it. (Ex: CD8RE) • Read the newsgroup – (If you don’t know how, you’re an engineer: Find out) • SIMPLIFY and ISOLATE