Pedreschi - Indico

advertisement

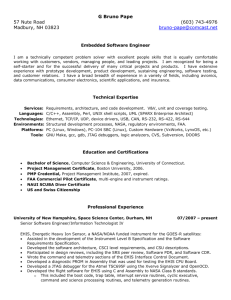

TEL62 status and plans Elena Pedreschi INFN-Pisa Thursday 08 September 2011 TDAQ WG Meeting at Mainz University TEL62 TEL 62 (v0) DDR2 DC (TDCB) Glue Card CCPC PP TTCRx QDR SL AUX Gigabit TEL62 TEL 62 (v0): DDR2, CCPC, Glue Card, Gigabit plugged TEL62 TEL 62 (v0): DC (TDCB), DDR2, CCPC, Glue Card, Gigabit plugged Lab SETUP Pisa Lab Crate SETUP Power Power requirements: 320mA@48V when PPs and SL programmed with simple firmware (DDR2 Controller included) -5V 3.3V 48V 5V JTAG & Programming (1) Small issue on IC 74LVC16244A (jtag tck driver) -> couple of “blue” wires Small issue with JTAG chain; 33 Ohm termination resistors removed from TCK and TMS driver JTAG & Programming (2) The chain is correctly recognized both using Altera USBblaster and CCPC jtag port(s). EPCS64, no-jtag, SFL on PP,SL SL PPs QDR GBIT TTCRx Pps correctly programmed through a single EPCS64 TDCB JTAG & Programming (3) EPCS programming through active serial -> OK EPCS programming through JTAG (jic file, using Quartus programmer proprietary method) -> OK Altera supports a non-proprietary programming of EPCS through JTAG using jam files. Programming with jam file through Windows Jam player -> OK CCPC software from LHCb includes a Jam player, but at the moment the same jam file does not work (neither on TELL1). Needs some work on the software side … Performed tests TTCRX -> OK (clock, LV1 recovered from fiber, commands received) Interface plug-in (TDCB) <-> TEL62: Power , JTAG , clock -> OK QPLL locks (both external clock and TTCRX clocks) “Potato” clock drivers -> OK RGB led on front panel -> OK CCPC: power-on -> OK Linux boot -> OK Connection to GLUE card, tested JTAG ports and I2C devices -> OK Test ECS connections to all the chips -> OK Tests in progress (1) DDR2: the controller is already in the PP firmware, but needs to be optimized toward the PCB’s delays, simulated and then deeply tested (quite a big work …) QDR: controller, optimization of the clock -> in progress PPs <-> SL: Data lines (120 MHz)-> in progress Interface plug-in (TDCB) <-> TEL62: Data lines -> in progress Tests in progress (2) Gbit: the firmware in the current TELL1 SL can be used but needs to be imported in the TEL62 framework and then tested Final Crate: test on final Crate to be performed in October in Frascati, using an ad-hoc firmware for power consumption measurements Firmware (1) Framework: HDL Designer (Mentor Graphics ): Powerful HDL design environment (manages complex FPGA designs in VHDL) Extensive design checking rules and rulesets Intelligent debug and analysis (board simulation) Development skeletons and common libraries already available Quartus II Design Software (Altera) Needed for VHDL development SignalTap II Logic Analyzer Allows to examine the behavior of internal signals Does not require extra I/O pins The design is running at full speed on an FPGA device while analyzing Firmware (2) HDL Designer environment: Project TEL62 Firmware (3) Repository: HDL Designer integrated CVS/SVN Preferred method Remote repository support to be verified Repository should be hosted at CERN CVS/SVN standalone zip files Details in “TEL62 firmware live kick-off meeting” … Planning (1) Components: Before the end of the year many of the critical components will be bought MT16HTF25664HZ-800H1 (Micron DDR2 2Gb 256Mx64) K7Q161852AFC13 (Samsung QDR Memory) -> DONE EP3SL110F1152C4N (Altera FPGA Stratix III) QHS55-012-NHCRC, ALD20G48N-L, QHS50-018-NHBRC (DC/DC converters) Pre-production: November: DEM @CERN will work on new TEL 62 pcb (up to now only simple modification are required) December: 10 TEL 62 printed circuit board will be in production One board will be mounted and tested (one week) Planning (2) January: Nine board will be mounted TEL 62 estimated price : ~3000-3500 € Dry Run at CERN: Time slot: 15 June /15 July 2012 (suggested) Functionalities: Basic firmware but sufficient to handle the dataflow and trigger No board to board comunications Test run at CERN: Time slot: September/October 2012 Planning (3) Final Production: Time slot: Autumn/Winter 2012 Productions acceptance tests: could be performed directly by the assembling company, if we provide the necessary hardware and software tools: Requirements: Vectors for Boundary Scan needs to be generated Jtag interface and software To test the plug-ins connections we will need: 4 TDCB (no special firmware is required) simple dummy boards to be plugged in DDR2 and AUX connectors CONCLUSIONS The TEL62 V0 is under test … No big issues up to now … Many important tests are in progress V1 will come at the end of year The TEL62 firmware: Framework chosen and firmware structure under development A lot of firmware has to be written We will have today a dedicated meeting Some critical components will be bought asap Pre-production before Dry Run (June 2012)