Chap1 - ECE Users Pages

advertisement

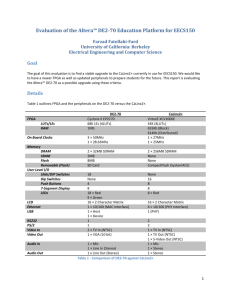

Figure 1.1 The Altera UP 3 FPGA Development board Figure 1.2 The Altera UP 2 FPGA development board. Figure 1.3 Design process for schematic or HDL entry. +5V +5V +5V PB1 PB2 Altera Flex Device LED Figure 1.4 Connections between the pushbuttons, the LEDs, and the Altera FPGA. (a) (b) Figure 1.5a and 1.5b. Equivalent circuits for ORing active low inputs and outputs. Figure 1.6 Creating a new Quartus II Project. Figure 1.7 Setting the FPGA Device Type. Figure 1.8 Creating the top-level project schematic design file. Figure 1.9 Selecting a new symbol with the Symbol Tool. Figure 1.10 Active low OR-gate schematic example with I/O pins connected. Table 1.1 Hardwired connections on the FPGA chips for the design. I/O Device UP 3 Pin Number Connections UP 1 & UP 2 Pin Number Connections PB1 62 (SW7) 28 (FLEX PB1) PB2 48 (SW4) 29 (FLEX PB2) LED 56 (D3) 14 (7Seg LED DEC. PT.) Figure 1.11 Assigning Pins with the Assignment Editor. Figure 1.12 Active low OR-gate timing simulation with time delays. VGA Par allel Por t Moun ti ng Port PS-2 Ho le J3 Port I2C PR OM C hip ..... H eat Sink U SB Port B B San ta C ruz Expan sion L ong C onn ector JP1 9 B Hea ders for I2C Bus Sign als USB PHY Ch ip B “B”- Buffe r C hip s J2 Seria l Ch ip B J4 San ta C ruz Expan sion L ong C onn ector Cyclone FPGA EP1C6Q240C8 Rea l Time C lock Inva lid Vol t. LED S W4 LED JTAG & AS Download Connector s 4 User Definable LEDs S W5 D5 D4 Reset D3 JP3 B 4 Use r D efina ble D IP Swi tch es (JP3) Global Reset Liquid Cr ystal Display LED On/Off Switch JP5 Oscil lator Ch ip SRAM S W7 D6 San ta C ruz Expan sion L ong C onn ector JP19 Flash S W6 J1 JP4 4 Push Buttons In put Clo ck JP7 Setti ng He ade rs J5 JP6 Heat Sink J7 Heat Sink +3.3 Volt Supply +5 Volt Supply LED LED Power Connector Pushbuttons Figure 1.13 ALTERA UP 3 board showing Pushbutton and LED locations used in design Chip Select Jumpers Decimal Point LED Mouse VGA Adapter DC_IN FLEX_DIGIT TCK POWER 25.175 MHz CLOCK FLEX_EXPAN_C FLEX_10K P1 EPC P2 R R P7 R R U1 P8 D1 D9 D13 D5 EMP7128SLC84-7 BFD329 837 D10 D2 D14 D6 D11 D3 D12 D4 P3 D8 P5 P6 D15 D7 P4 P9 EPF10K20RC240-4 DAA23 9837 D16 P10 FLEX_EXPAN_A FLEX_PB1 MAX_SW1 FLEX_PB2 MAX_SW2 JTAG_OUT FLEX Pushbuttons Figure 1.14 ALTERA UP 2 board with jumper settings and PB1, PB2, and LED locations Table 1.2 Jumper settings for downloading to the UP2 MAX and FLEX devices. MAX FLEX Pin 14 Figure 1.15 UP 2’s FLEX FPGA pin connection to sevensegment display decimal point. Figure 1.16 VHDL Entity declaration text. Figure 1.17 VHDL OR-gate model (with syntax error). Figure 1.18 VHDL compilation with a syntax error. Figure 1.19 Verilog module declaration text. Figure 1.20 Verilog active low OR-gate model (with syntax error). Figure 1.21 Verilog compilation with a syntax error. Figure 1.22 Timing analyzer showing input to output timing delays. Figure 1.23 Floorplan view showing internal FPGA placement of OR-gate in LE and I/O pins orgate PB1 LED PB2 inst Figure 1.24 ORgate design symbol. Figure 1.14 The Altera DE2 FPGA Development board 9V DC Power Supply Connector USB Blaster Port USB Device Mic In USB Host Mic Out Line In 24-bit Audio CO DEC Power ON/ OFF Switch XSGA Video Port Video In Et hernet 10/100M Port RS-232 Port 27Mhz Oscillator XSGA 10-bit DAC USB Host/Slave Controller Ethernet 10/100M Controller TV Decoder (NTSC/PAL) Altera EPCS 16 Configuration Device Altera USB Blaster Controller Chipset 50Mhz Oscillat or RUN/ PROG Switch for JTAG/AS Modes 90nm Cyclone II FPGA with 35K LEs LCD 16x2 Module 8MB SDRAM 7-SEG Display Module 88 88 512KB SRAM SD Card Connector 1MB Flash Memory (upgradable to 4MB) 8888 18 Red LEDs 8 Green LEDs IrDA Transceiver SMA Ext Clk 18 Toggle Switches 4 Push-button Switches Figure 1.15 The Altera DE2 FPGA Development board