Memory Sharing Processors - High Speed Digital Systems Laboratory

advertisement

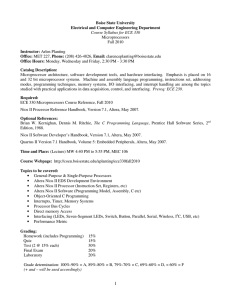

Technion – Israel Institute of Technology Department of Electrical Engineering High Speed Digital Systems Lab ® Spring 2009 Overview Any system which incorporates two or more microprocessors who work together is called a multiprocessor system A multi-core processor combines two or more independent cores in a single integrated circuit Nios II is an embedded processor implemented on Altera FPGA boards Several Nios II cores can be joined together on the FPGA board, thus creating a multi-core environment Project Goals Implementing different types of multi-core systems, each dealing with different aspects of multiprocessors Executing C/C++ programs on the different systems and comparing the benefits and disadvantages of each one Checking different aspects of multi-task programs and their compatibility on the multicore system Creating the basis for future lab experiments of multi-core SOPC Platform Altera DE2, the board used in the project, a development board built on a Cyclone II EP2C35 FPGA Includes memory peripherals as an 8-Mbytes SDRAM, 4Mbyte flash and 512Kbyte SRAM Includes an LCD, eight 7-segment displays, different LEDs, switches and buttons In addition includes several I/O device connections Design Tools Quartus II 8.0 software used for analysis and synthesis of the whole board design and I/O integration SOPC Builder used for creating the complete system infrastructure containing the Nios II processors, data memory and other IP components Nios II IDE used for executing and debugging C/C++ programs on the Nios II embedded processor Multiprocessor Systems A multiprocessor system benefits from increased performance, but at the expense of significant system complexity Until recent years such systems were only used on servers and high-end computers, using a complex load-sharing method (SMP) Altera FPGAs are a good platform for developing asymmetrical embedded multi-core systems Using the SOPC builder tool different kinds of multi-core systems can be easily built, examined and afterwards tested with the IDE Different Implementations Multiprocessor systems split into 2 main categories, those who share resources and those who don’t Autonomous processors do not share resources and do not communicate with each other and so are easy to implement Memory sharing processors share some resources between them, but creating such a system poses many challenges and isn’t straightforward A mixed system can also be built, a one in which some processors are autonomous and some share resources Autonomous processors Autonomous multiprocessors systems contain multiple processors, but behave as though they are in separate systems The processors do not interfere with each other and do not share addresses The good: When several tasks need to execute in real-time, giving each task its own core and resources lets it run undisturbed The bad: Resource utilization may not be optimized and cannot be shared with other tasks Memory Sharing Processors System resources are considered shared when they are available to be accessed by more than one processor The good: Shared resources is a very powerful aspect in a multiprocessor system since it maximizes resource utilization The bad: Although physically connecting several processors to a resource is easy, managing the resource correct operation and processors’ cooperation is hard Responsibility for this positive cooperation lays on the system programmer Memory Sharing Processors continued The most common type of shared resource in multiprocessor systems is the memory If the memory is shared for instruction purposes each processor must have its separate area for code execution When using the memory for data purposes, the problem is more complex since each processor can read and write to the same address simultaneously, thus creating data corruption or a system crash The memory can be shared symmetrically, or asymmetrically when some processors share one memory but others have their own private one The Mutex Core Nios II processor provides protection of shared resources using a hardware mutex The mutex core is itself a shared resource, providing atomic test-and-set operation Using the mutex each processor can lock a specific resource and release it when done using, giving an other processor access The software using the processors is responsible for using the mutex, since the mutex itself does not physically protect resources Mailbox The Mailbox is another core peripheral assisting in shared memory management The mailbox contains two mutexes, one for unique write and one for unique read Access to the mailbox is FIFO, meaning only one processor can read or write to the mailbox Processors can post and read messages in the mailbox, when the read operation can be blocking Processors must agree on a protocol for interpreting the messages Timeline Going over Altera’s SOPC tutorial course - done Building a single Nios II processor infrastructure and running a sample C program on it – done Implementing and testing an autonomous multiprocessor system – Until the midterm presentation, ~3 weeks Midterm presentation – End of May Implementing a shared memory multiprocessor system using different architectures and designs – After the midterm, ~4 weeks Executing multi-thread software on the system and comparing the benefits and disadvantages of it– ~2 weeks Documentation, project report and final presentation – ~Mid July