Chapter_5

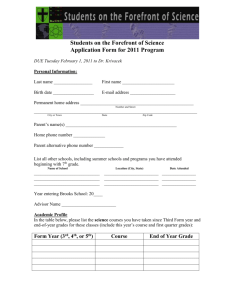

advertisement

Chapter 5 Computer Organization ©Brooks/Cole, 2003 OBJECTIVES After reading this chapter, the reader should be able to: Distinguish between the three components of a computer hardware. List the functionality of each component. Understand memory addressing and calculate the number of bytes for a specified purpose. Distinguish between different types of memories. Understand how each input/output device works. Continued on the next slide ©Brooks/Cole, 2003 OBJECTIVES (continued) Understand the systems used to connect different components together. Understand the addressing system for input/output devices. Understand the program execution and machine cycles. Distinguish between programmed I/O, interrupt-driven I/O and direct memory access (DMA). Understand the two major architectures used to define the instruction sets of a computer: CISC and RISC. ©Brooks/Cole, 2003 Figure 5-1 Computer hardware (subsystems) ©Brooks/Cole, 2003 5.1 CENTRAL PROCESSING UNIT (CPU) -CPU performs operations on data. It has 3 parts: an Arithmetic Logic UNIT (ALU), a Control Unit, and a set of registers. -ALU performs arithmetic and logical operations. -Control Unit is responsible for selecting one operation. -Registers are fast stand-alone storage locations that hold data temporarily. ©Brooks/Cole, 2003 Figure 5-2 CPU - Data Registers (R1, …R3) hold intermediate results to speed up operations. - Instruction register (I) holds one fetched instruction from memory to be executed after interpretation. - Program Counter (PC) register points to the address of the next instruction in memory to be executed. ©Brooks/Cole, 2003 5.2 MAIN MEMORY - Main memory is a collection of storage location, each with a unique identifier called address. A program (data & Instructions should be stored in memory in order to get executed. - Data are transferred to and from memory in groups of bits called words - A word can be a group of 8-bits (1 Byte), 16-bits (2 Bytes), 32-bits (4 Bytes) or 64-bits (8 Bytes). -The total number of uniquely identifiable locations in memory is called address space. ©Brooks/Cole, 2003 Table 5.1 Memory units Unit Exact Number of bytes Approximation -----------kilobyte megabyte gigabyte terabyte petabyte exabyte -----------------------210 bytes 220 bytes 230 bytes 240 bytes 250 bytes 260 bytes -----------103 bytes 106 bytes 109 bytes 1012 bytes 1015 bytes 1018 bytes ©Brooks/Cole, 2003 Figure 5-3 Main memory -Because computers operate by storing numbers as bit pattern, the address is also represented as bit pattern -Address starts from 0 to last addressable word in address space. -To address 64 kB (216) of memory, you need to use 16 bit for addressing ©Brooks/Cole, 2003 Note: Memory addresses are defined using unsigned binary integers. In general, if a computer has N words of memory, you need An unsigned integer of size log2 N to refer to each memory location. ©Brooks/Cole, 2003 Example 1 A computer has 32 MB (megabytes) of memory. How many bits are needed to address any single byte in memory? Solution The memory address space is 32 MB, or 225 (25 x 220). This means you need log2 225 or 25 bits, to address each byte. ©Brooks/Cole, 2003 Example 2 A computer has 128 MB of memory. Each word in this computer is 8 bytes. How many bits are needed to address any single word in memory? Solution The memory address space is 128 MB, which means 227. However, each word is 8 (23) bytes, which means that you have 224 words. This means you need log2 224 or 24 bits, to address each word. ©Brooks/Cole, 2003 Memory Types - Two types of memory are available: RAM and ROM -Random Access Memory (RAM) can be read from and written to by the user. It is also volatile storage because it hold the information (program and data) as long as the power of computer is on. -RAM can be static RAM (SRAM) or Dynamic RAM (DRAM -Read-Only Memory (ROM) is nonvolatile storage and users can read it but can't write to it. PROM, EPROM, EEPROM are some variants of ROM. Programmable ROM can be written once by special equipment Erasable Programmable ROM can hold data that can be overwritten user. EPROM requires physical removal from Computer but EEPROM (electronically ..)does not need !! 2003 ©Brooks/Cole, Figure 5-4 Memory hierarchy - Computer users need a lot of memory that is fast and very inexpensive. - very Fast memory (Registers) is expensive and ,therefore, are limited. It is used continuously. -Fast memory (Cache memory) is not cheap &are used to store data that are accessed often. -Cheap memory (Main memory) are used for data that are not accessed very often. ©Brooks/Cole, 2003 Figure 5-5 Cache -Cache is placed between CPU and main memory and it contains a portion of the main memory. -When the CPU needs to access a word in main memory, it checks first the cache, and if the word is found there, it copies it. Otherwise, it access a block (more than one word) from the memory and copies it to cache. ©Brooks/Cole, 2003 5.3 INPUT / OUTPUT -It allows a computer to communicate with the outside world and store programs and data even when the computer is off. -Nonstorage devices can not store information. Keyboard , monitor, and Printer are nonstorage devices. - Storage devices can store large amount of information to be retrieved at a later time. They are nonvolatile devices and can either be magnetic (Hard disk) or optical (CD-R or DVD). ©Brooks/Cole, 2003 Figure 5-6 Physical layout of a magnetic disk ©Brooks/Cole, 2003 Figure 5-7 Surface organization of a disk ©Brooks/Cole, 2003 Figure 5-8 Mechanical configuration of a tape ©Brooks/Cole, 2003 Figure 5-9 Surface organization of a tape ©Brooks/Cole, 2003 Figure 5-10 Creation and use of CD-ROM Create: 1. Master; infrared laser, form Pit (hole=0), Land (no hole=1). 2. Mold create from the master. 3. Molten; polycarbonate injected. Speed 1x, 2x………40x= 6 Mbytes Application: In mass quantity ©Brooks/Cole, 2003 Table 5.2 CD-ROM speeds Speed Data Rate Approximation -----------1x 2x 4x 6x 8x 12x 16x 24x 32x 40x -----------------------153,600 bytes per second 307,200 bytes per second 614,400 bytes per second 921,600 bytes per second 1,228,800 bytes per second 1,843,200 bytes per second 2,457,600 bytes per second 3,688,400 bytes per second 4,915,200 bytes per second 6,144,000 bytes per second -----------150 KB/s 300 KB/s 600 KB/s 900 KB/s 1.2 MB/s 1.8 MB/s 2.4 MB/s 3.6 MB/s 4.8 MB/s 6 MB/s ©Brooks/Cole, 2003 Figure 5-11 CD-ROM format ©Brooks/Cole, 2003 Figure 5-12 Making a CD-R Create: 1. 2. 3. 4. No master, Mold, Molten. Reflecting made by Gold instead of Aluminium Pit and Land are simulated, by Dye between reflecting layer and Poly High Power laser Beam make Dark Spot in Dye create spot which is Pit Reading Land can be read as (u can see through) Pit as opaua (can not see through) ©Brooks/Cole, 2003 Figure 5-13 Making a CD-RW Create: Same as CD-R but uses Alloy which has to character (Transparent, noon transparent) Reading same as CD-R Erasing: as long as it is mix it can be chane by the laser beam ©Brooks/Cole, 2003 Table 5.3 DVD capacities Feature Capacity --------------------------------single-sided, single-layer single-sided, dual-layer double-sided, single-layer double-sided, dual-layer -----------4.7 GB 8.5 GB 9.4 GB 17 GB Digital versatile Disk: •the Pit is smaller 0.4 Microne (CD is .8) •Track are closer to each other •The Beam is Red Laser instead of infrared •To recoeded layer ©Brooks/Cole, 2003 5.4 SUBSYSTEM INTERCONNECTION ©Brooks/Cole, 2003 Figure 5-14 Connecting CPU and memory using three buses -Bus is made of several wires, each having a bit at a time -Data bus is used to transmit a word between CPU and memory. Therefore, the number of wires depends on the size of the word. - Address bus allows access to a particular word in memory. Therefore, it depends on the address space of memory. -Control bus carries communication between CPU and memory. the number of wires depends on the number of commands (read,write,..) a computer needs. ©Brooks/Cole, 2003 Figure 5-15 Connecting I/O devices to the buses -CPU and memory are electronic devices but I/O devices are electromechnical, magnetic, or optical devices. -I/O devices are slow and can not be connected directly to the buses. They are connected to I/O controller that handles the difference in nature between I/O devices and CPU and memory -I/O controller can be serial or parallel. A serial controller allow the transfer of one bit while parallel allows multiple bits at time ©Brooks/Cole, 2003 Figure 5-16 SCSI controller (Small Computer System Interface) -It has a parallel interface with 8, 16, 32 wires. -It provides a daisy chained connection with termination -Each device must have a unique address. ©Brooks/Cole, 2003 Figure 5-17 FireWire controller -It has a serial interface that can transfer 50 MB/sec. -It can connect up to 63 devices in daisy chain or tree connection -It needs no termination. ©Brooks/Cole, 2003 Figure 5-18 USB controller Universal Serial Interface - It is a serial controller that can transfer 1.5 MB/sec. - It is used to connect slower devices such as KB, mouse ©Brooks/Cole, 2003 Addressing Input/Output devices -CPU uses the same bus to read data from or write to main memory and I/O devices. -The only difference is the instruction to be executed. If it refers to a word in memory, data transfer is between Memory and CPU but if it identifies an I/O device, data transfer is between CPU and I/O device. - There are 2 methods to handle the addressing of I/O devices: Isolated I/O method and Memory-mapped I/O method. ©Brooks/Cole, 2003 Figure 5-19 Isolated I/O addressing -Instructions (test, read from, write to, control) for Memory and I/O devices are totally different. -For example, the command READ 05 can be used to read from memory the word 05 while the command INPUT 05 can be used to read from Input device 05. ©Brooks/Cole, 2003 Figure 5-20 Memory-mapped I/O addressing -CPU does NOT have separate instructions for memory and I/O devices. For example, the READ command is used for both. -Part of the memory address space is allocated to registers in the I/O controller. -Of course, this method uses smaller no. of instructions!! -Adv. Configure small number of Instructions -All memory instructions can be used by I/O Device -Dis. Size of the memeroy are reduced ©Brooks/Cole, 2003 5.5 PROGRAM EXECUTION -A program consists of set of instructions to process data -A computer executes the program to create output data from input data. -Both the program and the data are stored in memory -A computer executes the instructions using repeating machine cycle: fetch, decode, execute ©Brooks/Cole, 2003 Figure 5-21 Steps of a cycle The control Unit do the following: Fetch: copy the instruction to be executed from memory to IR. The address of that instruction is stored in the PC which should then be incremented. Decode: interprets the command in the instruction register as binary code to be executed. Execute: sends the order to a component of CPU. ©Brooks/Cole, 2003 Figure 5-22 Contents of memory and register before execution ©Brooks/Cole, 2003 Figure 5-23.a Contents of memory and registers after each cycle ©Brooks/Cole, 2003 Figure 5-23.b Contents of memory and registers after each cycle ©Brooks/Cole, 2003 Figure 5-23.c Contents of memory and registers after each cycle ©Brooks/Cole, 2003 Figure 5-23.d Contents of memory and registers after each cycle ©Brooks/Cole, 2003 Input/Output operations -There are 3 methods to synchronize the difference in speed between the CPU and I/O device in order to transfer data from I/O devices to CPU and memory and vise versa: 1- Programmed I/O wastes CPU time because CPU waits until I/O operation is executed (finished). CPU asking I/O constantly 2- Interrupt driven I/O allows the CPU to execute, in parallel other instructions while the I/O operation is executed. CPU not asking I/O constantly. I/O inform CPU 3- Direct memory access allows ,unlike the other methods, data to be transferred directly between memory and I/O device without going first into CPU registers. DMA has register to hold data after and before memory transform. ©Brooks/Cole, 2003 Figure 5-24 Programmed I/O -When CPU encounters an I/O instruction, it does nothing until the data transfer is complete. -CPU checks continuously the status of the device for each unit of data to be transferred. -Data are transferred from CPU to memory after input operation -Data are transferred from memory to CPU before output operation ©Brooks/Cole, 2003 Figure 5-25 Interrupt-driven I/O -CPU informs the I/O device that a transfer is going to happen and continue doing other jobs -When the device is ready, it informs (interrupts) CPU and data transfer can begin -Again, data are transferred between the device and CPU not directly to memory ©Brooks/Cole, 2003 Figure 5-26 DMA connection to the general bus ©Brooks/Cole, 2003 Figure 5-27 DMA input/output ©Brooks/Cole, 2003 5.6 TWO DIFFERENT ARCHITECTURES ©Brooks/Cole, 2003 • CISC (Complex Instruction Set Computer) – The stratgy is to have large set of instructions. Include complex – Program in CISC is easer because there is no different between Simple or Complex Instructions. – Program done in two level: • Instructions not executed by CPU directly it is run by operation called microoperation • Complex instructions are transform in to simple operation – – – – – This meeans we need speciall memory called MicroMemory. Programing use microopertion called Microprograming. Disadvantage: over head of this Microprograming using this Micromemory BUT it is for samll program Pentium • RISC (Reduce Instruction Set computer) – – – – The strategy is to use small number of instruction to do Minmum number of operation. Complex operation is Simulated by using set of operation Programming very difficult because Complex instruction simulated by simple instruction Apple PowerPC ©Brooks/Cole, 2003