GlueXMeeting_10MAY2010

advertisement

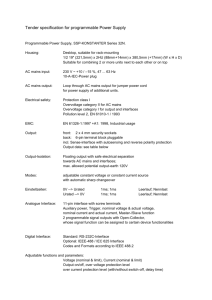

GlueX Collaboration Meeting 12GeV Trigger Electronics 10 May 2010 R. Chris Cuevas 1. FY10 Project Goals Update from January 2010 Collaboration Meeting 2. Hardware Design Status Updates 3. Summary NIM FY10 Project Goals • Baseline Improvement Activities (BIA) have been established for FY10 FADC250 Rev- BIAFAD Revision includes 12bit ADC and consolidation of FPGA which will reduce part count significantly. Use latest Xilinx technology and include new requirements. F1-TDC Rev-2 BIAF1T Revision includes 48 channel ‘mode’ for FDC, add VXS signaling, upgrade FPGA, add event RAM, and pulse output feature. SSP (Prototype) - BIATRG Complete schematic, board layout, assembly, and firmware for at least two units. GTP (Prototype) - BIATRG Complete schematic, board layout, assembly and firmware for a single unit. Complete VXS crate specification and procurement for ALL VXS crates needed for 12GeV applications. Allows for quantity price reduction and ‘phased’ delivery during installation period. 2 Hardware Design Status • SubSystem Processor (Prototype by end of June 2010!!) Ahead of schedule Board fabrication files checked and ready for order Components and assembly order prepared Firmware development on track • Global Trigger Processor (Prototype by end of FY10 will slip,,,) Specification has been updated and latest proposal presented and reviewed Schematic not started Schedule dependent on additional EE (Position open) • Crate Trigger Processor (No work plan for FY10) Two prototypes successfully tested! (FY09) Final revision in FY11 work plan • Signal Distribution switch (Revisions started – Welcome to Nicholas Nganga) Two prototypes successfully tested! (FY09) Final revision has been started and will extend into FY11 work plan 3 Hardware Design Status • Trigger Interface/Trigger Distribution (Latest revision by end of FY10 ) Work activity schedule created ( William Gu; Ed Jastrzembski) Initial version of TI/TD successfully tested FY09 Latest revision specification document has been updated Latest revision will be a single board design with TI/TD functionality Schematic capture complete Component placement complete Board routing complete Components ordered Firmware development on track • Trigger Supervisor (FY11-12 work plan) Specification has been created and reviewed Detailed work activity schedule will be created 4 Specification Status • VXS powered card enclosures ( Procurement by end of FY10 ) Crate specification has been created and ordering strategy discussed with procurement department. Multi-year procurement with delivery quantities per year to be determined. • Specification completed and Request For Information (RFI) has been prepared. • Accounts have been adjusted to reflect multi-year order and delivery schedule to reflect installation needs for both Halls D & B. • Trigger System Fiber Optics (FY11 work plan) Draft system diagram has been specified Final component specifications will need to be completed and ordered in FY11 5 SSP Layout Status Ben Raydo • SSP PCB Layout 100% - will be sent out for assembly in the next week or so • Assembly should arrive late May, module testing in June • Initial firmware is complete for multi-crate trigger testing (currently just energy sums) 6 SSP PCB Module Overview 8x 10Gbps Fiber Transceivers 4x LVDS/PECL/ECL Inputs 4x LVDS Outputs Ben Raydo 2x Bi-Directional Status NIM Ports LEDs VME Address DIP Switches DDR2 SO-DIMM (up to 4GBbyte) Jtag Power Supply Margin Header VME64x P2 VXS P0 VME64x P2 7 SSP Block Diagram Ben Raydo Front-Panel I/O To GTPs (Global-Trigger-Processors) 2x10Gbps L1 Streams Virtex 5 - FX70T 4Gbps VME Bridge - 4x 10Gbps Fiber Transceiver -Reed Solomon FEC Decoder - 500MB/s FX70T<->LX50T Bus -Used for VME Bridge - 4x 5Gbps FX70T->LX50T Bus -Used for L1 Streams HFBR-7934 -Single Cycle, BLT, 2eSST Support HFBR-7934 4x 5Gbps L1 Streams 4x 5Gbps L1 Streams Virtex 5 - FX70T 4Gbps VME Bridge DD2 SO-DIMM -Up to 4GB Memory Module - <60ns Random Access Time - 3.2Gbyte/sec burst rate 4-Channel Full Duplex 2.5Gbps Fiber Streams - 4x 10Gbps Fiber Transceiver -Reed Solomon FEC Decoder - 500MB/s FX70T<->LX50T Bus -Used for VME Bridge - 4x 5Gbps FX70T->LX50T Bus -Used for L1 Streams 10Gbps L1 Stream -Support for A24/A32, D32/D64 Transactions - 2x 10Gbps VXS Switch Links - VME64x Interface - 500MB/s FX70T<->LX50T Bus Used for VME Bridge - 8x 5Gbps FX70T->LX50T Bus Used for L1 Streams -DDR2 SO-DIMM Used for L2 dictionary HFBR-7934 4-Channel Full Duplex 2.5Gbps Fiber Streams 4-Channel Full Duplex 2.5Gbps Fiber Streams Virtex 5 – LX50T VME64x HFBR-7934 4-Channel Full Duplex 2.5Gbps Fiber Streams HFBR-7934 4-Channel Full Duplex 2.5Gbps Fiber Streams HFBR-7934 From CTPs (Crate-Trigger-Processors) Clock Distribution -Distributes to all FPGAs: 50MHz, 250MHz Clocks -Local 250MHz & 50MHz -SMA 250MHz, VXS-P0 SWA or SWB 10Gbps L1 Stream VXS-P0 Receives: CLK250,TRIG1,TRIG2,SYNC,LINKUP Transmits: TXDATA[3..0],Busy TX: 4x LVDS RX: 4x AnyLevel (LVDS,ECL,PECL) Bidirectional: 2x NIM 4-Channel Full Duplex 2.5Gbps Fiber Streams HFBR-7934 4-Channel Full Duplex 2.5Gbps Fiber Streams HFBR-7934 4-Channel Full Duplex 2.5Gbps Fiber Streams 8 Subsystem Processor: L1 Global Trigger Crate: Subsystem Energy Sum & Hit Pattern (10Gbps to GTP) • Sub-System-Processor (SSP) consolidates multiple crate subsystems & report final subsystem quantity to Global-Trigger-Processor (GTP) • 32bit quantity every 4ns Hit Pattern 10Gbps fiber optics Energy FCAL (11) BCAL (16) Tagger (2) ST (1) L1 Subsystems (# Crates) TOF (2) 9 1 1 2 1 2 1 2 2 1 D31 C31 B31 A31 Z31 C32 B32 A32 Z32 A4 D32 2 1 2 1 1 A5 C5 E5 F5 G5 A10 B10 C10 D10 E10 F10 G10 2 1 1 C6 E6 F6 G6 A11 B11 C11 D11 E11 F11 G11 1 2 1 1 2 E7 F7 G7 2 Z30 A30 B30 C30 D30 A1 B1 Z29 A29 B29 C29 D29 A3 B3 A4 B4 Z28 A28 B28 C28 D28 A5 A6 B6 Z27 A27 B27 C27 D27 A7 B7 C7 C4 E4 2 1 2 2 D7 C3 F4 G4 A9 B9 C9 D9 E9 F9 G9 1 2 C1 A2 F3 G3 1 G2 1 2 A8 2 A7 B8 C8 D8 E8 F8 G8 1 2 D1 E1 F1 G1 A6 B7 A3 A2 B6 C6 A1 C5 C7 B4 C4 B3 E7 F7 G7 C3 E6 F6 G6 1 2 B1 E5 F5 G5 4 25 1 C1 E4 F4 G4 2 D7 F3 G3 2 G2 1 2 D1 E1 F1 G1 2 1 2 2 21 1 1 A8 B8 C8 D8 E8 F8 G8 25 1 2 A9 B9 C9 D9 E9 F9 G9 Z26 A26 B26 C26 D26 1 3 6 4 2 0 1 2 1 2 A10 B10 C10 D10 E10 F10 G10 1 2 10 9 8 Z25 A25 B25 C25 D25 A11 B11 C11 D11 E11 F11 G11 7 5 3 2 1 1 2 1 1 1 1 1 2 2 2 1 2 1 2 2 2 Z24 A24 B24 C24 D24 1 2 2 2 1 1 1 1 1 2 1 25 2 2 1 Z23 A23 B23 C23 D23 1 2 1 2 2 1 1 2 2 11 2 Z22 A22 B22 C22 D22 2 1 2 16 15 14 13 12 10 9 2 2 2 2 1 1 1 1 2 1 1 1 1 2 2 1 1 2 1 2 2 21 21 12 Z21 A21 B21 C21 D21 1 2 2 1 1 1 2 1 2 1 2 1 1 12 12 21 2 2 2 1 1 2 1 2 1 1 1 1 1 1 1 1 2 Z20 A20 B20 C20 D20 2 2 1 2 2 1 1 2 1 2 2 2 2 2 2 2 2 1 1 1 2 1 2 1 Z19 A19 B19 C19 D19 1 2 2 2 1 1 1 21 2 1 1 2 2 1 2 1 1 2 3 4 5 6 7 8 1 2 2 1 1 2 2 1 2 Z18 A18 B18 C18 D18 12 1 2 2 1 1 2 1 2 2 25 2 1 2 1 1 2 2 1 1 2 2 1 External I/O 1 2 2 1 1 2 1 2 1 Z17 A17 B17 C17 D17 2 1 2 1 1 2 1 2 2 1 2 1 2 1 1 2 2 2 2 1 1 1 1 2 1 1 Z16 A16 B16 C16 2 2 1 2 2 1 1 2 1 2 1 D16 2 1 1 2 2 1 2 2 1 2 1 2 1 2 Z15 A15 B15 C15 D15 2 1 2 1 2 2 1 2 1 1 2 Z14 A14 B14 C14 D14 1 1 2 2 1 1 C12 B12 A12 Z12 B13 A13 Z13 2 2 2 1 D12 2 1 1 2 2 1 1 2 C13 2 D13 1 2 EP 1 2 2 1 1 2 1 1 2 1 2 2 2 1 1 1 2 1 2 1 1 2 2 2 Z11 A11 B11 C11 D11 1 2 1 2 2 1 1 1 2 2 2 1 1 2 1 2 1 1 2 1 2 1 2 17 2 1 2 25 2 1 1 2 Z10 A10 B10 C10 D10 2 1 2 1 2 1 1 2 1 1 2 1 2 2 1 2 2 1 1 Z9 A9 B9 C9 D9 21 2 2 2 1 1 2 1 2 1 1 1 1 1 1 1 2 2 2 2 2 1 1 2 2 1 Z8 A8 B8 C8 D8 2 2 1 1 2 1 2 1 1 1 2 Z7 A7 B7 C7 D7 1 17 1 2 2 1 1 2 2 2 1 2 2 2 1 2 1 Z6 A6 B6 C6 D6 2 2 1 1 2 1 1 2 2 1 2 2 1 2 2 1 2 1 2 1 2 2 1 25 2 1 1 1 2 2 1 1 Z5 A5 B5 C5 1 2 2 2 2 1 2 2 1 1 2 1 1 2 1 2 2 D5 1 2 1 1 Z4 A4 B4 C4 D4 1 1 2 2 1 4 6 5 2 1 2 2 1 2 1 2 1 2 2 1 2 1 1 1 2 Z3 A3 B3 C3 D3 2 1 1 1 1 1 2 1 2 1 2 1 2 2 2 2 1 2 1 1 2 1 1 Z2 A2 B2 C2 D2 1 2 3 2 1 1 2 1 2 1 2 1 2 2 1 25 2 1 2 1 2 Z1 A1 B1 C1 D1 21 2 1 1 2 1 2 1 1 1 2 1 1 2 1 2 2 2 1 2 1 1 1 2 2 2 2 1 1 2 2 1 1 1 1 2 2 2 2 2 1 2 1 17 1 1 1 2 1 1 2 2 1 2 2 1 2 2 1 3 2 1 2 1 2 1 1 2 2 2 1 2 1 1 2 1 1 2 1 2 1 1 1 1 2 1 1 2 1 2 2 2 1 1 2 2 1 2 2 2 2 1 2 2 1 2 1 2 2 1 1 2 2 2 1 1 1 1 2 1 2 1 1 2 2 2 1 1 2 2 1 2 2 1 2 1 2 1 2 1 2 2 1 1 1 1 2 1 2 1 2 1 2 1 2 2 2 1 1 1 2 1 1 2 2 1 2 1 2 1 2 1 2 1 2 1 2 65 2 1 1 2 2 1 2 1 1 2 2 1 2 1 2 2 2 1 1 2 1 2 1 1 1 2 1 2 1 2 1 2 2 1 1 2 2 1 2 1 1 1 21 2 1 2 21 1 1 2 1 2 12 1 1 2 1 12 1 1 2 2 1 2 2 2 1 2 2 2 1 2 1 1 2 1 2 1 1 2 1 1 2 2 1 1 1 2 1 2 1 2 1 1 2 1 1 1 2 2 2 1 2 2 2 2 2 2 1 2 2 1 2 1 2 2 2 1 33 2 1 1 2 1 2 1 2 33 1 1 2 1 2 2 1 1 1 2 2 1 1 2 1 2 2 2 1 1 2 2 1 2 2 1 1 2 17 2 2 2 1 2 2 17 1 1 2 17 1 1 1 1 2 1 1 2 1 1 1 2 1 2 2 1 1 2 1 1 2 2 1 2 2 2 32 31 30 29 28 27 26 25 1 2 2 1 2 2 1 1 2 2 2 1 1 1 2 2 1 1 24 1 1 2 2 2 2 1 23 2 2 2 1 1 1 1 3 22 1 2 1 2 1 1 2 2 2 1 1 1 1 2 2 1 2 1 1 1 1 4 21 2 2 2 2 1 2 2 1 2 2 1 2 5 20 1 2 19 2 2 1 2 2 2 1 1 7 2 8 17 1 1 2 8 7 18 2 1 6 1 1 1 1 2 2 2 1 1 2 1 1 2 2 1 2 1 3 6 2 1 2 0 1 2 9 10 11 12 13 14 15 16 2 1 1 2 1 2 2 1 2 1 2 1 1 2 4 5 2 1 1 1 2 2 2 2 1 2 1 1 1 2 1 2 2 2 2 1 1 1 1 2 2 2 2 2 1 2 1 1 1 1 2 2 2 2 1 2 1 2 1 1 1 2 1 2 2 2 2 1 EP 1 2 1 1 2 1 1 2 1 2 1 1 1 1 1 2 1 1 1 2 2 2 1 2 1 A3 A1 2 B3 C3 F3 G3 2 1 2 1 2 A4 B4 C4 E4 F4 G4 1 2 2 1 2 1 2 7 1 1 2 1 2 1 2 1 A7 B7 C7 D7 E7 F7 G7 1 1 2 1 2 2 1 1 2 11 6 1 1 A31 Z31 A32 Z32 2 1 2 2 1 1 2 B31 2 10 1 1 2 2 24 B32 A6 B6 C6 E6 F6 G6 2 2 1 2 C31 2 1 2 1 23 2 D31 9 3 22 1 2 1 2 C32 2 1 1 2 8 2 1 2 1 2 D32 A5 C5 E5 F5 G5 1 1 1 4 2 1 1 A2 2 2 2 1 2 2 1 5 1 21 1 2 2 1 1 1 2 1 1 2 6 2 1 1 1 1 7 2 2 20 2 1 2 1 19 2 2 1 8 2 G2 1 1 2 1 18 1 17 2 2 B1 C1 D1 E1 F1 G1 2 2 2 1 1 2 9 10 11 12 13 14 15 16 2 A8 B8 C8 D8 E8 F8 G8 2 1 2 1 32 31 30 29 28 27 26 25 2 1 1 2 5 12 1 2 1 2 1 2 1 1 1 2 1 13 4 1 2 Z30 A30 B30 C30 D30 A9 B9 C9 D9 E9 F9 G9 1 1 2 1 1 1 1 1 1 2 A10 B10 C10 D10 E10 F10 G10 2 1 1 2 2 1 1 14 3 2 2 2 2 2 2 2 2 2 1 2 1 2 2 1 2 15 2 1 2 1 1 2 Z29 A29 B29 C29 D29 2 A11 B11 C11 D11 E11 F11 G11 1 2 1 2 2 1 1 1 2 1 2 2 1 2 1 2 2 1 16 1 1 1 2 2 1 2 2 1 2 1 1 2 B27 A27 Z27 A28 Z28 1 B28 2 10 7 1 1 1 2 1 2 1 2 2 1 C27 9 8 1 2 D27 2 2 1 C28 1 2 2 1 D28 1 1 1 2 2 2 1 2 1 2 1 2 2 1 1 2 1 2 1 1 2 1 2 6 2 2 1 2 11 1 2 1 1 2 1 Z26 A26 B26 C26 D26 1 1 5 12 2 1 2 1 2 2 2 1 1 1 2 2 2 2 1 1 1 2 2 1 2 1 4 1 2 2 1 2 1 13 2 1 1 2 1 2 2 1 Z25 A25 B25 C25 D25 1 2 1 1 1 2 2 2 1 2 14 3 2 1 2 2 15 1 2 2 Z24 A24 B24 C24 D24 1 2 16 1 2 1 1 2 1 2 1 2 1 2 2 1 2 1 Z23 A23 B23 C23 D23 1 2 1 1 2 1 1 2 1 2 2 1 Z22 A22 B22 C22 D22 1 2 1 2 2 1 2 2 1 2 1 1 2 2 1 1 2 2 1 1 Z21 A21 B21 C21 D21 2 1 2 1 2 2 1 1 1 2 1 2 1 2 2 1 Z20 A20 B20 C20 D20 2 2 1 1 1 1 2 2 2 1 1 1 2 2 1 2 2 1 2 1 1 2 Z19 A19 B19 C19 D19 1 2 1 2 2 1 2 2 2 2 1 1 2 EP EP 2 1 2 1 1 1 1 1 2 2 Z18 A18 B18 C18 D18 1 2 1 2 2 1 1 2 1 2 2 1 2 1 2 2 1 2 2 2 1 2 1 1 C16 B16 A16 Z16 B17 A17 Z17 2 D16 2 2 1 1 Z15 A15 B15 C15 D15 1 1 2 1 12 1 1 2 3 C17 1 2 2 1 1 2 4 D17 2 1 1 1 2 1 2 2 2 1 5 1 6 1 1 1 1 2 2 2 2 1 2 3 1 1 1 2 2 1 1 2 4 1 2 2 2 1 1 1 1 2 2 1 1 2 2 1 1 2 2 2 EP 2 1 2 1 2 2 1 2 2 1 1 2 7 8 2 1 2 1 2 2 1 Z14 A14 B14 C14 D14 1 2 1 2 1 2 2 1 2 1 1 1 2 9 1 1 Z13 A13 B13 C13 2 2 1 D13 10 1 2 2 1 2 2 2 11 2 1 Z12 A12 B12 C12 2 1 2 D12 1 2 11 12 1 2 1 1 2 1 1 1 2 1 2 1 2 2 2 1 2 2 1 2 1 Z11 A11 B11 C11 D11 13 14 2 1 2 2 2 1 1 1 2 1 1 1 2 1 1 2 1 1 1 Z10 A10 B10 C10 D10 15 16 2 1 2 2 2 1 2 1 2 1 TrgSv Rev. 2 interface 2 1 1 8 Optical Transceivers HFBR-7924 4 2 2 1 2 1 C9 Z9 A9 B9 2 1 2 2 D9 2 17 18 1 2 1 2 2 1 1 1 1 1 2 19 20 2 1 2 2 1 Z8 A8 B8 C8 D8 1 2 2 1 1 2 1 2 1 1 21 22 2 1 1 2 1 2 Z7 A7 B7 C7 D7 2 1 2 1 2 2 1 2 2 2 1 1 2 2 2 1 2 23 24 2 1 1 1 2 1 Z6 A6 B6 C6 D6 2 2 2 1 1 2 1 1 6 5 4 3 2 1 1 1 1 1 1 1 2 1 2 1 2 2 2 Z5 A5 B5 C5 D5 2 1 2 2 2 1 1 2 1 2 2 1 1 2 2 Z4 A4 B4 C4 D4 1 2 2 1 2 1 8 7 2 6 2 5 4 3 2 1 2 2 1 1 1 1 2 1 1 2 1 2 2 2 1 8 7 2 1 9 6 2 10 5 D2 C2 B2 A2 Z2 D3 C3 B3 A3 Z3 1 1 2 1 9 Z1 A1 B1 C1 D1 2 1 10 1 1 11 1 12 13 14 1 1 2 2 15 2 2 1 11 4 16 2 1 2 12 3 2 1 1 2 13 2 2 2 1 1 2 1 2 14 1 Trigger Interface & Distribution 1 William Gu VMEPROM (FPGA firmware) Emergency/remote re-programming Xilinx Virtex-5 LX30T-FG665 VME 64x VXS P0 TD mode: from SD TI/TS mode: to SD One dedicated link for redundant data collection Trg/Clk/Sync outputs On row_C 10 TID William Gu • • • • • • • Trigger/Clock/Sync distribution/Busy Two sided, 12-layer VME board (6Ux160mm) PCB layout finished PCB fabrication after independent review/check FPGA firmware development underway Board testing in the summer. (Virginia summer is earlier) Module has been designed to function as Trigger Interface or Trigger Distribution • Module can be configured to function as a Trigger Supervisor (Trigger signals received on front panel I/O connector) • VXS payload board format • Provides communication from VME to SD & CTP modules via I^2C serial links. 11 William Gu TID Fiber TD with TS function TI#1 SD#1 FADC#1-16 TI#2 SD#2 FADC#1-16 VXS TI#8 VXS VXS SD#8 FADC#1-16 SD#9 Test/Commissioning setup: Up to 9 crates Can be supported 12 Level 1 & Trigger Distribution VXS-Crate SD TD TD TD TD TD TD TS Trigger Distribution Crate CPU TD TD TD TD TD TD L1 Subsystem Data Streams (hits & energy) Trigger Decisions CPU SSP SSP SSP SSP SSP SSP GTP GTP SSP SSP SSP SSP SSP SSP TI Global Trigger Crate VXS-Crate Fiber Optic Links SSP can manage 8 CTP (Crates) Fiber Optic Links TD can manage 8 TI (Crates) Clock Trig1 Trig2 Sync Busy Front-End Crates VME Readout to Gigabit Ethernet Up to 128 front-end crates 13 Global Trigger Processor: (GTP) • Global Trigger Processor (GTP) receives all subsystem Level 1 data streams • Trigger decisions made in GTP and distributed to all crates via the Trigger Distribution (TD) modules in the Trigger Supervisor Crate Up to 8x L1 Crates per SSP FCAL (Energy) SSP SSP BCAL (Energy) SSP SSP TOF (Hits) GTP SSP Start Counter (Hits) GTP SSP Tagger (Hits) SSP from CTPs up to 8 SSP Modules (64 L1 Front-End Crates) Each Connection: 8Gbps SSP->GTP (32bits every 4ns) Trigger Decisions to Trigger Distribution Crate 14 Global Trigger Crate VXS Pair Map • SubSystem Processors are Payload board format and will communicate with two GTP •Note TI mapping is identical to Front-End Crate • GTP must also provide SD fanout functions for SSP payload modules 15 GTP Specification Update presented at Online Working Group Meeting 16 • Virtex 5 devices available now that have high GigaBit transceiver counts capable of managing the data from up to 8 Sub-System Processors • GTP logic will effectively have all trigger data from up to 64 Level 1 crates in one FPGA. 17 • Quick view of proposed component layout using Virtex 5 FPGA • Routing will be dense for Gigabit links from each SSP ( 4 links * 8 SSP ) • GTP must manage the SD functions, but this should be feasible • Power and cost are reduced from original proposal 18 Discriminator Status Ben Raydo (Not truly trigger system hardware, but very nice new development) • 16 Channel dual-threshold discriminator prototypes are in house: -2 units for Hall D -5 units for Hall B • Prototype modules will be released in the next week for halls to use. • Significantly cheaper than V895: -cost < $2,000 • Provides several features not found on V895: -32bit scalers on all channels at both thresholds -Calibrated pulse widths: from 8 to 40ns -Trimmed input offset (<2mV error) -Second 34pin output connector is fully programmable. -Able to perform logic based on all channels at both thresholds 19 Ben Raydo 16 Channel VME Discriminator Block Diagram 20 Schedules, work plans for FY11 - FY13 • FY10 design projects are at full resource pace! FADC250 Production version at end of FY10 F1TDC-V2 SSP Prototype by end of June 2010 TI-TD Prototype(s) by end of summer 2010 16 Channel Discriminator/Scaler (Hall B requirement) 7 ‘production’ units under test now VXS Crate Specification At the RFI stage and accounts for each year allocated GTP Need new EE full time, but we will have to keep moving forward • Baseline Improvement Activities (BIA) review upcoming to review FY11 projects • Several of the board projects listed above will be available before FY11 begins • FY11 will be an intensive year of significant ‘system’ level testing to assure that these boards are ready for final production quantity orders in FY12 21 Summary (Almost identical to 28-Jan summary) • FY10 board design projects are on track and prototypes will be here soon!! • As always GREAT WORK on keeping these projects on schedule • Work activities exceed EE and E-Designer resources, but we push forward, • GTP design activities must be started soon independent of new EE hire status • 3nd annual 12GeV Trigger Workshop will be @CNU – 8 July 2010 • FINAL VXS pair mapping has been established so other groups (Hall A, Hall B) are able to start their custom VXS payload modules. (Super BigBite will use VXS payload modules for GEM tracker) • Weekly 12GeV Trigger meeting has produced good discussions and ideas for implementation of system level test programs that will be essential for commissioning the DAQ/Trigger/Readout system in the Hall. ( See Alex’s talk) • Looking forward, the FY11 – FY13 schedule appears to be reasonable, (labor $$ included), but detailed work activities will need to be created to assure success. 22 Recent Applications with Level 1 Hardware TID Test/Commissioning setup: Up to 9 crates TI#1 SD#1 FADC#1 TI#2 SD#2 FADC#2 Can be supported TD with TS function Fiber VXS VXS SD#8 TI#8 FADC#16 TID boards Luxury Setup (optional): Subsystem control (two fibers on TI) VXS TS SD TD#1 SD#9 TI#1 SD TID#n SubSys TS Fiber TD#2 TI#2 FADC#1 VXS SD VXS FADC#2 TD#16 TID#m SubSys TS TID boards TI#8 SD FADC#16 PREx -- HALL A Moller Polarimeter Application LEFT H. Dong RIGHT When TRIGGER condition is met, send data that cause TRIGGER. 1 2 SCIN TILL ATOR 1 2 3 3 4 4 1 2 3 CAL ORI MET ER 4 1 2 3 4 4 SCIN TILL ATOR CAL ORI MET ER TRIGGER condition (or): CL.AND.CR prescaled from 1 to at least 1000 CL prescaled from 1 to at least 1000 CR prescaled from 1 to at least 1000 CR = ΣI=1,4∑j=1,2 PJI > threshold CL = ΣI=1,4∑j=1,2 PJI > threshold SL = (ΣJ=1,2 S1J > threshold) or (ΣJ=1,2 S2J > threshold) or 4 (ΣJ=1,2 S3J > threshold) or (ΣJ=1,2 S4J > threshold) SR = (ΣJ=1,2 S5J > threshold) or (ΣJ=1,2 S6J > threshold) or (ΣJ=1,2 S7J > threshold) or (ΣJ=1,2 S8J > threshold) 4 4 9-12 5-8 13-16 FADC-250 1-4 ON BOARD SCALER (COUNTER) to be read out by a separate trigger (helicity and gate bits) at the helicity cycle of 30 to 2kHz. • CL and CR • CL and SL • CR and SR • CL and CR and SL and SR • CL and CR and (SL and SR delayed > 100 ns) B. Raydo Trigger application example Implemented with CAEN1495 2 Fully Prototyped Front-End Crates S S P T D * CPU - 6100 F A D C 2 5 0 CPU - 6100 L1 Crate Sum 10Gbps Stream 16 test signals distributed to 6 FADC boards Trigger Decision F A D C 2 5 0 F A D C 2 5 0 C T S P # D 1 “davw1” VXS crate C T S P # D 2 Trigger Clock Sync Busy F A D C 2 5 0 F A D C 2 5 0 T I F A D C 2 5 0 T I “davw5” VXS crate *SSP function embedded inside 2nd CTP Synchronized Multi-Crate Readout • CTP #2 is also acting as an SSP (by summing the local crate + CTP#1 sum over fiber • A programmable threshold is set in CTP, which creates a trigger when the global sum (6 FADC boards => 96 channels) is over threshold. • Example test with a burst of 3 pulses into 16 channels across 2 crates/6 FADC modules A 2μs global sum window is recorded around the trigger to see how the trigger was formed: Example Raw Event Data for 1 FADC Channel: B. Raydo 2 Crate Energy Sum Testing Global Sum Capture (at “SSP”): Input Signal to 16 FADC250 Channels: Raw Mode Triggered Data (single channel shown only): • Threshold applied to global sum (96 digitized channels) produces 3 triggers. • Raw channel samples extracted from pipeline shown for 1 channel. • Runs at 250kHz in charge mode • Latency: 2.3µs(measured) + 660ns(GTP estimate) < 3µs B. Raydo Synchronized Multi-Crate Readout Rates • FADC event synchronization has been stable for several billion events @ ~150kHz trigger rate. • Have run up to 140kHz trigger rate in raw window mode, up to 170kHz in Pulse/Time mode. • Ed Jastrzembski has completed the 2eSST VME Interface on FADC allowing ~200MB/s readout Single Crate 12 signals distributed to four FADC250 18% Occupancy B. Raydo GlueX Level 1 Timing