Sin título de diapositiva

advertisement

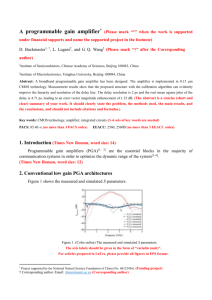

Non-linear dynamic range compression for the CTA camera I. Introduction II. DR compression in physics III. Non-linear amplification IV. Implementation (technology) V. Discussion VI. References ELEC/FPI CTA WP meeting- Munich, May 2008- D. Gascón (ICC – UB) I. Introduction: requirements • Dynamic Range (DR) for single photon resolution is 18 bits (100 dB approx): – Signal DR is from 1 to 6000 phe. – About 50 bins for single phe fit. • • An 18 bits resolution is not needed for full signal range Two possible solutions to simplify electronics: 1. Two gains and automatic gain switching mechanism. Only the very front end part of the electronics is duplicated. Not discussed here. 2. Non linear amplification of photo-sensor signal to perform DR compression. After A/D conversion the pulse shall be reconstructed by digital processing. • • Possible non-linear transfer function: piecewise linear with gain ratio 20:1 between smallest and highest gain. Logarithmic function could be considered. Requirements for a non-linear compressor: – – – – – – – The compressor must deal with an input dynamic range of about 100 dB. Bandwidth (BW) > 300MHz for all the gain. Output voltage range between 0-2 or 3 V. Very low temperature dependence. A large slew rate ~3000V/µs. Low noise. Series noise < 3nV/Hz and parallel noise < 30 pA/Hz. The precision of the decompression must be better than 1%. I. Introduction: non-linear transfer function 1 0,15 0,9 0,125 0,8 0,1 Output [V] Output [V] 0,7 0,6 0,5 0,4 0,075 0,05 0,3 0,2 0,025 0,1 0 0 0 1000 2000 3000 4000 Input signal [phe] • • • 5000 6000 0 10 20 30 40 50 60 70 80 90 Input signal [phe] Possible piecewise linear (5 regions) transfer function. Gain ratio 20:1, output is normalized to 1 V. How to obtain a compressor with such a transfer function? 1. 2. 3. How to fix the number of linear pieces? How to determine the value of the slopes and of the breakpoints? How to design a circuit with such a response? 100 II. DR compression in physics: computation of the transfer function • Typically the resolution of a detector depends on the input signal. For photon detectors: ENC 2 Si Si • ENF ENC n phe n phe GP 2 Characteristic of compression is usually ([1], [2], [3]) determined by: – – • ENF ·n phe GP n phe Dependence on signal of the resolution of the sensor. Requirement: quantization error << resolution of the detector. Quantization process matched to detector resolution, for and LSB referred to the input: Si LSB Si k • With N(nphe) as ADC counts corresponding to nphe: lim n phe 0 • • • N n phe n phe 1 k LSB n phe Si Using definition of detector resolution, a logarithmic function is obtained at the limit ([1], [2]). Difficult to implement. Bilinear and multilinear piecewise functions are used. Method to determine slopes and breakpoints minimizing the error at the initial part of each linear part ([1], [2]) : • • Choose the number of slopes (depends on implementation). Fix the factor k and the input an output ranges and resolutions. II. DR compression in physics: AUGER fluorescence camera • • • • A bilinear compressor has been designed for AUGER camera using previous method ([1], [4]). A DR of 16 dBs is matched to a 12-bit ADC. Compressor is based on closed loop operation of amplifiers A1 and A2. Fluorescence signal: – – • Trapezoidal shape From few hundreds of ns to several µs. Very difficult to achieve CTA BW with this topology. II. DR compression in physics: effects of amplifier BW • • • • • Insufficient bandwidth causes signal distortion: reconstruction is not possible by a first order system [5]. Bandwidth an slew rate effects are studied [5] for a multistage open loop compressor [3] (topology reviewed in next section). Typical behavior but precise results depend on the pulse shape and on circuit implementation. Settling time is 15 ns, not enough for CTA. How to implement? state of the art in electronics. Error at peaking time III. Non-linear amplification: diode vs multistage log amps • • • Non-linear amplifiers: instrumentation, RF, RADAR, LIDAR and optical fiber. Logarithmic amplifier is the most widely used non-linear amplifier. Two main types: diode and multistage log amp [6]. Diode log amp Multistage log amp Gain: A Limit: VL • DR >120 dB using diode connected BJT (subth MOS) • BW limitation: Miller effect + non-linear diode resistance. • Not used in HF applications. • Two types of multistage log amps: • Cascade of limiting amplifiers. • If stages “i” limits, output is (n-i)·VL+i·A·Vi • Inputs related with a ratio R correspond to outputs related by an increment (approx): logarithmic operation. • Piecewise linear approximation of a logarithm. 1. Successive detection log amps: logarithm of the envelope of the signal. Used to detect “slow” modulating signals or for receiver signal strength indicator (RSSI). 2. True or video log amps (TLA): instantaneous approximation to the logarithm of the signal. III. Non-linear amplification: TLAs • • • • Higher log DR and gain for series architectures. Higher BW for parallel summation TLAs Progressive compression parallel summation TLA (provided delay of different paths is matched). Mathematical description of non-linear transfer function in terms of circuit parameters. Method to synthetize piecewise linear compression functions ! Series linear-limit TLA Parallel amplification parallel summation TLA IV. Implementation: state of the art on HF TLAs • It is not enough to reproduce an adequate transfer function • BW (pulse distorsion), noise, accuracy f(implementation). • Commercial circuits for DC applications (diode logarithmic) or for RSSI (successive detection amplifiers). • State of the art on HF TLA ASICs: Ref. Topology Technology Bandwidth Rise / Fall time [ps] Log. DR [7] Series GaAs MESFET 0.5- 4 GHz - 70 dB [8] Parallel Si Bipolar fT=35 GHz DC - 4 GHz 100 /100 40 dB [9] Parallel SiGe HBT fT=47 GHz DC - 6 GHz 50 / 50 50 dB • Temperature and offset compensation DC methods are proposed. • SiGe 0.35 µm BiCMOS AMS technology, HBTs of fT=60 GHz . • Rough estimation of cost: 5 to 10 €/chip (only for production, 105 units). IV. Implementation: CMOS? • Single front end chip option (ampli + analogue memory + ADC + FIFO …) favours CMOS because some blocks already exists on CMOS. • No reports on HF CMOS TLAs. • Successive detection amplifiers (RSSI). • The limiting amplifier is similar to the basic amplifier of a TLA. • High bandwidth CMOS amplifiers have been reported: 400 MHz (0.6 µm [10]) and >900 MHz (0.35 µm [11]). • Noise should be studied in the first linear region: – – Noise is highest at lowest signal level (gain decreases as signal increases) It is assumed that the noise in the first amplifier dominates (enough gain). • Noise for > 900 MHz BW CMOS amplifier ([11]). is 180 µV, thus < 6 nVHz. • Noise for the BJT TLA in [8] is < 10 nVHz. V. Discussion • We have presented methods to: – Define a piecewise linear transfer function that preserves detector resolution. – Synthesize a circuit with such a function. • According to the state of the art of RFICs it seems possible to implement a TLA with such a function on SiGe BiCMOS technologies and likely on CMOS technologies. • Nevertheless the requirements of the circuit are very demanding (to the 1% accuracy). • BW limitation or inaccurate calibration (matching, device parameter variability…) could make impossible to reconstruct the pulse through digital signal processing. • If non-linear DR compression is considered an option for CTA a circuit demonstrator would be needed (simulation to start). • CMOS or BiCMOS? / Single front end chip or separated chips? • The full path of signal processing should be simulated: study timing and amplitude accuracy on reconstructed pulse. VI. References [1] P.W. Cattaneo, “The compression function for the fluorescence detector of the Auger experiment”, Auger GAP Note 1999002, February 1999. [2] P.W. Cattaneo, “Optimization of the multilinear compression function applied to calorimetry”, Nucl. Instr. and Meth. A 479, 2002. [3] A. Dell'Acqua et al., “A digital front-end and readout microsystem for calorimetry at LHC”, IEEE Trans. Nucl. Sci. NS-40 4 (1993), pp. 516–531. [4] P. F. Manfredi, M. Manghisoni, L. Ratti and V. Re, “A bilinear analog compressor to adapt the signal dynamic range in the AUGER fluorescence detector”, Nucl. Instr. and Meth. A 461, 2001. [5] W. Kurzbauer and B. Lofstedt, “Investigations of the dynamicnext term compression principle for fast detector pulses”, Nucl. Instr. and Meth. A 396, 1997. [6] W. Kester, J. Bryant, B. Clarke and B. Gilbert “Dynamic Range Compression”, High Speed Design Techniques Section 3: RF/IF Subsystems, Analog Devices. [7] M. A. Smith, "A 0.5 to 4 GHz true logarithmic amplifier utilizing monolithic GaAs MESFET technology" Microwave Theory and Techniques, IEEE Transactions on , vol.36, no.12, pp.1986-1990, Dec 1988 [8] C.D. Holdenried, J.W. Haslett, J.G. McRory, R.D. Beards, and A.J. Bergsma, “A DC-4GHz true logarithmic amplifier: Theory and implemenation,” IEEE J. of Solid State Cir., vol. 37, no. 10, pp. 1290–1299, Oct.2002. [9] C. D. Holdenried and J.W. Haslett, "A DC-6 GHz, 50 dB dynamic range, SiGe HBT true logarithmic amplifier," Circuits and Systems, 2004. ISCAS '04. Proceedings of the 2004 International Symposium on , vol.4, no., pp. IV-289-92 Vol.4, 23-26 May 2004. [10] C. C. Lin; K.H. Huang and C. K. Wang, "A 15mW 280MHz 80dB gain CMOS limiting / logarithmic amplifier with active cascode gain–enhancement," Solid-State Circuits Conference, 2002. ESSCIRC 2002, vol., no., pp. 311-314, 24-26 Sept. 2002. [11] S. Ho, "A 450 MHz CMOS RF power detector" Radio Frequency Integrated Circuits (RFIC) Symposium, 2001. Digest of Papers. 2001 IEEE , vol., no., pp.209-212, 2001. [12] D. Micusik and H. Zimmermann, "130dB-DR Transimpedance Amplifier with Monotonic Logarithmic Compression and HighCurrent Monitor" Solid-State Circuits Conference, 2008. ISSCC 2008. Digest of Technical Papers. IEEE International , vol., no., pp.78-597, 3-7 Feb. 2008. Back-up Experience on ASIC design • Technical staff of ICC of the University of Barcelona (UB) has experience on ASIC design for particle physics. • We have experience for a bandwidth up to 100 to 200 MHz. • But we have been collaborating for many years with the Electronics Department of the UB. – Microelectronics design group • Experience on ASIC for instrumentation, smart sensors, optoelectronics and micro-robotics. • Several CMOS (up to 130nm) and bipolar technologies. • Design tools: Cadence, Mentor, Synopsys, Sentaurus, etc. • Test facilities for mixed mode electronics. – RF/Microwave group • Experience on RF ICs for communications up to few GHz. • Experience on CMOS and SiGe technologies • Design tools: ADS, Cadence, EM simulators. • Test facilities for RF including EMI certification lab. Experience on ASIC design