2.4.2.A Programming Tutorial

advertisement

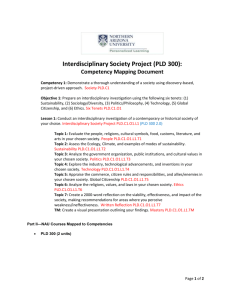

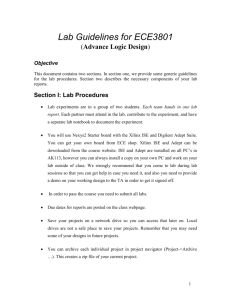

Activity 2.4.2 Introduction to Programmable Logic Devices: Programming Tutorial (DLB/Xilinx 12.4) Introduction When circuit designs become too large or complex to realistically breadboard, designers often use a Programmable Logic Device to (PLD) to prototype and test a circuit. A PLD is an integrated circuit whose logic function is user-configurable. Unlike discrete logic gates such as the AND, OR, NAND, and NOR gates, whose functionality is fixed when they are manufactured, a PLD must be programmed prior to being used. The first user-configurable PLD was introduced in 1978. This PLD was called a Programmable Array Logic (PAL), and it contained 24 user input/output signals. Over the three decades since the PAL was first introduced, the complexity of the devices and level of integration has increased significantly. The current state-of-the-art for PLDs is the Field Programmable Gate Array (FPGA). It contains 232 user input/output signals. In this activity you will learn how to use the Circuit Design Software (CDS) and the Xilinx Programming Software (XPS) to program the Field Programmable Gate Array (FPGA) on the Digital Logic Board (DLB). Equipment These instructions assume that all necessary software has been installed and configured by your teacher in the DE classroom. If you are not in a DE classroom environment, and you wish to install all software associated with the Digital Logic Board (DLB), please refer to the DMS Startup Instructions v2014. Digital Logic Board (DLB) Hardware Platform: Digital Logic Board (DLB) Circuit Design Software (CDS): Multisim 12.0.1 Xilinx Programming Software (XPS): NI LabVIEW FPGA Xilinx 12.4 SP1 Tools Note: Xilinx 12.4 is used to create a bit file and load it to the FPGA. It is not necessary to open Xilinx tools to load the FPGA using this process outlined in this document. See DMS Startup Instructions v2014 for full classroom install guide. Note: Xilinx does not currently support Windows 8. © 2014 Project Lead The Way, Inc. Activity 2.4.2 Introduction to Programmable Logic Devices: Programming Tutorial (DLB/Xilinx 12.4) – Page 1 Digital Logic Board (DLB) Transfer → Export to PLD Process Part 1: Setting up the CDS (Multisim) in PLD Mode 1. Start the CDS. Select: Options → Global Preferences. 2. Select: Options → Global preferences → Paths → Miscellaneous → Xilinx tool path. Make sure the Xilinx tool path is set to C:\NIFPGA\programs\Xilinx12_4\ISE a. Note: Your instructor may have a different path they wish you to navigate to. 3. Select: Apply. Select: OK. a. Note: If your classroom supports both the Digital Logic Board (DLB) and Digital MiniSystem (DMS), you will need to check this path in Global Preferences to make sure the correct Xilinx Software is selected. See Page 8. 4. Create a new folder and name it “Tutorial”. Make sure this folder is in a location students typically have access to if using a computer that does not have full admin rights. 5. Select: File → New → PLD Design. This will open the PLD Wizard. © 2014 Project Lead The Way, Inc. Activity 2.4.2 Introduction to Programmable Logic Devices: Programming Tutorial (DLB/Xilinx 12.4) – Page 2 6. New PLD Design – Step 1 of 3: a. Select: Use standard configuration b. Select: NI Digital Electronics FPGA Board c. Select: Next 7. New PLD Design – Step 2 of 3: a. PLD Design name: Name this file “Tutorial”. Note: Numbers, spaces, and some special characters are not accepted in file names by the XPS, which you will use later in this tutorial. Select: Next. © 2014 Project Lead The Way, Inc. Activity 2.4.2 Introduction to Programmable Logic Devices: Programming Tutorial (DLB/Xilinx 12.4) – Page 3 8. New PLD Design – Step 3 of 3: a. For this example we will program a simple OR GATE. Select: “Uncheck all” and then individually select the desired connectors. Use BTN0, BTN1, and LED0. Select: Finish. 9. The CDS will open a sheet in PLD mode with two port connectors on the left (the buttons) and one on the right (the LED). It is possible to change the port connectors after closing the PLD wizard. 10. To remove a port connector, simply delete it. 11. To add a port connector, select Place → Connector. Then choose the appropriate connector for the design. 12. Port connector names and functions (Mode) can be changed by right-clicking a connector and choosing Properties. The error that follows a change can be ignored by selecting YES. © 2014 Project Lead The Way, Inc. Activity 2.4.2 Introduction to Programmable Logic Devices: Programming Tutorial (DLB/Xilinx 12.4) – Page 4 Part 2: Simulating a PLD Mode Design in the CDS (Multisim) 13. The PLD design mode possesses a different list of components; the components from one mode do not work in the other. You can however use the simulation feature within PLD Mode to test whether the circuit is working before programming the DLB. 14. Components are found and placed in PLD Mode the same way they were in Design Mode. The PLD logic components available are generic and therefore do not have part numbers. 15. To place an OR gate: Select: PLD Logic → OR2 16. To place inputs for simulation: Select: Sources → INTERACTIVE_DIGITAL_CONSTANT. 17. To place an output for simulation: Select: Indicators → Probe 18. Save the circuit to the Tutorial project folder you created. Select: Simulation switch to run the simulation and test the circuit before exporting it to the PLD. © 2014 Project Lead The Way, Inc. Activity 2.4.2 Introduction to Programmable Logic Devices: Programming Tutorial (DLB/Xilinx 12.4) – Page 5 Part 3: Exporting the Design to the PLD Module. 19. Your DLB should be connected via USB to the computer and power supplied to it. 20. Having verified your gate is working Select: Transfer → Export to PLD. As long as there are no errors, this will open the PLD Export dialog box. 21. PLD Export – Step 1 of 2 Select: Program the connected PLD. The save box should have a check mark in it. Select: Next © 2014 Project Lead The Way, Inc. Activity 2.4.2 Introduction to Programmable Logic Devices: Programming Tutorial (DLB/Xilinx 12.4) – Page 6 22. PLD Export – Step 2 of 2 Xilinx tool: a. Under the Xilinx tool drop down menu Select: Xilinx ISE Design Suite 12.4 32-Bit or Xilinx ISE Design Suite 12.4 64-Bit Programming file: Select: Browse. Set your location for the programming file if you are not already there. PLD part number: The PLD part number will auto-populate. Advance settings: Xilinx user constraint files (*.ufc): Under the advanced settings select the button on the right side “three dot box” of the Xilinx user constraint files row and set path to C:\Program Files\National Instruments\Circuit Design Suite 12.0\pldconfig Select: “DEFB.ufc” from pldconfig folder. Select: Open Allow unmatched LOC constraints: Yes. Select: Finish 23. If errors occur, tell your teacher so that steps can be taken to check for proper installation of driver, Multisim, and Xilinx software.If the device is not found: a. check that the USB cable is connected. b. check user constraint path under PLD export Step 2. c. check the Xilinx tool path under Global Settings. d. check your Device Manager to see if “Digilent USB Device” is found. 24. Exporting to the PLD will take several minutes. Test the OR GATE on the PLD. © 2014 Project Lead The Way, Inc. Activity 2.4.2 Introduction to Programmable Logic Devices: Programming Tutorial (DLB/Xilinx 12.4) – Page 7 Classrooms Using Both Hardware Platforms (DMS and DLB) If your classroom is using both hardware platforms (The Digital MiniSystem and the Digital Logic Board), you will need to check that the CDS is pointing to the correct version of Xilinx, the correct drivers, and the correct user constraint file each time you “Transfer →Export to PLD”. The following is a summary of settings you should check if you are having trouble transferring the project to the PLD. If only using one hardware option you may disregard the optional information provided. Digital MiniSystem (DMS) Option Global Settings o Options → Global preferences → Paths → Miscellaneous → Xilinx tool path o C:\NIFPGA\programs\Xilinx14_4\ISE Transfer →Export to PLS Settings o Xilinx tool: “Xilinx ISE Design Suite 14.4 (32-bit or 64-bit) (Unsupported)” o Xilinx user constraint file: “Digilent C-mod S6.ucf” Digital Logic Board (DLB) Option Global Settings o Options → Global preferences → Paths → Miscellaneous → Xilinx tool path o C:\NIFPGA\programs\Xilinx12_4\ISE Transfer →Export to PLS Settings” o Xilinx tool: “Xilinx ISE Design Suite 12.4 (32-bit or 64-bit)” o Xilinx user constraint file: “DEFB.ucf” © 2014 Project Lead The Way, Inc. Activity 2.4.2 Introduction to Programmable Logic Devices: Programming Tutorial (DLB/Xilinx 12.4) – Page 8 Conclusion 1. Look up the names and definitions for the following programmable logic acronyms: a. PLD: b. PAL: c. GAL: d. CPLD: e. FPGA: 2. The evolution of programmable logic devices from the simple PALs of the late 1970s to the FPGAs of today is a classic example of Moore’s Law. What is Moore’s Law? © 2014 Project Lead The Way, Inc. Activity 2.4.2 Introduction to Programmable Logic Devices: Programming Tutorial (DLB/Xilinx 12.4) – Page 9