EDA\41_2_SSTA-

advertisement

STA with Variation

1

Corner Analysis

• PRCA (Process Corner Analysis):

Takes

1. nominal values of process parameters

2. and a delta for each parameter by which it varies.

Finds

− performance as max and min values.

•

Δ = 3σ

Pros:

Simple

•

Cons:

Conservative

Inaccurate

Inefficient: Not practical for many parameters

2

Corner Analysis: Conservative & Inaccurate

H

Hmax

M3

H Cg

T

W

M2

Tmin

Cg

M1

T

Tmax

Hmin

W

Wmin

Wmax

• PRCA shortcoming:

Process corners are assumed to coincide with performance

corners.

− Fact: best/worst-case corner may not depend on Pmin or Pmax for a particular

interconnect parameter but on a value within that range.

3

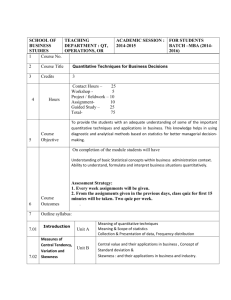

Corner Analysis: Conservative & Inaccurate

Parameter

Delay Impact

Metal (mistrack, thin/thick track)

-10% to +25%

Environmental (IR drop,

temperature)

+25%

Vth, tox

±5%

PLL (jitter, duty cycle, phase error)

±10%

N/P mistrack

±10%

-35% to 75% impact on delay?!

• Pessimistic Analysis:

Design that operates faster than necessary but high

power consumption

4

Corner Analysis: Inefficient

• Inefficient / impractical (if you want to be exact):

Needs 2n STAs / corner files

− n: # of sources of variations

− 27 to 220 analyses in practice

Has long been done for inter-die variations

− Small # of corner files

5

Corner Analysis: Inaccurate

• Inaccurate:

Cannot provide design sensitivity to different process

parameters

− Useful for robust design (i.t.o. timing yield)

6

Solution: SSTA

• SSTA:

Allows to compute the probability distribution of the

design slack in a single analysis.

-

If (timing constraint - delaycritical_path) > 200 ps yield ≈ 100%

If (delaycritical_path - timing constraint) > 300ps yield ≈ 0

Can adjust yield during design process

8

Impact of Variation

• Importance of variation:

Timing violations

− Yield loss

9

Impact of Variation

• Process variations can cause

up to 2000% variation in leakage current and

30% variation in frequency in 180nm CMOS

− Borkar, S., Karnik, T., Narenda, S., Tschanz, J., Keshavarzi, A., De, V.

Parameter Variations and Impact on Circuits and Microarchitecture. In

Proc. of DAC (2003), 338-342.

10

Impact of Variation

Die-to-die frequency variation

11

Statistical Description

The combined set of underlying deterministic and

random contributions are lumped into a combined

“random” statistical description.

12

Variation Parameter

• Parameters treated as Random Variables (RV)

Pi: a structural or electrical parameter e.g.

−

−

−

−

−

−

W,

tox,

Vth,

channel mobility,

coupling capacitances,

line resistances.

• Delay of each edge: a function of Pi’s

Delay: an RV too

13

Timing Graph

• Timing Graph:

G = {N, E, ns, nf } (directed)

ns: source node

nf: sink node

N: nodes

E: edges

di: Edge weight: gate/interconnect delay

• Statistical timing graph:

A timing graph if ith edge weight di is an RV.

• Critical path delay:

Changes from one die to another is an RV

• SSTA must compute the characteristics of this RV

By computing its

− PDF: probability-distribution function or

− CDF: cumulative-distribution function

14

SSTA

• Environmental uncertainty (supply, temperature):

Modeled by worst case margins

• Process uncertainty:

Modeled statistically

15

CDF and PDF

Area under f(t) from 0 to t1:

Prob. that critical path delay is < t1

predicted

t1

t1

Prob. that the delay up to

this (output) node is t1

16

Normal Distribution

• Gaussian or Normal Distribution

17

Normal Distribution

99.7% to be exact

[Sill05]

18

New vs. Older Technology

• Increasing variation

Probability Distribution

Old

New

Delay

19

SSTA

Can compute µ and σ

CDF and PDF can be derived from one another

• Given:

CDF of circuit delay and

required performance constraint

• Can compute

anticipated yield

• Given

CDF of the circuit delay and

required yield

• Can compute

maximum frequency at which the set of yielding chips

can be operated

20

SSTA

• SSTA problem definition:

path pi

− a set of ordered edges from source to sink in G

Di:

− path-length distribution of pi, computed as the sum of the

weights d for all edges k on the path.

SSTA finds distribution of

− Dmax = max(D1, . . . , Di, . . . , Dnpaths) among all paths

• Motivated from PERT in project management:

PERT: Project Evaluation and Review Technique

21

Sequential Paths

Tpath = t0+t1+t2+t3+…t(n-1)

• ti for n random variables:

ti = (µ, s)

Assume: independent delays

• Path delay RV:

Tpath = (n×µ, s × √n)

…

22

Sequential Paths

• 3 sigma delay on path:

Statistical:

n×µ + 3n × s

Worst case:

n×(µ+3 s)

Overestimate n vs. n

…

23

Parallel Paths

Tcycle = max(tp0, tp1, , tp(n-1))

T0 = Timing wall

P(Tcycle<T0) = P(tp0<T0)×P(tp1<T0)… = [P(tp<T0)]n

− Assuming: probabilities are equal

• For 50% reliability (Yield > 50%):

0.5 = [P(tp<T50)]n

P(tp<T50) = (0.5)(1/n)

24

SSTA Challenges (*)

• Challenges:

Topological correlation

Spatial correlation

Non-normal process parameters and non-linear delay

models

Skewness due to max operation

26

Topological Correlation (*)

• Reconvergent path

P1 and P2 share g0 edge and reconverge at g3 output

node (r)

27

Topological Correlation (*)

• Topological correlation between the arrival times:

Input arrival times at the reconvergent node become

dependent on each other

RVs are not independent

Complicates the max operation at the reconvergent

node

28

Spatial Correlation (*)

For P1 and P3 (no edges shared) if gates g1 and g2

are close on the die,

Correlation between the two path delays

−With SC:

− Leff,

− Temperature

− Supply voltage

−No SC:

− tox,

− Na

Affects both sum and max

29

Correlation (*)

Gate B delay

Gate B delay

Gate A delay

Correlated

Gate A delay

Uncorrelated

30

Systematic (Correlated Random)

WID Variation (*)

• Sample 1

• Sample 2

• Sample 3

• Models distance-dependent smooth variations

• Exact shape is unknown

[Samaan, ICCAD 04]

31

Non-Normal Process Parameters (*)

• Gaussian distribution:

Most commonly observed distributions for RVs

A number of elegant results exist for them

Most of work for SSTA assumed normal dist. For

− physical/electrical device parameters

− gate delays

− arrival times

• Problem:

Some physical device parameters may be significantly

non-normal:

− e.g. CD

32

Non-Normal Process Parameters (*)

• CD distribution:

Negative skewness (long tail in –ve direction)

33

Non-Linearity

• Non-linear dependence:

Even if some parameters are normal, dependence of

electrical parameters (e.g. gate delays) on them may

be non-linear

− Non-normal delays

• Assumption of initial work:

Linear dependence of gate delay on physical

parameters

− OK for small variations

− Recent papers address this issue

34

Skewness Due to Max

• Max operation is inherently non-linear

Max of two normal RVs is not normal

− Typically positively skewed

Non-normal arrival time at one node is the input to max

computation at down stream nodes

Need max operation of non-normal arrival times

• Most of the existing approaches assume normal

arrival times

36

Skewness of Max

Error of non-normal is large when similar µ but very different σ

− i.e. inputs of a gate have nominally balanced path delays but one path

has a tighter delay distribution (e.g. passing from less number of gates)

For delay values < mean, A dominates

For delay values > mean, B dominates

37

Skewness of Max

Small skewness if similar µ and σ

38

Skewness of Max

If very different µ, the bigger dominates

39

References (*)

• [Blaauw08] Blaauw, Chopra, Srivastava, Scheffer, “Statistical

Timing Analysis: From Basic Principles to State of the Art,” IEEE

Transactions on CAD, Vol. 27, No. 4, April 2008.

• [Forzan09] Forzan, Pandini, “Statistical static timing analysis: A

survey,” Integration, the VLSI journal, 42, 2009.

• [Sill05] F. Sill, “Statistical Static Timing Analysis and Statistical

Static Timing Analysis and Modeling of Parameter Variations,”

Lecture Slides, 2005

• [Sinha07] D.Sinha,H.Zhou,N.V.Shenoy, “Advances in

computation of the maximum of a set of Gaussian random

variables,” IEEE Trans. Computer-Aided Design 26

(2007)1522–1533.

40

References

• [Agarwal03a] A. Agarwal, D. Blaauw, and V. Zolotov, “Statistical

timing analysis for intra-die process variations with spatial

correlations,” in Proc. ICCAD,2003, pp. 900–907.

• [Agarwal03b] A. Agarwal, V. Zolotov, and D. Blaauw, “Statistical

timing analysis using Bounds and Selective Enumeration,”

TCAD 2003, pp. 1243–1260.

• [Chang03] H. Chang and S. Sapatnekar, “Statistical timing

analysis considering spatial correlations using a single PERTlike traversal,” in Proc. ICCAD, 2003, pp. 621–625.

41