LOW NOISE AMPLIFIER FOR AN ELECTRO-CARDIOGRAM

INTEGRATED CIRCUIT ANALOG FRONT END

A Project

Presented to the faculty of the Department of Electrical and Electronic Engineering

California State University, Sacramento

Submitted in partial satisfaction of

the requirements for the degree of

MASTER OF SCIENCE

in

Electrical and Electronic Engineering

by

Dhruval Patel

SUMMER

2013

© 2013

Dhruval Patel

ALL RIGHTS RESERVED

ii

LOW NOISE AMPLIFIER FOR AN ELECTRO-CARDIOGRAM

INTEGRATED CIRCUIT ANALOG FRONT END

A Project

by

Dhruval Patel

Approved by:

______________________________, Committee Chair

Perry L. Heedley, Ph.D.

__________________________________, Second Reader

Thomas W. Matthews, Ph.D.

Date

iii

Student: Dhruval Patel

I certify that this student has met the requirements for format contained in the University

format manual, and that this project is suitable for shelving in the Library and credit is to

be awarded for the project.

, Graduate Coordinator

Preetham B. Kumar, Ph.D.

Date

Department of Electrical and Electronic Engineering

iv

Abstract

of

LOW NOISE AMPLIFIER FOR AN ELECTRO-CARDIOGRAM

INTEGRATED CIRCUIT ANALOG FRONT END

by

Dhruval Patel

An electrocardiogram is a measurement of the signal due to the electrical activity

of the heart. This signal contains a great deal of useful diagnostic information. This

project explores the needs of key circuit blocks in an integrated circuit analog front end

for electro-cardiogram applications. Specifically, it is concerned with the design of the

low noise amplifier and includes a brief explanation of the circuit, trade-offs that should

be considered, and key decisions that must be made to meet critical specifications.

Simulations of a proposed circuit design were performed to compare the

performance achieved with a given set of specifications using worst-case variations for

process, supply voltage and temperature. A summary shows the final values achieved for

all specifications, and conclusions and recommendations are discussed.

, Committee Chair

Perry L. Heedley, Ph.D.

Date

v

TABLE OF CONTENTS

Page

List of Tables .................................................................................................................... vii

List of Figures .................................................................................................................. viii

Chapter

1. INTRODUCTION .........................................................................................................1

1.1

1.2

Background ......................................................................................................1

1.1.1

Signal Characteristics ...........................................................................1

1.1.2

Types of ECG Systems.........................................................................3

1.1.3

Analog Front End (AFE) ......................................................................3

Analog Front End .............................................................................................4

1.2.1

Low Noise Amplifier (LNA) ................................................................5

1.2.2

High Pass Filter (HPF), and Low Pass Filter (LPF) .............................5

1.2.3

Variable Gain Amplifier (VGA) ..........................................................6

1.2.4

Successive Approximation Analog to Digital Converter

(SAR-ADC) ..........................................................................................6

2. DESIGN OF THE LOW NOISE AMPLIFIER .............................................................8

2.1

Circuit Description ..........................................................................................8

3. SIMULATION OF THE LOW NOISE AMPLIFIER .................................................14

3.1

Waveforms .....................................................................................................14

3.2

Results ............................................................................................................19

4. CONCLUSIONS AND RECOMMENDATIONS ......................................................20

References ..........................................................................................................................21

vi

LIST OF TABLES

Tables

1.

Page

Table 3.1 Simulation Results .................................................................................19

vii

LIST OF FIGURES

Figures

Page

1.

Figure 1.1. Example Cardiogram .............................................................................2

2.

Figure 1.2 Block Diagram for the AFE ...................................................................4

3.

Figure 2.1 Low Noise Amplifier Circuit................................................................10

4.

Figure 2.2 Common Mode Feedback Circuit ........................................................11

5.

Figure 3.1 Closed loop transient response for a sine wave input...........................15

6.

Figure 3.2 Closed loop AC response .....................................................................16

7.

Figure 3.3 Open loop AC response ........................................................................17

8.

Figure 3.4 FFT Analysis ........................................................................................18

viii

1

Chapter 1

INTRODUCTION

1.1 Background

The use of integrated circuits for biomedical applications is increasing. One

important application is the measurement of the electrocardiogram (ECG), which is a

signal due to the electrical activity of the heart. Such use of integrated circuitry can result

in increased precision as well as making the measurement process easier. This report

presents an integrated low-noise analog front end for ECS measurements.

1.1.1

Signal Characteristics

The first step in learning the requirements for any biomedical instrument is to

learn about the signal to be sensed. The subject of this report is an amplifier for the ECG

signal. An example of an ECG signal is shown in Figure 1.1. There are many important

aspects to the actual signal, as can be seen in the figure. To differentiate them, each

interval is named specifically by the medical community using two or more letters to

identify each interval, such as the PR Interval, QRS Complex, QT Interval, etc. Each part

of the signal provides different information about the condition of the heart.

2

Figure 1.1. Example Cardiogram [8]

The peaks of the QRS complex are different for each individual. Depending on

the measurement conditions the value of this peak varies between +/- 1 mV to +/- 20 mV,

which is relatively small compared to the signals in most electronic devices today.

Therefore, designing a circuit to measure such small signals presents a unique set of

challenges.

3

1.1.2

Types of ECG Systems

Currently, two kinds of ECG systems are available; one is for the consumer, and

the other is for health care professionals. The first one is used for measuring the number

of heartbeats in a minute called BPM, or beats per minute. This type of instrument is

only concerned with the QRS complex (see Figure 1.1) rather than details for the other

intervals. The second instrument is used by health care professionals to obtain high

resolution waveforms, which can be used to precisely measure every detail of the ECG

signal even for the smallest parts of the signal. Such precision is required when a doctor

wants to check the condition of a patient’s heart, not just the BPM. The task for this

project was to design for the first type of ECG, so less stringent specifications were

required for the circuits used.

1.1.3

Analog Front End (AFE)

Real world signals are analog in nature, meaning that they are continuous in both

time and value with an infinite number of possible values. If we want to analyze a signal

on a digital device, we have to limit the number of samples of the waveform we use since

we cannot represent an infinite number of values in any digital system. For that, we must

convert the analog signal to a digital representation before we can input the signal to a

digital instrument. This requires an analog-to-digital converter (ADC), as well as several

additional gain and filtering functions which condition the signal before it is converted to

digital form. For the BPM application, five circuit blocks are required to properly

4

condition the signal. Together these circuits are called the “analog front end” or AFE.

The functions provided by each block in the AFE are explained in the following section.

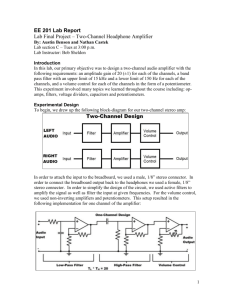

1.2 Analog Front End

Low

Noise

Amplifier

High

Pass

Filter

Variable

Gain

Amplifier

Low

Pass

Filter

Successive

Approximation

ADC

Figure 1.2 Block Diagram for the AFE

The Analog Front End (AFE) of an ECG is made up of five major blocks, as

shown in Figure 1.2. As a whole, we want a digital representation of the analog ECG

signal at the output. A brief explanation of each block is included in the following to

assist with understanding its contribution to the overall system.

5

1.2.1

Low Noise Amplifier (LNA)

Before we can understand the significance of the low noise amplifier, it is

worthwhile to ask a question: Why is it that we cannot use a standard operational

amplifier at the input of an ECG system? As we know, the input signal is very small, so

any noise becomes significant. So while a simple operational amplifier could be used to

amplify the input it would add too much noise to the signal. To reduce the amount of

noise added by the amplifier while maintaining enough gain requires a special kind of

amplifier, a low noise amplifier. So, the purpose of a LNA in an ECG system is to

amplify the input signal while adding an insignificant amount of noise to the system. In

addition, the LNA used for ECG applications must have an extremely high CMRR

(common-mode rejection ratio), on the order of 100dB or higher. This is necessary to

reject the 60Hz interference which is typically picked up by the wires used to connect the

instrument to the patient.

1.2.2 High Pass Filter (HPF), and Low Pass Filter (LPF)

In general, filters are used to remove unwanted signal frequencies. This ensures

inclusion of only the frequency range of interest. Limiting the bandwidth used also has

the desirable effect of minimizing the amount of noise added to the signal.

For the ECG signal, the frequency range is 0.1Hz to 200Hz. As the name

suggests, a high pass filter passes higher frequencies, so in this application a high pass

filter is used to remove frequencies below 0.1Hz. In addition, a low pass filter is used to

6

remove frequencies greater than 200Hz. As a result, the signal input to the ADC is

limited to the range of 0.1Hz to 200 Hz.

1.2.3 Variable Gain Amplifier (VGA)

As mentioned before, the amplitude of the heartbeat signal detected varies greatly

depending on the measurement conditions. So the question becomes, how do we amplify

that signal to fill the full scale input of an analog to digital converter (ADC), without

clipping the signal by amplifying it too much? The answer is a variable gain amplifier

(VGA). This amplifier provides a set of closed loop gains, and the needed amount of

gain is selected depending on the current signal strength. Typical gains provided range

from 2 to 20. This allows the input signal to the ADC to have nearly the same amplitude

each time. For example, if the input to the VGA is 100 mV in one case, and a gain of 4 is

selected, then the output of VGA will be 400 mV. In another case, if the input is 25 mV,

and a gain of 16 is selected, the output will again be 400 mV. Therefore even though we

have different input signals, we can apply the same input amplitude to the ADC.

1.2.4 Successive Approximation Analog to Digital Converter (SAR-ADC)

All signals in the real world are analog, and vary continuously in both time and

amplitude with an infinite number of possible values. However, most of the time digital

systems are used for data analysis, for example to analyze ECG data by inputting the data

into a computer or other digital analysis system. This leads to the need for an electronic

circuit that will convert the analog signal at the input to a digital representation. That

kind of circuit is called an analog to digital converter (ADC). For ECG applications

7

Successive Approximation ADCs are often used since they provide enough speed and

resolution while using only small amounts of power and area on the integrated circuit.

8

Chapter 2

DESIGN OF THE LOW NOISE AMPLIFIER

2.1 Circuit Description

This section will describe the operation of the low noise amplifier selected for this

design, which is shown in Figure 2.1 [12]. The common-mode feedback circuit used

with this amplifier is shown in Figure 2.2. Closed loop gain is one of the key parameters

for any amplifier. This is usually set by a ratio of resistors in feedback around an

amplifier.

However, in this circuit the feedback resistors are included inside the

amplifier. Notice the two components RS and RF in Figure 2.1. These resistors act as

the input and feedback resistors, respectively. The ratio of the values of RF to RS defines

the closed loop gain, which is 48000/2400 = 20 in this case. The equation for the

AOL

resultant closed loop gain is ACL= 1+AOL/ACLR , where ACL is the closed loop gain,

AOL is the open loop gain, and ACLR is the resistor ratio. From this equation we can

see that, the higher the open loop gain, the closer the closed loop gain will be to the

resistor ratio. Simulation results for both the open loop and closed loop gains are shown

in Chapter 3.

As shown in Figure 2.1, there are four transistors stacked in each input leg. M1

and M4 form the differential pair where the input signal is applied, while M2 and M5

form a second differential pair where feedback from the output is applied. Stacking these

two differential pairs provides a very high CMRR. They are based by the tail current

sources provided by M3 and M6. The diode connected transistors M7 and M8 act as the

9

load devices for the first stage, and are also the inputs to the current mirrors formed by

M8, M9 and M7, M10. The overall typology forms a current mirror amplifier. To keep

the input transistors in saturation, we need a higher common mode input voltage, which is

achieved by adding the source follower transistors, M13 and M16, before the input

differential pair. The bias current in the two input legs was chosen to be high enough so

even after signal current is steered through the resistors, enough bias current is left to

keep the two differential pairs (M1, M4 and M2, M5) turned on and operating in

saturation.

Figure 2.1 Low Noise Amplifier Circuit.

10

11

Figure 2.2 Common Mode Feedback Circuit.

High common mode rejection ratio (CMRR) is also a key specification for this

application. The equation for this is CMRR=

|ADM|

|ACM|

, where ADM is the differential gain,

and ACM is the common mode gain. From this equation we can see that to get a high

CMRR, we either need a high differential gain, or a low common mode gain, or both.

The usual way to achieve a low common mode gain is to use a tail current source with

high output resistance to bias the input differential pair. For this circuit, the second

differential pair (M2, M5) used for feedback acts as cascade devices for the tail current

sources (M3, M6). So, this circuit has a much higher CMRR compared to one without a

cascoded tail current source. In addition, long channel lengths were chosen for these

12

devices to help increase the resistance of the tail current source, and thus the CMRR.

Together, this allowed a CMRR of nearly 100dB to be achieved, as shown in Table 3.1.

Meeting the noise specification was the most challenging part of this LNA design.

Since this circuit is used for a low frequency (0.1 Hz to 200 Hz) application, the

dominant part of the noise is from 1/frequency noise in the MOSFETs. As the name

suggests, noise is inversely proportional to frequency, so the lower the frequency, the

greater the noise.

Another type of noise, called white noise, which is directly

proportional to resistance and frequency must also be considered.

However the

contribution from white noise was not significant due to the low bandwidth used in this

application of only 199.9 Hz (200 Hz – 0.1 Hz). However, choosing resistance values

represents a trade off. Clearly, reducing the value of RS and RF while maintaining the

desired ratio of 20 to 1 would reduce the noise contributed by these resistors. But

reducing the value of these resistors would also reduce the Gm*RS of the devices in the

differential pairs, which would lower the accuracy of the closed loop gain.

Also,

reducing these resistor values too much would cause difficulties in the layout for

resistance matching. So there is a trade off. Since the noise contributed by these resistors

was not significant compared to the 1/f noise contributed by the MOSFETs, the values

chosen here were acceptable.

Stability is another key factor for a negative feedback circuit. Since this circuit is

basically a current mirror amplifier, it has the dominant pole at the output, and the second

pole at the gates of the diode connected FETs, M7 and M8. The dominant pole sets the

unity gain frequency, while the second pole limits how high the unity gain frequency can

13

be while still achieving a reasonable phase margin. For this application, high bandwidth

is not a requirement, but achieving enough phase margin for good stability is. This is

limited by the second pole frequency. Notice that the current mirror ratio used in this

design is only ¼ between M7, M10 and M8, M9. Usually a current mirror ratio greater

than one is used to increase the open loop gain. Here, to achieve a good phase margin,

the second pole frequency had to be increased. To make that happen, the capacitance at

the gates of M7 and M8 needed to decrease. So to achieve a good phase margin while

not increasing noise, the current mirror ratio was chosen to be less than one. Stability

results are shown in Chapter 3.

14

Chapter 3

SIMULATION OF THE LOW NOISE AMPLIFIER

All simulations shown here were run with a worst-case process variations, high

temperature and low supply voltages.

3.1 Waveforms

Figure 3.1 shows the results of a transient simulation with an input sine wave,

which was used to determine the closed loop response. Figure 3.2 shows the closed loop

AC response. Figure 3.3 shows the open loop AC response which achieved an open loop

gain of 40.86 dB and a phase margin of 70.91 degrees. Figure 3.4 shows the results from

an FFT analysis, which achieved an ENOB (Effective Number Of Bits) of slightly over 9

bits which is sufficient for this application. An AC simulation of the noise performance

was also performed to determine the input referred noise. The result was 5.86uV/sqrt Hz,

as shown in Table 3.1

.

350.0M

V(VIDM)

V(VODM)

300.0M

250.0M

200.0M

Peak

Peak: 596.74

: 596.74

PeakTo

To Peak

MVMV

150.0M

100.0M

Voltage (V)

50.0M

Peak

To Peak : 40 MV

Peak To Peak : 40.000 MV

0.0M

-50.0M

-100.0M

-150.0M

-200.0M

-250.0M

-300.0M

-350.0M

0.0M

0.2M

0.4M

0.6M

0.8M

1.0M

1.2M

1.4M

1.6M

1.8M

2.0M

Time (s)

Figure 3.1 Closed loop transient response for a sine wave input.

15

30.0

db(VODM)

23.49486

23.4948

6

20.0

10.0

0.0

Magnitude (dB)

-10.0

-20.0

-30.0

-40.0

-50.0

-60.0

20.0

cphase(VODM)

-0.00207

0.0

-20.0

-40.0

-60.0

-80.0

Phase (degrees)

-100.0

-120.0

-140.0

-160.0

-180.0

-200.0

-220.0

-240.0

-260.0

1.0e-1

2

3

C1:

3.65041e-1

C1:

4 53.56041e-1

6

1.0e+0

2

3

4

5 6

1.0e+1

2

3

4

5 6

1.0e+2

2

3

4

5 6

1.0e+3

2

3

4

5 6

1.0e+4

2

3

4

5 6

1.0e+5

2

3

4 5 6

1.0e+6

2

3

4

5 6

1.0e+7

Frequency (Hz)

Figure 3.2 Closed loop AC response.

16

50.0

db(VODM)

40.85523

40.85523

40.0

30.0

20.0

10.0

0.00006

0.00006

Magnitude (dB)

0.0

-10.0

-20.0

-30.0

-40.0

-50.0

-60.0

20.0

cphase(VODM)

-0.01506

0.0

-20.0

-40.0

-60.0

-80.0

-109.09001

-109.09001

Phase (degrees)

-100.0

-120.0

-140.0

-160.0

-180.0

-200.0

-220.0

-240.0

-260.0

1.0e-1

2

3

C1:

4 53.56041e-1

6

1.0e+0

2

3

4

5 6

1.0e+1

2

3

4 5 6

1.0e+2

2

3

4

5 6

1.0e+3

2

3

4

5 6

1.0e+4

2

3

4

5 6

Frequency (Hz)

1.0e+5

2

3

4 5 6

1.0e+6

2

3

4

5 6

1.0e+7

C2:

1.45478e+5

= 1.45478e +2K)

C2: 1.45478e+5

(dx =(dx

1.45478e+2K)

Figure 3.3 Open loop response.

17

Figure 3.3 Open loop AC response.

17

18

Figure 3.4 FFT Analysis

19

3.2 Results

Table 3.1 Simulation Results

Specification

Achieved

Unit

Closed loop gain (ACL)

23.49

dB

Open loop gain (AOL)

40.86

dB

Phase margin (PM)

70.91

Degrees

Unity gain bandwidth (UGBW)

145.48

kHz

Common mode rejection ratio (CMRR)

97.94

dB

Input referred noise at 0.1 Hz (Vrms)

5.86

uV/sqrt Hz

Signal to noise ratio (SNR)

58.07

dB

Signal to distortion ratio (SDR)

62.56

dB

Signal to noise + distortion ratio (SNDR)

56.75

dB

20

Chapter 4

CONCLUSIONS AND RECOMMENDATIONS

In conclusion, the requirements for a low noise amplifier in an ECG analog front

end are very specific – achieve low noise, sufficient closed loop gain, and high common

mode rejection.

High bandwidth is not a key requirement in this design, and low

distortion is not difficult to achieve given the low output swing that is needed. Based on

the results discussed here, this design could be used as part of an analog front end for an

electro-cardiogram.

However, the low noise amplifier design shown in this project uses four

transistors stacked between the power supplies, so it requires a supply voltage of at least

3V to 5V to keep all four transistors in saturation. If a low noise amplifier in a recent

technology which uses a low supply voltage is needed, the use of other circuit topologies

should be considered.

21

REFERENCES

[1] Texas Instruments. [2012], “Low-power, 8-channel, 24-bit analog front-end for

biopotential measurements”, [Online]. Available: ADS1298/www.ti.com

[2] Enrique Company-Bosch and E. Hartmann. (n.d.). “ECG front-end design is

simplified with microconverter,” Analog Dialogue, November, 37-11. [Online].

Available: www.analog.com/analogdialogue

[3] Chinmayee Nanda et al., “1 V CMOS instrumentation, amplifier with high DC

electrode offset cancellation for ECG acquisition system,” Proceedings of the

Students’ Technology Symposium, 2010 IEEE, Kharagpur, India 2010, pp. 21-25.

[4] Robert Rieger. “Variable-gain, low noise amplification for sampling front end,” IEEE

Trans. Biomed. Eng., vol. 5, no. 3, pp. 253-261, Jun. 2011.

[5] James McKee et al., “Sigma-Delta analog-to-digital converters for ECG signal

acquisition,” 18th Annual International Conference of the IEEE Engineering in

Medicine and Biology Society, Amsterdam, Netherlands, 1996, pp. 19-20.

[6] Maximintegrated.com. [2010]. "Introduction to electrocardiographs”. [Online].

Available: http://www.maximintegrated.com/app-notes/index.mvp/id/4693

[7] Mentor Graphics. [2009]. Questa ADMS: analog-digital mixed-signal simulator

datasheet. [Online]. Available: www.mentor.com

[8] Were you wondering. [2009]. What does your heart do? [Online]. Available:

http://www.wereyouwondering.com/what-does-your-heart-do/

[9] Perry L. Heedley, EEE235 Lab documents, unpublished.

[10] Perry L. Heedley, EEE230 Class Notes, unpublished.

[11] Perry L. Heedley, EEE232 FFT Matlab Code, unpublished.

[12] Willy M. C. Sansen and Michel S. J. et al., “A micropower low-noise monolithic

instrumentation amplifier for medical purposes”, IEEE Journal of Solid-State

Circuits, vol. SC-22, no. 6, pp. 1163-1168, Dec. 1987.

[13] Chinmayee Nanda et al., “A CMOS instrumentation amplifier with low voltage and

low noise for portable ECG monitoring systems”. 2008 ICSE Proceedings, Johor

Bahru, Malaysia, pp. 54-58, 2008.

22

[14] Analog Devices, [2009], “Instrumentation amplifier (in-amp) basics,” pp. 1-5.

[15] Chia-Hao Hsu et al., “A high performance current-balancing instrumentation

amplifier for ECG monitoring systems”, ISOCC, 2009, pp. 83-86.

[16] Jack Li, “Thermal noise analysis in ECG applications,” Texas Instruments, 2011,

pp. 1-6.

[17] Texas Instruments, “Diagnostic, patient monitoring and therapy applications guide,”

2010, pp. 1-71.

[18] Venkatesh Acharya. “Improving common-mode rejection using the right-leg drive

amplifier,” Texas Instruments, 2011, pp. 1-11.