MSP430 Teaching Materials

UBI

Lecture 14

RF link using the eZ430-RF2500 &

Interrupts

Texas Instruments Incorporated

University of Beira Interior (PT)

Pedro Dinis Gaspar, António Espírito Santo, Bruno Ribeiro, Humberto Santos

University of Beira Interior, Electromechanical Engineering Department

www.msp430.ubi.pt

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

Contents (1/2)

UBI

RF Introduction

The application

The hardware

The software

Configuration

Algorithms

New challenges

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

2

Contents (2/2)

UBI

Interrupt Introduction

Interrupt: Processor's Perspective

Interrupt Service Routine

Some Common Questions

Interrupt Vector Table

Interrupt Latency

Sources of Interrupt Overhead

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

3

RF Introduction (1/3)

UBI

This laboratory demonstrates the operation of a small

wireless communication application;

The purpose of this laboratory is to send and receive text

messages, making use of RF links between the central

unit (base unit) and the various peripheral units (remote

units).

It is an integrated application, using some peripherals of

the MSP430, in particular, the USCIx communication

modules;

Additionally, it uses the CC2500 radio transceiver as an

interface to external devices;

Even though the application is simple, it is motivating to

the user because the IO console allows easy interaction

with the system;

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

4

RF Introduction (2/3)

UBI

This laboratory has the following objectives:

To demonstrate the importance of software organization as

a fundamental part of an embedded systems project:

• To approach the problem using a top-down approach,

applying the necessary abstraction to organize the

software into functional layers.

To give an example of the management of a complex

project, integrating together more than one functional

module:

• To develop a modular structure so that several functional

modules co-exist together within a single software

project.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

5

RF Introduction (3/3)

UBI

This laboratory has the following objectives (continued):

Make use of the wireless communications capability of the

MSP430, demonstrating its practical advantages;

Consolidate knowledge acquired during the previous

laboratories, namely:

• From the MSP430 communications interfaces laboratories:

– SPI mode to access the transceiver CC2500;

– UART mode to interface with the IO console.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

6

The application (1/2)

UBI

This laboratory establishes communications between

various RF units;

The stations are identified by an ID, i.e., the address for

presentation to the network. When a station wants to

communicate with another station, it must use the

address of the target station in the message;

The CC2500 has several ways to communicate, which

determine the size of the messages exchanged;

In order to simplify the communication process, fixedsize address and data have been used (maximum

message size 64 bytes). This corresponds to the size of

the CC2500 FIFO.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

7

The application (2/2)

UBI

CC2500 packages format:

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

8

The hardware (1/3)

UBI

The CC2500 is a radio frequency transceiver operating in

the widely used ISM/SRD (Industrial-Scientific-Medical

/Short-Range-Devices) 2.4 GHz frequency band;

It is a low-cost device with low power consumption,

designed for consumer electronics applications.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

9

The hardware (2/3)

UBI

The communications protocol uses very little data

formatting. It is up to the user to define the

communications protocol that best suits their application

and implement their own software;

The CC2500 is a low pin-out device, because it integrates

all the radio functions, except the antenna;

This device is not sufficiently independent that it can

operate without the aid of a microcontroller;

When coupled to the MSP430, connection is made

between:

• Access to internal registers: SPI interface belongs to the

USCIB0 unit;

• Status pins: GDO0 and GDO2 (P2.6 and P2.7).

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

10

The hardware (3/3)

UBI

CC250 RF transceiver:

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

11

The software (1/2)

UBI

Internal structure:

Structured in layers:

• Base layer: Hardware abstraction layer. Responsible for

separating the higher layers of software from the

hardware;

• Middle SPI layer: Ensures the communication functions

for the correct operation of CC2500;

• UART layer: Provides connection to the PC via RS232;

• CC2500 layer: Access and control functions controlling

the CC2500 (SPI and the GPIO);

• Application layer: Uses the features offered by layers at a

lower level to implement the tasks necessary for the

correct operation of the application.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

12

The software (2/2)

UBI

Software structure:

Application

CC2500

UART

SPI

Hardware Definition

CC2500 + SPI +UART

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

13

Configuration (1/3)

UBI

Clearly defined start-up of the multiple

modules and the various software modules;

hardware

Important: The unit’s address needs to be changed

during compilation, to allocate a unique address.

START

Configure MSP430 IO

Initialize MS430 Interface

Put CC2500 in RX state

Power-Up reset signal

sequence to CC2500

Set device Adress

Write RF Settings to

CC2500

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

Enter Sleep mode 3

14

Configuration (2/3)

UBI

Remote station code:

Composed of two interrupt

service routines (ISR) and

two buffers:

CC2500

RX Buffer

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

TX Buffer

Port2

Port1

RSI

ISR

Port1

Port2

RSI

ISR

UART

RS232

Keyboard

GPIO

TX

Switch

15

Configuration (3/3)

UBI

Remote station code:

• Port1 ISR:

– Enabled by the GDO0, which causes a L-H transition

when it receives a valid Sync_Word;

– H-L transition at the end of a message reception;

– Received message contents to IO console (RS232).

• Port2 ISR: Generated when the button is pressed,

sending the signal announcing the presence of the

remote station;

• Two buffers used to hold the messages:

– Transmit buffer is used to build the message for later

transmission;

– The receive buffer is used to hold the data read from

the CC2500 FIFO after receiving a message.

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

16

Algorithms (1/2)

UBI

Transmission algorithm implemented by Port2 ISR:

START ISR P1

Switch pressed?

Yes

Build a packet

Write data to TX buffer

No

Put CC2500 in TX state

Send

Packet

Wait forGDO0 to finish

Clear flag

END

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

17

Algorithms (2/2)

UBI

Reception algorithm used by the Port1 ISR in both

START ISR P2

stations:

Rx Buffer have

data

Yes

Read first byteof FIFO

(len byte)

No

Read len byte from FIFO

Read

packet

Read status byte

Clear flag

END

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

18

New challenges

UBI

The messages typed into the IO console for a particular

address would be sent by wireless support to the

console addressed.

To achieve this objective, it is useful to define a small set

of user-defined commands, such as:

• Address allocation at the local station;

• Address allocation at the remote station;

• Sending a message;

• Neighbourhood screening of possible talking partners;

• Among others…

>> Contents

Copyright 2009 Texas Instruments

All Rights Reserved

www.msp430.ubi.pt

19

Interrupt Introduction (1/3)

UBI

When MSP430 processor executes the following

code, it will loop forever;

Question: How can it execute other codes that handle

external events, e.g. I/O, timer?

StopWDT

SetupP1

Mainloop

Wait

L1

>> Contents

mov.w

bis.b

xor.b

mov.w

dec.w

jnz

jmp

#WDTPW+WDTHOLD,&WDTCTL

#001h,&P1DIR ; P1.0 output

#001h,&P1OUT ; Toggle P1.0

#050000,R15 ; Delay to R15

R15

; Decrement R15

L1

; Delay over?

Mainloop

; Again

20

Interrupt Introduction (2/3)

UBI

Option 1:

Put codes that handle external events in your main

program polling ;

StopWDT

SetupP1

Mainloop

Wait

L1

mov.w #WDTPW+WDTHOLD,&WDTCTL

bis.b #001h,&P1DIR ; P1.0 output

xor.b #001h,&P1OUT ; Toggle P1.0

mov.w #050000,R15 ; Delay to R15

dec.w R15

; Decrement R15

jnz

L1

; Delay over?

bit.b #B1,&P2IN

; Test bit P2IN

jnz ButtonUp

; Jump if not zero

bis.b #LED1,&P2OUT ; Turn LED1 on

ButtonUp: jmp

Mainloop

; Again

>> Contents

21

Interrupt Introduction (3/3)

UBI

Option 2:

Keep your program unchanged and force the processor

to jump to the code handling the external event when

that event occurs.

Requirements:

Must know when the event occurs;

Must let the processor know where to jump to execute

the handling code;

Must not allow your program know!!

you program must execute as if nothing happens;

Must store and restore your program state.

This is called interrupt!

>> Contents

22

Interrupt: Processor's Perspective (1/2)

UBI

Interrupts are triggered when certain events occur;

Usually done by sending a signal to one of the

processor’s IRQ (interrupt request) pins.

>> Contents

23

Interrupt: Processor's Perspective (2/2)

UBI

An interrupt signal stops processor at the next

instruction and the processor saves the address of

the next instruction on the stack;

Jumps to a specific interrupt service routine (ISR).

ISR is basically a subroutine to perform operations to

handle the interrupt with a RETURN at the end.

It is common to save the register contents onto the

stack (saving the state) and restoring them at the

end of the ISR (restoring the state).

>> Contents

24

Interrupt Service Routine (1/2)

UBI

The following shows an example of an ISR:

Task Code

...

MOVE R1, R7

MUL R1, 5

ADD R1, R2

DIV R1, 2

JCOND ZERO, END

SUBTRACT R1, R3

...

...

END: MOVE R7, R1

...

>> Contents

ISR

PUSH R1

PUSH R2

...

;ISR code comes here

...

POP R2

POP R1

RETURN

...

25

Interrupt Service Routine (2/2)

UBI

An ISR is like a subroutine, invoking similar

operations;

Subroutine:

Program has total control of when to call and jump to a

subroutine.

ISR:

Program is forced by hardware signals to jump to an ISR

at an unpredictable time, not by its control.

>> Contents

26

Disabling Interrupts

UBI

Programs may disable interrupts

In most cases the program can select which interrupts

to disable during critical operations and which to keep

enabled by writing corresponding values into a special

register;

Nonmaskable interrupts cannot be disabled and are used

to indicate power failures or serious event.

Certain processors assign priorities to interrupts

Allowing programs to specify a threshold priority;

Only interrupts having higher priorities than the

threshold are enabled and the ones below it are

disabled.

>> Contents

27

Where to Put ISR Code?

UBI

Challenges:

Locations of ISRs should be fixed so that the processor

can easily find them;

Different ISRs may have different lengths

Hard to track their starting addresses;

Application programs may supply their own ISRs; thus

ISR codes may change dynamically.

Possible solutions:

ISR is at a fixed location, e.g., in 8051, the first

interrupt pin always causes 8051 to jump to 0x0003;

A table in memory contains addresses of ISR

The table is called interrupt vector table.

>> Contents

28

How to Know Who Interrupts?

UBI

Simple answer: according to interrupt signal

One interrupt signal corresponds to one ISR;

Difficult problem: same interrupt signal shared by

several devices/events

Option 1: inside the corresponding ISR, poll and check

these devices/events in turn

Devices are passive;

Option 2: devices/events provide the address of ISRs

Devices are proactive;

Vectored interrupt.

>> Contents

29

Some Common Questions

UBI

Can a processor be interrupted in the middle of an

instruction?

Usually not;

Exceptions: critical hardware failure, long-running

instructions (e.g. moving data in memory).

If two interrupts occur at the same time, which ISR

does the process do first?

Prioritize the interrupt signals.

Can an interrupt signal interrupt another ISR?

Interrupt nesting usually allowed according to priority;

Some processor may require re-enabling by your ISR.

What happens when an interrupt is signaled while

the interrupt is disabled?

Processors usually remember the interrupt signals and

jump to the ISR when the interrupt is enabled.

>> Contents

30

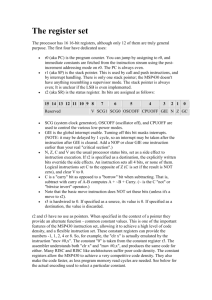

Interrupt Vector Table

UBI

Interrupt Source

Interrupt

Flag

System

Interrupt

Word Address

Priority

Power-up

External Reset

Watchdog Timer+

Flash key violation

PC out-of-range

PORIFG

RSTIFG

WDTIFG

KEYV

Reset

0FFFEh

31

(highest)

NMI

Oscillator Fault

Flash memory access violation

NMIIFG

OFIFG

ACCVIFG

Non-maskable

Non-maskable

Non-maskable

0FFFCh

30

0FFFAh

29

0FFF8h

28

0FFF6h

27

Watchdog Timer+

WDTIFG

maskable

0FFF4h

26

Timer_A2

TACCR0 CCIFG

maskable

0FFF2h

25

Timer_A2

TACCR1 CCIFG

TAIFG

maskable

0FFF0h

24

0FFEEh

23

0FFECh

22

ADC10

ADC10IFG

maskable

0FFEAh

21

USI

USIIFG

USISTTIFG

maskable

0FFE8h

20

I/O Port P2 (2)

P2IFG.6

P2IFG.7

maskable

0FFE6h

19

I/O Port P1 (8)

P1IFG.0 to

P1IFG.7

maskable

0FFE4h

18

0FFE2h

17

0FFE0h

16

0FFDEh to 0FFCDh

15 - 0

>> Contents

Unused

31

Interrupt Latency

UBI

Interrupt latency is the amount of time taken to

respond to an interrupt. It depends on:

Longest period during which the interrupt is disabled;

Time to execute ISRs of higher priority interrupts;

Time for processor to stop current execution, do the

necessary ‘bookkeeping’ and start executing the ISR;

Time taken for the ISR to save context and start

executing instructions that count as a ‘response’.

Make ISRs short

Factors 2 and 4 are controlled by writing efficient code

that are not too long;

Factor 3 depends on HW, not under software control.

>> Contents

32

Sources of Interrupt Overhead

UBI

Handler execution time

Interrupt mechanism overhead

Register save/restore

Pipeline-related penalties

Cache-related penalties

>> Contents

33