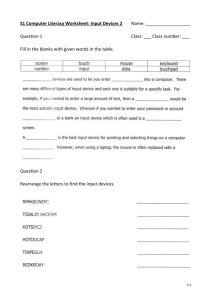

on I/O Devices

advertisement

COMP541

Input Devices: Keyboards,

Mice and Joysticks

Montek Singh

Nov 3, 2014

1

Keyboard Interface

USB keyboard plugs into the USB port

on Nexys 3 / Nexys 4 boards

USB to PS/2 emulation

Host controller on Nexys boards

talks to USB keyboard on one side

speaks PS/2 protocol to the FPGA on the other side

PS/2 used to be the dominant keyboard protocol

PS/2 = a synchronous serial protocol

What does that mean?

Each symbol is transmitted bit-by-bit

8 data bits + 3 control bits

synchronized to the keyboard’s clock (slow)

3

the COM port will produce serial data traffic on the

N17 and N18 FPGA pins.

Physical Interface

Micro-USB

FT232

Spartan 6

USB HID Host

Two lines

A Microchip PIC24FJ192

microcontroller provides the Nexys3

K_CLK

L12

PS/2 Keyboard

with

USB

H

ID

host

capability.

Clock (15-20KHz)

K_DAT

J13

rence Manual

Firmware in the microcontroller can

M_CLK

L13

drive a mouse or a keyboard attached

2

PS/2 Mouse

Data to the type A USB connector at J4

K14

M_DAT

labeledbe

"Host".

Hub support

is notthe PIC24 reads the GPIO0

files will automatically

rejected.

Note

FPGA's mode,

and

Additional

I/Odone

L16 init,

currently

available,

so only a single

Normally

high,

asserted

low

“HOST”J4

H17

GPIO1

n drive the PROG pin as a part of the programming

sequence.

(for future use)

mouse or a single keyboard can be

used. The PIC24 drives four signals

into the FPGA – two are used as a

keyboard port following the keyboard

PS/2 protocol, and two are used as a

mouse port following the mouse PS/2

protocol.

I

Read:

ler

pp. 13-14 of Nexys 3 manual

pg.controller,

10 of Nexys

4 manual

he USBhost

EDK designs

DIN

CLK

R13

R15

FPGA Serial

programming

PIC24FJ192

Spartan 6

Tck Tck

Two PoC24 I/O pins are also cnne cted to the

FPGA’s

the FPGA

Edge

0 two-wire serial programming port, soEdge

10

standard PS/2 core

(non-EDK designs

can be programmed from a file stored on a USB memory stick. To program the FPGA, attach a

memory

stick containing a single .bit programming file in the root directory, load both M0 and M1 on

mple state machine).

Reference

‘0’ will

start

bit the PIC processor to program

stop

J8 jumper, and cycle board power. This

cause

the FPGA,‘1’

and

any bit

Thld

ted on the Digilent website show an

502-182

page 12 of 22

reading charactersDoc:

from

a USB

Tsu

onnected to the USB host interface.

yboards that use the PS/2 protocol

ire serial bus (clock and data) to

e with a host device. Both use 11-bit

nclude a start, stop, and odd parity bit,

packets are organized differently, and

Symbol

Parameter

Min

Clock time

30us

TCK

Data-to-clock setup time 5us

TSU

THLD Clock-to-data hold time 5us

Max

50us

25us

25us

4

Protocol

Bidirectional

Kybd-to-host and host-to-kybd on same wires

CAPS LOCK light for example

Assert low

To send, keyboard starts clocking

sends successive bit on positive edge of clock

host reads bits on negative edges of clock

For your lab:

You shouldn’t need to send anything to keyboard

5

Protocol

11 bits

a start bit: always 0

8 bits of data

lsb first

one parity bit (odd)

a stop bit: always 1

Clocked by keyboard

Value should be latched by FPGA on neg edge of keyboard

clock

Illustration from http://www.beyondlogic.org/keyboard/keybrd.htm

6

What is Sent

ASCII is not sent!

Nexys3 Reference

Manualkeys

Scan codes

for

The keyboard can send data to the host only when both the data and clock lines are high (or idle).

Most

keys

an 8-bit

(single

scancode

Since

the hosthave

is the bus master,

the keyboard

must check byte)

to see whether

the host is sending data

before driving

s the bus. To facilitate this, the clock line is used a a “clear to send” signal. If the host pulls the

clock line

low, thebytes

keyboard must not send any data until the clock is released. The keyboard

Some

have

two

sends data to the host in 11-bit words that contain a ‘0’ start bit, followed by 8-bits of scan code (LSB

first), followed by an odd parity bit and terminated with a ‘1’ stop bit. The keyboard generates 11 clock A few

have

more!

transitions

(at 20 even

to 30KHz) when

the data is sent, and data is valid on the falling edge of the clock.

Scan

codes for

most be

PS/2 keys

are shown in the

figure below.

Most

(not

all,

careful!)

keyboards

use these scancodes:

ESC

76

`~

0E

1!

16

TAB

0D

Caps Lock

58

Shift

12

Ctrl

14

F1

05

F2

06

F3

04

F4

0C

2@

1E

3#

26

4$

25

5%

2E

Q

15

W

1D

A

1C

E

24

S

1B

Z

1Z

D

23

X

22

Alt

11

R

2D

F5

03

6^

36

T

2C

F

2B

C

21

F7

83

7&

3D

Y

35

G

34

V

2A

F6

0B

8*

3E

U

3C

H

33

B

32

9(

46

I

43

J

3B

N

31

F8

0A

M

3A

F9

01

0)

45

O

44

K

42

-_

4E

P

4D

L

4B

,<

41

F10

09

=+

55

[{

54

;:

4C

>.

49

Space

29

/?

4A

Alt

E0 11

F11

78

F12

07

E0 75

BackSpace

66

E0 74

]}

5B

'"

52

\|

5D

Enter

5A

E0 6B

E0 72

Shift

59

Ctrl

E0 14

PS/2 Keyboard Scan Codes

Mouse

Illustration from Nexys 3 manual

7

Scan Codes

Normally translated by software

You remap your keys, for example

Software takes care of

Shift, caps lock, control

8

Some Scan Codes Long

Two code sequence common

Some special keys use even more…

…have a look at Break key!

9

Even More Complicated

Scan code generated when you press

And when you release

Two bytes: F0 followed by key scan code

Example:

Space pressed, 29 sent

Space released, F0 29 sent

10

Resources

Information

http://www.beyondlogic.org/keyboard/keybrd.htm

Scan codes

http://www.barcodeman.com/altek/mule/scandoc.php

Available on the class website:

my Verilog for keyboard

11

My Verilog

Have Verilog for keyboard

a test/demo which displays data from keyboard onto 7segment display

have tested it with the FPGA kit; seems to work fine

To use:

You will memory-map the character code register

give the keyboard a memory address so the CPU can read it using

lw instructions

Handle presses and releases appropriately in software

Either: Check for a key release before reading a new key press

OR: Delaying next key read (by, say, 1/4th sec)

– gives you automatic “key repeat” feature!

12

Mice

13

Mouse

Very similar interface (clk & data)

But: 3 words sent w/ mouse movement or button press

Read

pp. 14-15 of Nexys 3 manual / pp. 12-13 of Nexys 4 manual

Verilog

I can guide you to modify keyboard.v to read 3 bytes

Nexys3 Reference Manual

Mouse status byte

1

0

L

R

0

Start bit

1 XS YS XY YY P

Stop bit

X direction byte

1

0

Y direction byte

X0 X1 X2 X3 X4 X5 X6 X7 P

Start bit

Stop bit

Idle state

VGA Port

1

0

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 P

Start bit

1

Stop bit

Idle state

Mouse Data Format

14

Movement

Movement is relative

XS, YS are sign (+ is up/right)

XY, YY are overflow (too fast)

L, R are buttons

Nexys3 Reference Manual

Mouse status byte

1

0

L

R

0

Start bit

1 XS YS XY YY P

Stop bit

X direction byte

1

0

Y direction byte

X0 X1 X2 X3 X4 X5 X6 X7 P

Start bit

Stop bit

Idle state

VGA Port

1

0

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 P

Start bit

1

Stop bit

Idle state

Mouse Data Format

15

Scroll Wheel, etc.

Extensions to original 2 button PS/2 mouse

See http://www.computer-engineering.org/ps2mouse/

16

Joystick

Joystick module

2 axes: x and y

10-bit position values

On-board microprocessor

handles debouncing

communicates with host

Info on class website

reference manual

Verilog code

demo: feeds joystick output to the 7seg display

you will modify to feed the output into

your memory-mapped I/O unit instead

18

Accelerometer

Nexys 4 boards have built-in accelerometer

For Nexys 3: read on…

19

Accelerometer module

3-axis accelerometer

x, y, z components of gravity

helps determine

orientation and acceleration

On-board microprocessor

communicates with host

Info on class website

reference manual

Verilog code

demo: feeds accelerometer

output to the 7-seg display

you will modify to feed the

output into your memorymapped I/O unit instead

20

Keypad

21

Keypad module

4x4 keypad

0-9, A-F

one hex character input

Simple interface

4-bit row, 4-bit column

a ‘0’ means pressed

Info on class website

reference manual

Verilog code

demo: feeds keypad output to

the 7-seg display

you will modify to feed the

output into your memorymapped I/O unit instead

22

Stereo Audio Amplifier

Nexys 4 has mono amplified built-in

Nexys 3/Nexys 4: you can attach a stereo module

(read on…)

23

Amplifier module

Stereo output

headphone jack compatible

Very very low-level…!

expects analog waveform on

input!

your design on FPGA will have

to generate an analog value

by rapidly toggling between 0 and 1

e.g., 60% of the time ‘1’ value will approximate an analog value of

0.60V (if range is 0-1V)

Verilog code

I will post mine on the website

24