Document

advertisement

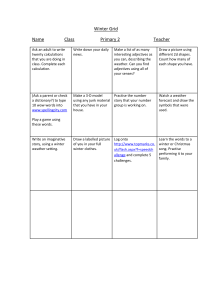

ENG6530/ENG3050

Reconfigurable Computing

Systems

General Information

Handout

Winter 2014, January 6th

Shawki Areibi

Office, Email, Phone

•

•

•

•

Office: 2335, EXT 53819

Email: sareibi@uoguelph.ca

Web: http://www.uoguelph.ca/~sareibi

Office Hour: Thursday 2:00 – 3:00

PhD, Waterloo 1995

Research Interests

• VLSI Physical Design Automation (CAD/EDA)

• Combinatorial Optimization (Heuristics/Meta-heuristics)

• Reconfigurable Computing Systems/Embedded Systems

2

RCS - Winter 2014

2

Outline

•

•

•

•

•

•

•

Staff (TA, Lab Tech)

Lecture Schedule

Course Text and References

Resources and Communication

Assignments, Paper Review, Project

Evaluation

Course contents, Tentative Schedule

3

3

RCS - Winter 2014

Lab Coordinator

• Nate Groendyk

• Lab#1 2307, Office 2308, ext 53873

• Lab#2 RICH 1532

• Email: groendyk@uoguelph.ca

4

RCS - Winter 2014

4

Teaching Assistant

• Ahmed Al-Wattar, PhD Student

• Research: Reconfigurable Computing

• TA for ENG2410, 2011, 2012, 2013

• Room THORN 2319, ext. 56493

• Email: aalwatta@uoguelph.ca

• Office Hour: Wed 3:30 – 4:30

5

5

RCS - Winter 2014

Lecture Schedule

Lectures 10:00 – 11:30 (Mon/Wed)

In MACN 118

Starting Next Lecture RICH 2531

Lab 3:30 – 5:30 (Monday)

In RICH 1532

6

6

RCS - Winter 2014

Text Book and References

Text Books & References

1.

“Reconfigurable Computing: The Theory and Practice of

FPGA-Based Computing”, Edited by S. Hauck, 2008.

2.

“Introduction to Reconfigurable Computing:

Architectures, Algorithms and Applications”, by C.Bobda

3.

“Reconfigurable Computing: Accelerating Computation

with FPGAs”, by Maya Gokhale

4.

“Computer Organization and Design”, by Patterson and

Hennessy

5.

“VHDL for Engineers”, by K. Short, 2009.

6.

“The Designer’s Guide to VHDL”, by Peter Ashenden

7

7

RCS - Winter 2014

Resources & Communication

http://www.uoguelph.ca/~sareibi

Communications

1.

2.

E-mail

ENG6530/ENG3050 Web Pages

Username:

Password:

8

8

RCS - Winter 2014

Prerequisites

Digital Design (ENG2410)

Computer Organization (ENG3380)

Basic knowledge of programming

languages (C, C++)

Basic Knowledge of Hardware

Description Languages (VHDL)

Experience in VLSI Design maybe

helpful but not required.

9

9

RCS - Winter 2014

Course Objectives

Achieves the following goals:

1.

Gives an overview of the traditional Von Neumann

Computer Architecture, its specifications, design and

implementations and main drawbacks. Techniques to improve

the performance.

2.

Teaches you the internal structure of Programmable Logic

in general and Field Programmable Gate Arrays in particular.

3.

Teaches you how digital circuits are designed today using

advanced CAD tools and HDLs and high level languages.

4.

Teaches you the basic concepts of Reconfigurable Computing

systems (Hardware/Software co-design)

5.

Teaches you when/how to apply Reconfigurable Computing

Concepts to design efficient, reliable, robust systems (DSP).

6.

Understand the concept of Run Time Reconfiguration.

10

10

RCS - Winter 2014

Evaluation “Graduate”

Topic

Weight

Details

Assignments

20%

Assignments

Paper Review

10%

See Web Page

Project

30%

See Web Page

Final Exam

40%

Closed Book Exam

11

11

RCS - Winter 2014

Evaluation “UnderGraduate”

Topic

Weight

Details

Assignments

20%

Assignments

Paper Review

10%

See Web Page

Labs

20%

See Web Page

Final Exam

50%

Closed Book Exam

12

12

RCS - Winter 2014

Paper Review

Each student (group) is assigned several

articles from journal papers/conferences.

Prepare a brief (20 minute) oral presentation

of the article or topic (objectives, methods,

results, contributions e.t.c.)

A Two page summary giving the citation and

the material in the oral presentation must be

written and a copy is distributed to each class

member.

13

13

RCS - Winter 2014

Paper Review: Topics

14

1.

Coarse Grained Reconfigurable Arrays

2.

Evolvable Hardware

3.

Floating Point vs. Fixed Point representations

4.

CAD for RCS (High Level Synthesis)

5.

Operating Systems for Reconfigurable Computing

6.

Electronic System Level: A comparison

7.

ASICs vs. FPGAs vs. ASIPs

8.

Run Time Reconfiguration: Challenges

9.

Others …

14

RCS - Winter 2014

Research Project

“Graduate Students” will select a topic related to

Reconfigurable Computing Systems.

You should conduct an in-depth study covering

the problem to be solved and its current status.

Your finding should be documented in a report

Introduction to the problem

Motivation

Background

Literature Review

Methodology

Results

Conclusion

15

15

RCS - Winter 2014

What is Reconfigurable

Computing?

Mapping algorithms traditionally running on general purpose

processors onto reconfigurable platforms to achieve better

performance.

Computation using hardware that can adapt at the logic level to solve

specific problems

Why is this interesting/important?

Some applications are poorly suited to General microprocessors.

VLSI “explosion” provides increasing resources.

Hardware/Software Co-design is main trend in Embedded Systems.

Accelerate scientific/industrial applications to achieve speedup (Real Time

performance is necessary!)

16

16

RCS - Winter 2014

Microprocessor-based Systems

Von-Neumann Architecture

Data Storage

(Register File)

A

B

C

ALU

64

Characteristics?

Generalized to perform many functions well.

Operates on fixed data sizes.

Instruction fetch, decode, execute Inherently sequential.

17

17

RCS - Winter 2014

Reconfigurable Computing

A

If (A > B) {

H = A;

L = B;

}

Else {

H = B;

L = A;

}

18

B

Functional

Unit

H

L

Create specialized hardware for each application.

Functional units optimized to perform a special task.

18

RCS - Winter 2014

Implementation Spectrum

Microprocessor

Reconfigurable

Hardware

ASIC

Characteristics?

ASIC gives high performance but is inflexible and expensive

Processor is very flexible but not tuned to the application.

Reconfigurable hardware is a nice compromise.

19

19

RCS - Winter 2014

Tentative Schedule

20

Topic

Topic

Topic

Topic

Topic

Topic

Topic

Topic

Topic

Topic

Topic

#1, Introduction to RCS

#2, Programmable Logic Devices

#3, CAD for RCS (FPGAs)

#4, VHDL

#5, High Level Languages (Handel-C)

#6, Reconfigurable Processors (ASIPs)

#7, Hardware/Software Co-design

#8, Run Time Reconfigurations

#9, Digital Signal Processing, Tools

#10, Design Exploration Techniques

#11, RCS Applications

RCS - Winter 2014

20

Topic #1: RCS, Introduction

Identify bottlenecks currently found in traditional Von

Neumann Architectures.

Learn new techniques to improve performance.

How/Why RCS can fill the gap between ASICs and

General Purpose Processors.

21

21

RCS - Winter 2014

Topic #1, Cont ..: Technology

Comparison

Technology

Performance

Cost

Power

Flexibility

Memory BW

I/O BW

GPP

LOW

LOW

HIGH

HIGH

LOW

LOW

PDSP

Medium

Medium

Medium

Medium

Medium

LOW

ASIC

HIGH

HIGH

LOW

LOW

HIGH

HIGH

FPGA

Med-High

LOWt

Low-Medium

HIGH

HIGH

HIGH

22

22

RCS - Winter 2014

Topic #2: Programmable Logic

Programmable

Or Array

Programmable

AND array

Programmable

AND array

Programmable

Or Array

23

23

RCS - Winter 2014

Topic #2 Cont … : FPGAs

Around the beginning of the 1980s, it became apparent that there

was a gap in the digital IC continuum.

At one end, there were programmable devices liks SPLDs and CPLDs,

which were highly configurable but could not support large designs.

At the other end of the spectrum were ASICs which can support

complex functions but were expensive, time consuming, ….

PLDs

SPLDs

ASICs

The

GAP

CPLDs

Gate Arrays

Structured ASICs*

Standard Cell

Full Custom

*Not available circa early 1980s

24

RCS - Winter 2014

24

Topic #3: CAD for Programmable Logic

Design

Entry

Placement

Routing

Synthesis

Packing LUTs

to CLBs

Simulation

Logic

Optimization

Mapping

to k-LUT

Configure an

FPGA

25

25

RCS - Winter 2014

Topic #3: FPGA Design Flow

Design Specification

Design Entry/RTL Coding

Behavioral or Structural Description of Design

RTL Simulation

• Functional Simulation

• Verify Logic Model & Data Flow

(No Timing Delays)

LE

MEM

Synthesis

I/O

• Translate Design into Device Specific Primitives

• Optimization to Meet Required Area & Performance

Constraints

Place & Route

• Map Primitives to Specific Locations inside

Target Technology with Reference to Area &

• Performance Constraints

• Specify Routing Resources to Be Used

26

26

RCS - Winter 2014

Topic #4: VHDL

External

Interface

circuit

A

B

Internal

Functionality

Outputs

Inputs

27

F

27

RCS - Winter 2014

Topic #4: Synthesizable VHDL

VHDL for Simulation

VHDL for Synthesis

VHDL for

Specification

VHDL for Synthesis

of Arithmetic Circuits

28

28

RCS - Winter 2014

Topic #5: Managing Complexity

ESL

29

29

RCS - Winter 2014

Topic #5: High Level Languages

Take an algorithm written in C.

Generate an efficient hardware design, run it on an FPGA.

Fast design cycle, easy to maintain code.

C programmers should be able to create fast hardware!

30

30

RCS - Winter 2014

Topic #6: ASIPs

An ASIP is a storedmemory CPU whose

architecture is tailored for

a particular set of

applications.

The instruction-sets tailored

to specific applications or

application domains

31

31

RCS - Winter 2014

Topic #7: Hardware/Software Co-design

Interface

process (a, b, c)

in port a, b;

out port c;

Partition

{

Model

read(a);

…

Capture

write(c);

}

Synthesize

Specification

Line ()

{

a=…

…

detach

}

FPGA

Processor

32

32

RCS - Winter 2014

Topic #8: RTR

FPGAs are classified as dynamically reconfigurable if their embedded

configuration storage circuitry and corresponding functions can be

updated without disturbing the operation of the remaining logic.

33

33

RCS - Winter 2014

Topic #8, Cont ..: Virtual Hardware

The concept of Run Time Reconfiguration on FPGAs is

similar to the concept of Virtual Memory on Computer

Systems.

Configuration data

stored in memory device

Function A

Unused resources

Active tasks

Inactive tasks

Function A

Function B

Function B

Function C

Overwrite function B

with new function C

34

34

RCS - Winter 2014

Topic#9: DSP

35

35

RCS - Winter 2014

Topic #9: DSP, Performance Gap

Algorithmic complexity increases as application demands

increase.

In order to process these new algorithms, higher performance

signal processing engines are required

36

36

RCS - Winter 2014

Topic #10: Design Exploration

Given an application (software implementation):

what is the most appropriate hardware components and communication links

that should be used?

The main challenge in DSE arises from the sheer size of the design space

that must be explored.

Typically, a large system has millions, if not billions, of possibilities, and

so enumerating every point in the design space is prohibitive.

37

37

RCS - Winter 2014

Topic #11: Applications

What applications require Hardware Acceleration?

Image processing, medical applications, real time …

Hardware Accelerators for CAD

Hardware Accelerators for ANNs

Hardware Accelerators for Communication Systems

38

38

RCS - Winter 2014

Satellite Imaging

•

•

•

Satellite imaging used for mapping, environmental studies

and defense applications

High-data rate and low-power demands of space require

cutting-edge technology such as RC to provide required

processing capabilities

Including RC devices in the processing chain will

eventually enhance performance

c/o US Air Force

c/o LANL

Receive

Cube

Pulse

Compression

Doppler

Processing

Space-Time

Adaptive

Processing

(STAP)

Constant

False Alarm

Rate

(CFAR)

c/o LANL

Send

Results

GMTI processing chain

Corner Turn

Partitioned along

range dimension

RCS - Winter 2014

Partitioned along

pulse dimension

39

fMRI and Real-time Human Body Imaging

• Technique for determining which parts of the brain are activated

by different types of physical sensation or activity – “brain

mapping”

• High- and low-resolution scans compared using numerous FFTs

– Typically post-processed

– Much error correction needed due to subject movement

– 3D data representation requires a good deal of conventional processing

• Studying how RC devices can achieve real-time processing

Figures c/o University of Oxford, UK

RCS - Winter 2014

40

41

41

RCS - Winter 2014