EKT 121 / 4 ELEKTRONIK DIGIT 1

EKT 221/4

DIGITAL ELECTRONICS

II

Registers, Micro-operations and Implementations

-Part3

Outlines

Multiplexer-based transfers

Transforming Block Diagram to Detailed Logic

Shift Registers

Shift Registers with Parallel Loads

Shift Registers with Parallel Loads and Hold

Bidirectional Shift Register

MUX-Based Transfer

Bus-Based Transfer

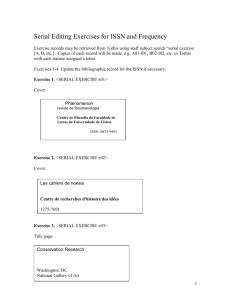

Serial Transfer and Micro-operations

Multiplexer-Based Transfers

A Register receives data transfers from more than 1 sources.

A dedicated multiplexer is used to select the wanted input

Example shows:

R0 receives data from

R1 if K1 is 1.

R0 receives data from

R2 if K1 is 0.

K2

R2

R1

K1 n=4 n=4

0

1

S

MUX n=4

R0

Multiplexer-Based Transfers

How do we represent this in RTL form?

Written in if-then-else:

If (K1=1) then (R0 R1) else if

(K2=1) then (R0 R2)

Written in RTL

K1:R0 R1, K1K2:R0 R2

K2

R2

R1

K1 n=4 n=4

0

1

S

MUX n=4

R0

Multiplexer-Based Transfers

K1:R0 R1, K1K2:R0 R2

Analyze the diagram for input:

K1 K2 Load

1

1

0

0

0

1

0

1

0

1

1

1

R0 content n.c

R2

R1

R1

K2

R2

R1

K1 n=4 n=4

0

1

S

MUX n=4

Load

R0

K2

R2

R1

K1 n=4

0

1

S

MUX n=4

Block Diagram n=4

Load

R0

Transforming a Block

Diagram into Detailed Logic

K2

K1

Load

D0

D1

D2

D3

R2

Q0

Q1

Q2

Q3

Load

CLK

D0

D1

D2

D3

R1

Q0

Q1

Q2

Q3

B0

B1

B2

B3

2 to 1 MUX

S

A0

A1

A2

A3

Y0

Y1

Y2

Y3

Detailed Logic

Load

D0

D1

D2

D3

R0

Q0

Q1

Q2

Q3

Shift Registers

Shift Registers move data laterally within the register toward its MSB or LSB position

In the simplest case, the shift register is simply a set of D flip-flops connected in a row like this:

Shift Registers

Parallel Output

Serial Input

Serial Output

Data input, In, is called a serial input or the shift right

input.

Data output, Out, is often called the serial output.

The vector (A, B, C, Out) is called the parallel output.

Shift Registers

• T0 is the register state just before the first clock pulse occurs

• T1 is after the first pulse and before the second.

• Initially unknown states are denoted by “?”

• Complete the last three rows of the table

CP In A B C Out

T0 0 ?

?

?

?

T1 1 0 ?

?

?

T2 1 1 0 ?

?

T3 0 1 1 0 ?

T4 1

T5 1

T6 1

Shift Registers with Parallel

Load

The shift register shown earlier has no control input, thus data is always shifted on clock pulse

How to make the shift registers more controllable?

Shift Registers with Parallel Load

By adding a mux between each shift register stage, data can be shifted or loaded

D n

IN

2 to 1 MUX

A0

A1

Selector

SHIFT

If SHIFT is LOW, A and B are replaced by the data on DA and DB lines, else data shifts right on each clock.

Shift Registers with Parallel Load

But what if we want to hold to the current data, meaning no shift or no loading of new data?

The design must have 2 controls:

1.

For the SHIFT

2.

For the LOAD

SHIFT

0

0

1

LOAD OPERATION

0

1

X

No Change

Load Parallel

Data

Shift right

We use an AND gate to disabled the

Load input, so we mark with don’t care condition

SHIFT REGISTER WITH PARALLEL LOAD AND HOLD OPERATION

In Register Transfer Language:

Shift : Q slQ, Shift Load : Q D

Bidirectional Shift Register

Bidirectional Shift Register

Unidirectional Register

Capable of shifting only in one direction (like what we have discussed in last lecture)

1.

Shift on clock pulse

2.

Shift & Load

3.

Shift, Load & Hold

* shift occurs in one direction only

Bidirectional Register

A register that can shift in both directions

1.

Shift Left (sl)

2.

Shift Right (sr)

And at the same time is capable of HOLD and LOAD

Bidirectional Shift Register

By placing a 4-input multiplexer in front of each D flip-flop in a shift register, we can implement a circuit with shift right, shift left, parallel load, hold.

A1

A2

A3

A4

4 to 1 mux

S0 S1

S1 S0 Register Operation

0 0 No change (hold)

0 1 Shift Left

1 0 Shift Right

1 1 Parallel Load

Bidirectional Shift Register

How do we represent his in RTL :

S1 S0 Register Operation

0 0 No change (Hold)

0 1 Shift Left

1 0 Shift Right

1 1 Parallel Load

(No Transfer occurs)

S

1

S

0

: Q slQ

S

1

S

0

: Q srQ

S

1

S

0

: Q D

Bidirectional Shift Register

Lets analyze the single stage diagram of a Bidirectional Shift

Register

0

1

1

S1

0

S0 Register

Operation

0 No change (Hold)

1

0

1

Shift Left

Shift Right

Parallel Load

Bidirectional Shift Register

Shift registers can also be designed to shift more than a single bit position right or left

Bidirectional Shift Register

Shift register can be designed to shift a variable number of bit positions specified by a variable called a shift

amount.

4 Bits Bidirectional Shift Register

MUX-based Transfer

Dedicated MUX – based Transfer

Multiplexer connected to each register input produces a very flexible structure

Characterize the simultaneous transfers possible with this structure

Example 1:

S0, S1, S2 = (0,0,1) and

L0, L1, L2 = (0,0,1) then

L2 : R2

←

R1

Example 2:

S0, S1, S2 = (1,0,0) and

L0, L1, L2 = (0,1,1) then

L1: R1

←

R0, L2 : R2

←

R0

MUX and Bus – based transfer for

Multiple Registers

Multiplexer dedicated to each register

Excessive amount of logic

High number of interconnections

3 n-bit 2-to-1 MUX

Each with own “Select” signal

Each register has own

“Load” signal

MUX and Bus – based transfer for

Multiple Registers

Solution to the problem :

Shared transfer paths for registers

A shared transfer object is called a bus

Bus implementation using :

Multiplexers

Three – state nodes and drivers

In most cases, the number of bits is the length of the receiving register

Multiplexer Bus

Only need a single n-bit

3-to-1 MUX and parallel load registers

MUX outputs are shared as common path (bus)

SELECT

Determine contents of source register

LOAD

Determine destination register / register to be loaded with data

Multiplexer Bus

Example 1:

S1, S0 = (0,0) and L0, L1, L2 = (0,0,1) then

L2 : R2 R0

Multiplexer Bus

Example 2:

S1, S0 = (1,0) and L0, L1, L2 = (1,1,0) then

L0: R0 R2, L1 : R1 R2

Multiplexer Bus

Example 3:

S1, S0 = (1,0) and L0, L1, L2 = (0,1,1) then

L1: R1 R2, L2 : R2 R2 (n.change)

Multiplexer Bus

A single bus driven by a

MUX lowers cost, but limits the available transfers

Characterize the simultaneous transfers possible with this structure…

Characterize the cost savings compared to dedicated MUX…

Multiplexer Bus

3 rd transfer : cannot be done

Requires 2 simultaneous sources in a single bus

Cannot occur in 1 clock cycle

Requires at least 2 buses

However, dedicated MUX can do this

MUX-based vs Bus-based

MUX-based

Any combination of transfers is possible

Bus-based

Simultaneous transfers from different sources in single clock cycle is impossible

Reduction in hardware

Limitation in simultaneous transfers

Three – state Bus

Three – state Bus

The 3 – input MUX can be replaced by a 3 – state node (bus) and 3 – state buffers

Cost is further reduced

Signals can travel in 2 directions

Use same bus to carry signals into and out of registers

Serial Transfers &

Micro-operations

Serial Transfers & Microoperations

Serial transfers

Used for “narrow” transfer paths

Example : Telephone or cable line

Parallel – to – Serial : at source

Serial – to – Parallel : at destination

Parallel Serial Serial Parallel

Source Destination

Serial micro-operations

Example 1 : Addition

Example 2 : Error – Correction for CDs

Serial Transfers

Serial mode info is transferred / manipulated one bit at a time

Serial transfer from RA to RB is done with shift registers

Serial Transfers

Serial output (SO) of A connected with serial input (SI) of B

SI of A receives 0’s

Data from A transferred to B

Initial content of B shifted out to SO of B and lost

Serial Transfers

To maintain the data in A, connect SO of A to its SI

Serial Transfers

Shift determine when & how many times the registers are shifted

Clock pulse ( Clock ) can pass to C only when

Shift is HIGH (1)

Serial Transfers

Serial Micro-operations

Serial addition is a low cost way to add large numbers of operands, since a “tree” of full adder cells can be made to any depth.

Other operations can be performed serially as well, such as parity generation / checking or more complex error – check codes.

Shifting a binary number left = multiplying by 2

E.g: sl 0100 1000

Shifting a binary number right = dividing by 2

E.g: sr 0100 0010

Serial Adder

The circuit shown uses 2 shift registers for operands

A (3 :0)

B (3:0)

A full adder, and one more FF (for carry) is used to compute the sum

Result stored in A register and final carry in FF

Serial Adder

SI of B can receive new inputs

In each clock pulse / cycle :

New sum bit is transferred to A

New carry transferred to FF

Both registers shifted once to the right

Process cont. until

Shift = 0

Example 1:

Reg A : 1000

Reg B : 0101

Analyzing the circuit :

Serial Adder

T2

T3

T4

T0

A3 A2 A1 A0 B3 B2 B1 B0 SUM

(A+B)

+ Cin

Cout Cin

1 0 0 0 0 1 0 1 0 0 0

T1

Example 2:

Reg A : 1011

Reg B : 0101

Analyzing the circuit :

Serial Adder

T0

A3 A2 A1 A0 B3 B2 B1 B0 SUM

(A+B)

+ Cin

Cout Cin

1 0 1 1 0 1 0 1 0 0 0

T1

T2

T3

T4

Reg A

Sin

Parallel Adder

A0

A1

A2

A3

A0

B0

Cin

FA

Sout A1

B1

FA

Sin

Reg B

B0

B1

B2

B3

A2

B2

A3

B3

FA

FA

Sout

S0

S1

S2

Can be the input for

Reg A

S3

Cout

Serial vs. Parallel Transfers

Space vs. Time Trade-off

Serial adder is a sequential circuit because it includes the carry from FF. but need n clock cycle to complete the addition (Less Space, more Time)

Parallel adder is a combinational circuit because it needs n FA for n bit operation. Need only one clock cycle to complete the addition. (More

Space, less Time)

Gives the designer choice.

More Space – More cost

More Time – More delay (not fast)