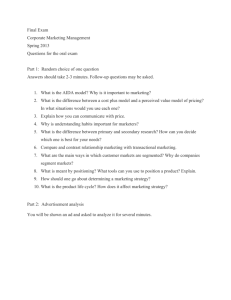

ppt

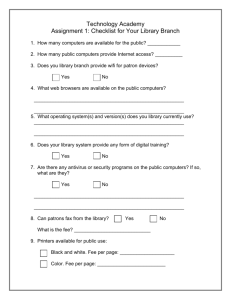

advertisement

AIDA Front end electronics Report February 2008 11th March 2008 AIDA FEE Report 1 FEE – module spec • • • • • Readout 128 strips of DSSSD via 8 , 16 channel ASICs. Module width : 8cm. Data rate defined by 10Khz implantation rate in the Detector. Timestamp readout data items based on the BUTIS distributed clock. ASIC analogue data triggered by per channel discriminator. – – • ASIC preamp output digitised at 50Mhz – 14bits. – – – – – – • • Energy Timestamp Leading Edge discriminator. Energy (MWD) including Base Line Restore. Waveform ( T(trig-pretrig) to T(trig+postrig) ) – max 20uS T0 calculation based on the rising edge of Waveform. Timestamp Pile-up detection and ??? Data items formatted and output using Gigabit Ethernet. Output Fast OR of all 128 channel discriminators. 11th March 2008 AIDA FEE Report 2 Architecture • • • • • Based on the GREAT TDR. ( Operating in Jyvaskyla ) Timestamped data items. Module divided between two identical boards. Each board has 4 ASICs – 64 channels – 1 FPGA ( $1,002.00 ) Cooling for the electronics with water cooled metal plates and conformal heat conducting foam sheet. ( Based on AGATA digitiser ) In the FPGA – Five data sources • 4 ASIC analogue (16 channels each ) • 1 Digital ( 64 channels ) • Each source provides Single Time Ordered data stream (STO). – Xilinx MicroBlaze soft processor running Linux ( under investigation ) controls acquisition. – Gigabit Ethernet link with TCP/IP for control and transfer of Data items. • • The Five data sources to be merged by external processing. ASICs mounted on mezzanine cards with connection to detectors via “crate” mounted board and Kapton cable. 11th March 2008 AIDA FEE Report 3 Board block Diagram 11th March 2008 AIDA FEE Report 4 Module construction 11th March 2008 AIDA FEE Report 5 FPGA outline block diagram FPGA outline block diagram 11th March 2008 AIDA FEE Report 6 ASIC – Analogue • Expect 6 items per implant at 10Khz. – 5 from implantation – 1 from decay • • • • Use “flip-flop” memory for item store. Each item is two 32 bit words. ( GREAT format ) Use 4 BRAMs as two blocks of 1024 x 32 512 items can be stored which is 512/6 = 85 implants. Thus the maximum time that can be stored is 2 x 85 x 100uS = 17mS. • The time to readout one store at a 32bit bus speed of 100Mhz is 1024 x 10nS = 10uS • All four stores can be read in 40uS. • A CPU tick of 1mS will be fine 11th March 2008 AIDA FEE Report 7 ASIC Digital – 1 channel • Expect 3 items per implant at 10Khz. All in different channels - on average. – 2 from edge of the implant. – 1 from decay. • Item comprises Energy, Time , Ident, Quality, and Waveform ( size is WS ). • Waveform is 20uS>WS>2uS • Incoming data is stored in a “circulating buffer”. • When LE discriminator and MWD logic agree signal is sent to the Timestamp Queue. • Energy and quality is sent to its Channel Queue and when available waveform is sent to a FIFO. 11th March 2008 AIDA FEE Report 8 Digital readout Global Clock, Sync and reset Timestamp Counter SYNC Floating point time vernier calculator 48 64 Digital Buffer status Timestamp Q 1024 x 115 Readout controller CPU path Control/status Pause/Resume To External SDRAM MPMC •Readout Controller reads the Timestamp Q and transfers items for all the active channels to the SDRAM directly through a port in the MPMC. •Two ports are used. •The data for the waveform is transferred to the external SDRAM as 32 bits at 100Mhz so it takes 5uS for a 20uS waveform size. •An Item takes about 6uS to process including the floating point time vernier calculation. ( estimate ) 11th March 2008 AIDA FEE Report 9 Time distribution and Power • One box with a single BUTIS interface • Connects to each board using a standard HDMI cable. ( High definition TV cable ) • Differential signals – Clock, SYNC, Reset, Fast-OR. • Power • One connector per module so 16 layer system of 3 DSSSD per layer means 128 sockets. • Prototype will need only 4, so prototype box… 11th March 2008 AIDA FEE Report 10 Questions • Are the Rates correct ? – Implants 10K => 60K(An) + 30K(Dig) per FPGA max (i.e. per ½ DSSSD side ) – But 1K max rate per channel? • • • • • Is the Waveform size range 20uS>WS>2us a reasonable range? What is the Time vernier calculation? Is battery backed up Master timestamp required? Is a Leading Edge Discriminator OK? Can you define the logical response to multiple hits in one channel? – Define Pile-up and how to respond to it? • • GREAT buffer overflow is indicated by the Pause/Resume system. Is this OK ? The digital Channels will queue a maximum of 60uS of waveform data. – This can be treated as 3 x 20uS or 6 x 10uS or … – Is this too much ? Can I reduce it to 40uS max ? 11th March 2008 AIDA FEE Report 11