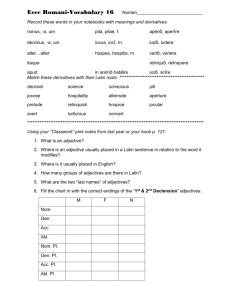

L10.6

advertisement

CSE 171 Lab 11 Digital Voltmeter Objective Design a Digital Voltmeter Using: • a Xilinx XC95108 PC84 CPLD chip • a PLDT-3 Trainer Board with a 4 MHz clock • an ADC0831 Analog-to Digital Converter chip Background VIN ADC Output = 255 * , so set VREF = 5.0 V. VREF Then, if VIN = 5.0 V, the ADC Output = 255, and as 2 * 255 = 510, the ADC Output * 2 = 102 * VIN 250 If we set VIN = * test voltage (VT) , or VT * 0.980, 255 then the ADC Output * 2 100 * VT Use of a voltage divider to approximate VT * 0.980 VT Test Voltage Input (VT) R1 = 4.7 K IT = (R1 + R2) IT VIN = IT * R2 VIN R2 = 220 K R2 = VT * (R1 + R2) 220 K = VT * 224.7 K VT * 0.979 Analog-to-Digital Converter Circuit Voltage Input +5 VDC 4.7 K CS VIN (+) VIN (-) 220 K GND 1 8 Analog-to7 2 Digital 3 Converter 6 ADC0831 5 4 VCC CLK DO VREF Xilinx XC95108 Interface The max. clock speed of the ADC0831 chip is 400 Khz, so we need a 4-bit counter to divide the PLDT-3 board 4 MHz clock frequency by 16. Clock 4.0 MHz Q0 2.0 MHz Q1 1.0 MHz Q2 0.5 MHz Q3 0.25 MHz By extending this counter to eight bits, additional Analog-to-Digital Converter control signals can be generated. Analog-to-Digital Converter Circuit Voltage Input +5 VDC 4.7 K CS VIN (+) VIN (-) 220 K GND 1 8 Analog-to7 2 Digital 3 Converter 6 ADC0831 5 4 VCC CLK DO VREF Xilinx XC95108 Interface Q3 Q4 Q5 Q6 Q7 Q3 (CLK) Q6 & Q7 (CS) Data Out (DO) 7 6 5 4 3 2 1 0 4 MHz Clock Xilinx XC95108 PC84 CPLD Clock Divider Counter Q7..Q0 Q3 Q7 Q6 CLK CS ADC0831 Interface DO Q3 Q4 Q5 Q6 Q7 Q3 (CLK) Q6 & Q7 (CS) Data Out (DO) 7 6 5 4 3 2 1 0 !Q3 shift (S) 7 6 5 4 3 2 1 0 [Q7..Q4] == 10 !Q3 display (D) (Capture) 4 MHz Clock Xilinx XC95108 PC84 CPLD Clock Divider Counter Q7..Q0 Q3 Q7 Q6 Count Detect Logic (Q7..Q4 = 10102) Capture CS ADC0831 Interface Q3 Shift Register S7..S0 Load CLK Display Register D7..D0 !Q3 Clock Data Clock DO Xilinx XC95108 PC84 CPLD (Shift Register S7..S0) (!Q3) (Capture) Load Display Register D7..D0 Clock 0 Binary-to-BCD Converter Hundreds 1 Tens Units 0 7-Segment Decoder 7-Segment Decoder 7 7 a..g dpt a..g Voltage Display Pre-Lab: • Make a copy of your Bin9BCD.abl program from Group Homework # 5. • Make copies of your cadd3.abl, hex7seg.abl, and reg4bitg.abl from Labs 3 and 10. • Download a copy of the div16cnt.abl program from the class website. • Write an ABEL program, VM.abl, that provides the control signals for an ADC0831 chip and collects and displays the value of the measured voltage. Lab: • Create a new project, Lab11a, and add copies of your Bin9BCD.abl program and the cadd3.abl program. Simulate the Bin9BCD.abl program and print out a copy of the simulation report. • Create a new project, Lab11b, and add a copy of your VM.abl program and copies of all embedded modules. • Generate a program file for your VM.abl program. • Build the ADC circuit on the breadboard and connect the circuit to the Xilinx XC95108 PC84 chip. Configure the PLDT-3 board and connect power to the PLDT-3 board. • Download and test your program. • Demonstrate your completed circuit to your lab instructor.