Programming & Development of Mobile & Embedded Systems

advertisement

Programming & Development of

Mobile & Embedded Systems

Lin Zhong

ELEC424, Fall 2010

Outline

• Programming basics

• Programming MSP430

• Programming Windows Mobile devices

2

Programming basics

• How programmable systems work

executables

Instruction

fetching

Execution unit

Non-volatile storage

Processing

Programming is about changing the content of non-volatile storage

•PC: Hard drive

•Mobile Devices: Flash ROM

•MSP430: Flash ROM

Many input channels can work

•PC: DVD/CD drive M, USB drive, Ethernet, Wi-Fi

•Mobile Devices: USB port, Bluetooth, Cellular, Wi-Fi

•MSP430: Any input (even analog!!!!)

3

Programming basics (Contd.)

• How executables are generated?

Compile

High-level language

•C/C++/C#/Java

•Matlab/Labview

•Perl

Compile

Intermediate format

•Assembly

•Java byte code

Machine code

101010100

Machine code

101010100

Machine code

101010100

Link

Machine code

101010100

Compile & link can be done at run-time

• Java & C#: second stage compilation

• Perl/BASIC (interpretive languages)

4

Cross platform development

• Cross compile & Cross link

– Produce the machine code for a foreign platform

– PCMobile devices

• X86 processorsARM processors

– PCOrbit sensors

• X86 processorsMSP430

• Cross development tool chains

– Linux GNU ARM tool chains

– Integrated development environment (IDE)

• Microsoft Visual Studio

• IAR Embedded Workbench

5

IDE concepts

• Projects

– Organized source files

– Properties of target platform

• Run-time debug

– Debug/release modes

• Emulators

– Development without a physical device

6

Programming MSP430

USB cable

JTAG

JTAG

7

IAR Embedded Workbench

• C and C++

• Software emulator

• Free evaluation version

8

IAR Embedded Workbench

• Project options

9

Run-time debugging

10

Getting help

11

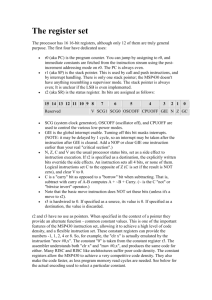

Memory space

• Unified address space

• No “cache”

12

Tilt 2 vs. PC

Registers

CPU

Cache

Main memory

File system cache

Hard disk

13

Special function registers (SFRs)

• 16 registers (R0-R15)

• Program counter (PC)/R0

– Pointer to the next instruction

14

Stack pointer (SP/R1)

• Store the return addresses of subroutine calls and

interrupts

• Stack

–

–

–

–

Last-In, First Out

PUSH

POP

Automatic allocated memory in C

• You don’t need to worry about it

– Take care by the compiler

– Subroutine calls

– Interrupt handlers

15

Status register (SR/R2)

• Can be read and written

Clock

16

Load-store architecture

a.k.a. RISC architecture

Register file

MEM/Cache

Execution unit

Load/store

17

Interrupt-driven programming

Start

System idle

Initialization

Interrupt Interrupt

• Clock

• I/O pins

• Interrupt

• Periperals

TimerA()

USARTRX()

Interrupt handlers

18

Initialization

19

Interrupt properties

• Maskable vs. non-maskable

• Nested

• Priority

20

IAR EWR interrupt

• Enable interrupt

21

IAR EWR interrupt

• Interrupt handler is a special subroutine

22

A problem

– A[0]=1;

– B[0]=1;

• enable interrupt there

• while () {

Interrupt_handler() {

A[0]=2;

B[0]=2;

}

– if (A[0]!=B[0]) exit;

– else continue ;

• }

23

A problem

• A[0]=1;

• B[0]=1;

• while () {

– if (A[0]!=B[0]) exit;

– else continue ;

• }

Interrupt_handler() {

A[0]=2;

B[0]=2;

}

LD R13, (A[0]);

LD R14, (B[0]) ;

CMP R13, R14;

JEQ EXIT

24

Critical section

• A[0]=1;

• B[0]=1;

• while () {

– if (A[0]!=B[0]) exit;

– else continue ;

• }

Section of code that access a

shared resource that must not be

concurrently accessed by more

than one thread of execution

Interrupt_handler() {

A[0]=2;

B[0]=2;

}

LD R13, (A[0]);

LD R14, (B[0]) ;

CMP R13, R14;

JEQ EXIT;

…….

25

Atomic operation

• A set of operations that appears to be one to the

system

– System state change due to the operations invisible until

all the operations are successful

– If any of the operations fails, the entire set fails; and no

change to the system state

• Examples

– An assembly instruction

– Interrupt-disabled

26

When do we need an OS?

27