forgione_p

advertisement

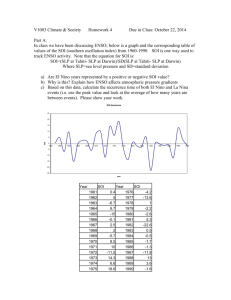

PDSOI and Radiation Effects: An Overview Josh Forgione NASA GSFC / George Washington University Forgione 1 MAPLD 2005/P104 Abstract • Silicon-On-Insulator (SOI) Complementary Metal-OxideSemiconductor (CMOS) – An alternative to bulk CMOS for radiation environments – SOI dielectric isolates device layer from substrate. – Long-time appeal to military and aerospace IC designers. • Discussion focus: – Investigate behavior of Partially-Depleted SOI (PDSOI) device with respect to three common space radiation effects: • Total Ionized Dose (TID) • Single-Event Upsets (SEUs) • Single-Event Latchup (SEL). – Test and simulation results from literature and bulk comparisons facilitate reinforcement of PDSOI radiation characteristics. Forgione 2 MAPLD 2005/P104 Introduction • Traditional CMOS is fabricated on a bulk substrate. + VS n+ VG + VD + VS n+ p+ VG + VD p+ n well P-type, ‘Bulk’’ Substrate Figure 1: Bulk CMOS device structure Forgione 3 MAPLD 2005/P104 Introduction • SOI MOSFETs are isolate from the substrate and each other via a thick insulator, or ‘buried oxide’ (BOX) + VS n+ VG p + VD + VS p n+ VG n+ + VD p SiO2 Insulator – ‘Buried Oxide’ p Substrate Figure 2: SOI CMOS device structure Forgione 4 MAPLD 2005/P104 Introduction • Device-layer thickness (tsi) determines one of two main SOI types – Partially-Depleted SOI (PDSOI): tsi > 2*xdmax • Focus of discussion – Fully-Depleted SOI (FDSOI): tsi < xdmax B: FDSOI Front Gate Depletion Fully Depleted Body tSi Front Gate Oxide xdmax Front Gate Oxide tSi xdmax A: PDSOI p Body Back Gate Buried Oxide (BOX) Back Gate Depletion Back Gate Buried Oxide (BOX) Forgione Figure 3: Distances between front and back-gate depletion regions define PDSOI (A) and FDSOI (B). 5 MAPLD 2005/P104 Introduction • Equivalent PDSOI circuit model: VG + VS n+ VG + VD p + VS n+ + VD p n+ Buried Oxide (BOX) Buried Oxide (BOX) p substrate (back gate) p substrate (back gate) VBG n+ VBG Figure 4: Transistors (left), capacitors, and diodes (right) embedded in the PDSOI MOSFET structure. Forgione 6 MAPLD 2005/P104 Introduction • PDSOI ‘floating body’ effects – Results from inherent, un-terminated body – Body-source junction can forward-bias parasitic Bipolar Junction Transistor (BJT) • Current transient – Body-source potential affects threshold voltage – Can be alleviated (but not cured!) using body ties • Body ties = Body potential connected to known reference • Difficult to implement for each transistor in a device • A must for space-flight designs Forgione 7 MAPLD 2005/P104 SOI and Single Event Latchup (SEL) • Incoming charged particles can activate parasitic thyristor structure in bulk CMOS devices – Can result in permanent device failure • SOI’s adjacent device isolation eliminates the possibility of SEL entirely. Figure 5: Cross section of a p-well CMOS inverter, with parasitic elements pertinent to latch-up[1] Forgione 8 MAPLD 2005/P104 PDSOI and SEUs • Significant SOI cross-sectional area decrease – Deposited charge in substrate cannot return to depletion region – Theoretical result: • Decreased current transients • SOI devices less susceptible to SEU Forgione Figure 6: Conceptual distribution of charge funnels in bulk (a) and SOI (a) devices. The SOI device dramatically reduces the area for collected charge[via 3]. 9 MAPLD 2005/P104 PDSOI and SEUs Figure 7: Sensitivity of the 68020 microprocessor, in CMOS/thick SOI and CMOS/epi taxial technologies, for two different test programs[4 via 5]. Forgione 10 MAPLD 2005/P104 PDSOI and SEUs Figure 8: Peak transient current as a function of strike Linear Energy Transfer (LET) and technology scaling for bulk and SOI technologies[6] Forgione 11 MAPLD 2005/P104 SEU and SOI • Parasitic BJT increases SEU sensitivity – Amplifies deposited charge – Can completely null SOI SEU advantages due to reduced cross-sectional area[2] – Spaceflight designs require body ties • Decreases BJT gain (β) Figure 9: Parasitic BJT in PDSOI Table I: Experimental and Calculated LET Threshold in SOI SRAMs in MeV/(mg/cm2), Bipolar Amplification Factors β*[4] VG + VS n+ + VD p n+ Buried Oxide (BOX) p substrate (back gate) VBG Forgione 12 MAPLD 2005/P104 PDSOI and TID • Gate-oxide charge traps can disable a bulk or SOI device – Increased leakage currents lead to threshold voltage shifts. • PDSOI buried-oxide charge traps can activate the back-gate transistor – May increased front-gate leakage currents and cause threshold voltage shifts. • Process and device design techniques can reduce the effects of trapped charge in the buried oxide[7]. Forgione 13 MAPLD 2005/P104 PDSOI and TID Figure 10: Drain-to-Source (DS) I-V characteristics for (a) a back-gate transistor irradiated to 1 Mrad (SiO2) and its effect on (b) the top-gate transistor leakage current. The transistors were irradiated in the OFF (VGS = VS = 0V; VDS = 5V) bias condition[8]. Forgione 14 MAPLD 2005/P104 Conclusions • SOI often used for low-power, high-speed devices – Desired features in military and aerospace designs • SOI SEL immunity does not infer a a cureall for radiation-tolerant designs – Inherent parasitics lead to TID and SEU sensitivities in PDSOI. Forgione 15 MAPLD 2005/P104 Conclusions • Radiation effects omitted from discussion: – Proton secondary effects – Analog and Digital Single-Event Transients (ASETs, DSETs, respectively) – Dose rate – Etc., etc. • All effects and appropriate mitigation methods must be considered during design Forgione 16 MAPLD 2005/P104 References [1] R.S. Muller, T.I. Kamins, Device Electronics for Integrated Circuits. New York: John Wiley & Sons, Inc, 2003. [2] A. G. Holmes-Siedle, Len Adams, Handbook of radiation Effects. Oxford University Press, 2002. [3] J.P. Coligne, Silicon on Insulator Technology: Materials to VLSI. Boston: Kluwer, 2003. [4] P. Lestrat, et. al, “SOI 68T020 Heavy Ions Evaluation,” IEEE Transactions on Nuclear Science, vol. 41, p. 2240, 1994. [5] O. Musseau, “Single-Event Effects in SOI Technologies and Devices,” IEEE Transactions on Nuclear Science, vol. 43, p. 603. April 1996. [6] P. Dodd, et. al, “Production and Propagation of Single-Event Transients in HighSpeed Digital Logic ICs,” IEEE Transactions on Nuclear Science, vol. 51, p. 3278, December 2004. [7] K. Bernstein, SOI Circuit Design Concepts. Hingham, MA: Kluwer, 2000. [8] J.R. Schwank, “Radiation Effects in SOI Technologies,” IEEE Transactions on Nuclear Science, vol. 50, p. 522. June 2003. Forgione 17 MAPLD 2005/P104 PDSOI and Radiation Effects: An Overview Josh Forgione NASA GSFC / George Washington University Forgione 18 MAPLD 2005/P104