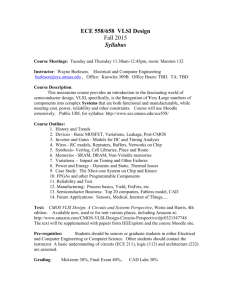

VLSI Design

advertisement

Lecture # 1 ENG6090 ENG 6090 – VLSI Design – VLSI Design Introduction to VLSI Design – Lec01. 1 ENG 6090 – VLSI Design Professor: Shawki Areibi (Off:Thorn 2335) sareibi@uoguelph.ca Lecture Mon - Fri Laboratory 10:30 - 12:00 pm Thorn2336 ENG 2307 (Digital Design Lab) Course Web Page www.uoguelph.ca/~sareibi Introduction to VLSI Design – Lec01. 2 ENG 6090 – VLSI Design COURSE INFORMATION Syllabus Grading Texts - VLSI Design/Reconfigurable Computing 30% Assign 10% Presentation 40% Project 20% Exams - Kang & Leblebici. “CMOS Digital Integrated Circuits” - Rabaey. J. “Digital Integrated Circuits”, 2002 - Uyemura J. P. “Physical Design of CMOS Integrated Circuits Using L-Edit” (optional reference) Project - Cadence Tools - Technology Files (0.18 process) Course Expectations Introduction to VLSI Design – Lec01. 3 - Must Do a Project to Illustrate your Understanding ENG 6090 – VLSI Design ENG6090 – COURSE OBJECTIVES 1. This course provides an introduction to the fundamental principles of VLSI circuit design. 2. Emphasis is placed on the design of basic building blocks of large scale digital integrated circuits and systems. 3. Understand the concept behind ASIC Design. 4. Implement a complete digital system on silicon using state of the art CAD tools. 5. Understand the consequence of scaling down the dimensions of transistors and its affect on device speed, density, …. 6. Have the necessary background to complete CMOS designs and assess which particular design style to use on a given design from FPGA to Full custom design. Introduction to VLSI Design – Lec01. 4 ENG 6090 – VLSI Design ENG6090 TOPICS TO BE COVERED Overview of VLSI Design Cycle and Methodologies nMOS, pMOS transistor theory and design equations Overview of VLSI fabrication technology, Basic CMOS digital circuits, transistor-level and mask-level design, Complex logic gates, modular building blocks Data path components, ASIC design guidelines, Hardware Descriptive Languages Reconfigurable Computing Systems (FPGAs) Physical Design Automation Introduction to VLSI Design – Lec01. 5 ENG 6090 – VLSI Design VLSI:Very Large Scale Integration • Integration: Integrated Circuits – multiple devices on one substrate • How large is Very Large? • SSI (small scale integration) – 7400 series, 10-100 transistors • MSI (medium scale) – 74000 series 100-1000 • LSI 1,000-10,000 transistors • VLSI > 10,000 transistors • ULSI/SLSI (some disagreement) Introduction to VLSI Design – Lec01. 6 ENG 6090 – VLSI Design WHY VLSI? Integration Improves the Design • Lower parasitics, higher clocking speed • Lower power • Physically small Integration Reduces Manufacturing Costs • (almost) no manual assembly • About $1-5billion/fab • Typical Fab 1 city block, a few hundred people • Packaging is largest cost • Testing is second largest cost • For low volume ICs, Design Cost may swamp all manufacturing cost Introduction to VLSI Design – Lec01. 7 ENG 6090 – VLSI Design Levels of Design • Specifications • IO, Goals and Objectives, Function, Costs • Architectural Description • VLHD, Verilog, Behavioral, Large Blocks • Logic Design • Gates plus Registers • Circuit Design • Transistors sized for power and speed • Discrete Logic, Technology Mapping • Layout • Size, Interconnect, Parasitics Introduction to VLSI Design – Lec01. 8 ENG 6090 – VLSI Design SYSTEM + MODULE GATE CIRCUIT G S n+ Introduction to VLSI Design – Lec01. 9 D n+ DEVICE ENG 6090 – VLSI Design What is “CMOS VLSI”? • MOS = Metal Oxide Semiconductor (This used to mean a Metal gate over Oxide insulation) • Now we use polycrystalline silicon which is deposited on the surface of the chip as a gate. We call this “poly” or just “red stuff” to distinguish it from the body of the chip, the substrate, which is a single crystal of silicon. • We do use metal (aluminum) for interconnection wires on the surface of the chip. Introduction to VLSI Design – Lec01. 10 ENG 6090 – VLSI Design D S G D G S Poly crossed over Diffusion Field effect transistor (FET) Insulated Gate Metal Oxide Semiconductor FET Source and Drain are Interchangeable Introduction to VLSI Design – Lec01. 11 ENG 6090 – VLSI Design N-Channel Enhancement mode MOS FET • Four Terminal Device - substrate bias –The “self aligned gate” - key to CMOS Introduction to VLSI Design – Lec01. 12 ENG 6090 – VLSI Design CMOS:Complementary MOS • Means we are using both N-channel and P-channel type enhancement mode Field Effect Transistors (FETs). • Field Effect- NO current from the controlling electrode into the output – FET is a voltage controlled current device – BJT is a current controlled current device • N/P Channel - doping of the substrate for increased carriers (electrons or holes) Introduction to VLSI Design – Lec01. 13 ENG 6090 – VLSI Design Complementary Metal Oxide Semiconductor VDD PMOS X’ X NMOS VSS Introduction to VLSI Design – Lec01. 14 ENG 6090 – VLSI Design Four Views Logic Transistor Introduction to VLSI Design – Lec01. 15 Layout Physical ENG 6090 – VLSI Design VLSI Design • The real issue inVLSI is about designing systems on chips. • The designs are complex, and we need to use structured design techniques and sophisticated design tools to manage the complexity of the design. • We also accept the fact that any technology we learn the details of will be out of date soon. • We are trying to develop and use techniques that will transcend the technology, but still respect it. Introduction to VLSI Design – Lec01. 16 ENG 6090 – VLSI Design Help from Computer Aided Design tools • Tools – – – – – – – Editors Simulators Libraries Module Synthesis Place/Route Chip Assemblers Silicon Compilers Introduction to VLSI Design – Lec01. 17 • Experts – Logic design – Electronic/circuit design – Device physics – Artwork – Applications - system design – Architectures ENG 6090 – VLSI Design Design Styles • • • • • • Full custom Standard cell Gate-array Macro-cell “FPGA” Combinations Introduction to VLSI Design – Lec01. 18 ENG 6090 – VLSI Design Full Custom • • • • • • • Hand drawn geometry All layers customized Digital and analog Simulation at transistor level (analog) High density High performance Long design time Introduction to VLSI Design – Lec01. 19 ENG 6090 – VLSI Design Full Custom Vdd IN Out Gnd Introduction to VLSI Design – Lec01. 20 ENG 6090 – VLSI Design Standard cells • Standard cells organized in rows (and, or, flipflops,etc.) • Cells made as full custom by vendor (not user). • All layers customized • Digital with possibility of special analog cells. • Simulation at gate level (digital) • Medium density • Medium-high performance • Reasonable design time Introduction to VLSI Design – Lec01. 21 ENG 6090 – VLSI Design Standard cells Routing Cell IO cell Introduction to VLSI Design – Lec01. 22 ENG 6090 – VLSI Design Gate-array • Predefined transistors connected via metal • Two types: Channel based Channel less (sea of gates) • Only metallization layers customized • Fixed array sizes (normally 5-10 different) • Digital cells in library (and, or, flip-flops,etc.) • Simulation at gate level (digital) • Medium density • Medium performance • Reasonable design time Introduction to VLSI Design – Lec01. 23 ENG 6090 – VLSI Design Gate-array Sea of gates Channel based Vdd NAND gate using gate isolation Vdd A B PMOS B Oxide isolation Out A Out NMOS Gate isolation Gnd Can in principle be used by adjacent cell Gnd Introduction to VLSI Design – Lec01. 24 ENG 6090 – VLSI Design Gate-array Sea of gates RAM Introduction to VLSI Design – Lec01. 25 ENG 6090 – VLSI Design Macro cell • • • • • • • • • • Predefined macro blocks (Processors, RAM,etc) Macro blocks made as full custom by vendor All layers customized Digital and some analog (ADC) Simulation at behavioral or gate level (digital) High density DSP processor High performance LCD RAM Short design time cont. Use standard on-chip busses ADC ROM “System on a chip” Introduction to VLSI Design – Lec01. 26 ENG 6090 – VLSI Design FPGA = Field Programmable Gate Array • • • • • • • • • • Programmable logic blocks Programmable connections between logic blocks No layers customized (standard devices) Digital only Low - medium performance (<50 - 100MHz) Low - medium density (up to ~100k gates) Programmable by: SRAM, EEROM, Anti_fuse, etc Cheap design tools on PC’s Low development cost High device cost Introduction to VLSI Design – Lec01. 27 ENG 6090 – VLSI Design FPGA Introduction to VLSI Design – Lec01. 28 ENG 6090 – VLSI Design Comparison FPGA Density Flexibility Analog Performance Design time Design costs Tools Volume Low Low (high) No Low Low Low Simple Low Gate array Medium Low No Medium Medium Medium Complex Medium Introduction to VLSI Design – Lec01. 29 Standard cell Full custom Medium High Medium High No Yes High Very high Medium High Medium High Complex Very complex High High Macro cell High Medium Yes Very high Medium High Complex High ENG 6090 – VLSI Design High performance devices • Mixture of full custom, standard cells and macro’s • Full custom for special blocks: Adder (data path), etc. • Macro’s for standard blocks: RAM, ROM, etc. • Standard cells for non critical digital blocks Introduction to VLSI Design – Lec01. 30 ENG 6090 – VLSI Design ASIC with mixture of full custom,RAM and standard cells Single port RAM Dual port RAM Full custom Standard cell FIFO Introduction to VLSI Design – Lec01. 31 ENG 6090 – VLSI Design Pentium Introduction to VLSI Design – Lec01. 32 ENG 6090 – VLSI Design ALPHA & MOTOROLA POWER PC Alpha Introduction to VLSI Design – Lec01. 33 ENG 6090 – VLSI Design New combinations • FPGA’s with RAM, PCI interface, Processor, ADC, etc. • Gate arrays with RAM, Processor, ADC, etc Processor FPGA or Gate-array logic RAM Introduction to VLSI Design – Lec01. 34