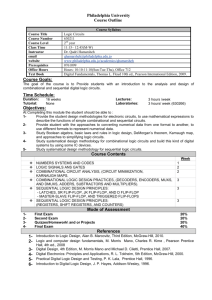

EE261 Lecture Notes (electronic)

advertisement

EE 261 – Introduction to Logic Circuits Module #7 – State Machines • Topics A. B. C. D. • Sequential Logic Finite State Machines State Variable Encoding Other Flip-Flop Devices Textbook Reading Assignments 7.1-7.8, 7.12 • Practice Problems 7.4, 7.12, 7.18, 7.44 VHDL 2-bit Binary Counter Design & Simulation (see M7_HW3 handout) • Graded Components of this Module 3 homeworks, 3 discussion, 1 quiz (2 homeworks will be uploaded to the course Dropbox, 1 homework plus the discussions & quiz are online) EE 261 – Introduction to Logic Circuits Module #7 Page 1 EE 261 – Introduction to Logic Circuits Module #7 – State Machines • What you should be able to do after this module Understand the operation of sequential logic storage devices (Latches & Flip-Flops) Draw a state diagram describing the logical operation of a finite state machine Create the State/Output tables for a finite state machine Synthesize the logic diagram of a state machine Understand the design trade-offs of various state encoding techniques Use VHDL to describe and simulate finite state machines EE 261 – Introduction to Logic Circuits Module #7 Page 2 Sequential Logic • Combinational Logic - until now, we've covered logic whose outputs depend on the current values of the input this is the definition of "Combinational Logic" • Sequential Logic - Now we move to logic circuits whose outputs depend on : - the current values of the inputs - the past values of the inputs - this is the definition of "Sequential Logic" - in order to make logic circuits based on the previous values of inputs, we need a storage device EE 261 – Introduction to Logic Circuits Module #7 Page 3 Sequential Logic • Feedback - consider this circuit - the outputs are "fed back" to the inputs - this gives the following relationships: Q = Vin1' Qn = Vin2' Vin1 = Qn Vin2 = Q Vin1 = Vin2' = Q' = Vin1 Vin2 = Vin1' = Qn' = Vin2 - this circuit will HOLD or STORE a logic value - feedback gives us the ability to build "Sequential Storage Devices" EE 261 – Introduction to Logic Circuits Module #7 Page 4 Sequential Logic • Metastability - what if the input is VDD/2 - in an ideal world, the outputs would be driven to VDD/2 - we know that noise exists in the world (thermal, shot, etc…) - noise will add a small Δv to the nodes in the system EE 261 – Introduction to Logic Circuits Module #7 Page 5 Sequential Logic • Metastability - let's consider a + Δv being superimposed on input Vin1 who starts out at VDD/2 VDD/2 + Δv VDD/2 - Δv VDD/2 - Δv VDD/2 + Δv - this causes a - Δv to be superimposed on output Q due to the inverting nature of the inverter - this - Δv is fed back to input Vin2, which in turn causes a + Δv on output Qn EE 261 – Introduction to Logic Circuits Module #7 Page 6 Sequential Logic • Metastability - this new + Δv is fed back to the original Vin1 voltage in an additive nature - this drives Vin1 even further positive, which in turn starts the loop all over again VDD/2 + Δv + Δv VDD/2 - Δv - Δv VDD/2 - Δv - Δv VDD/2 + Δv + Δv - this feedback loop continues until the inputs and outputs are driven to either a 0 or a 1 EE 261 – Introduction to Logic Circuits Module #7 Page 7 Sequential Logic • Metastability - Metastability is the situation where the inputs cause an indeterminate output in a feedback circuit - i.e., VILmax < Vin < VIHmin - using feedback, we know that the circuit will always be driven to a final state - this is also called a "Bi-Stable" element meaning that the inputs and outputs will be driven to one of two final states (i.e., a 1 or a 0) - the final state that the circuit is driven to is unknown, but we know it will go there eventually EE 261 – Introduction to Logic Circuits Module #7 Page 8 Sequential Logic • Recovery time - manufactures can specify the maximum amount of time that a bi-stable element will take to reach its final value - the time that the output is unknown is called the "Metastability Region" - the time it takes to exit the Metastable region is called the "Recovery Time" (trecovery) • Summary - feedback gives us the ability to build digital storage devices using gates - anytime we use feedback, we create a bi-stable element and can have Metastability EE 261 – Introduction to Logic Circuits Module #7 Page 9 Sequential Logic • SR Latch - consider the following circuit which is called an "SR Latch" - To understand the SR Latch, we must remember the truth table for a NOR Gate EE 261 – Introduction to Logic Circuits AB 00 01 10 11 F 1 0 0 0 Module #7 Page 10 Sequential Logic • SR Latch - when S=0 & R=0, it puts this circuit into a Bi-stable feedback mode where the output is either: Q=0, Qn=1 Q=1, Qn=0 0 0 0 1 0 0 1 1 1 0 AB 00 01 10 11 0 F 1 (U2) 0 0 (U1) 0 EE 261 – Introduction to Logic Circuits 0 AB 00 01 10 11 F 1 (U1) 0 (U2) 0 0 Module #7 Page 11 Sequential Logic • SR Latch - we can force a known state using S & R: Set (S=1, R=0) 0 Reset (S=0, R=1) 1 1 0 1 1 0 0 0 1 AB 00 01 10 11 0 F 1 (U1) 0 0 (U2) 0 (U2) EE 261 – Introduction to Logic Circuits 1 AB 00 01 10 11 F 1 (U2) 0 (U1) 0 0 (U1) Module #7 Page 12 Sequential Logic • SR Latch - we can write a Truth Table for an SR Latch as follows SR 0 0 0 1 1 0 1 1 Q Last Q 0 1 0 Qn . Last Qn 1 0 0 - Hold - Reset - Set - Don’t Use - S=1 & R=1 forces a 0 on both outputs. However, when the latch comes out of this state it is metastable. This means the final state is unknown. EE 261 – Introduction to Logic Circuits Module #7 Page 13 Sequential Logic • SR Latch - Remember the Truth Table for an SR Latch : SR 0 0 0 1 1 0 1 1 Q Last Q 0 1 0 Qn . Last Qn 1 0 0 - Hold - Reset - Set - Don’t Use - there is delay associated with changes on the input causing a change on the outputs: tPLH(SQ) = Δt for a LOW-to-HIGH transition on S to cause an output change on Q tPHL(RQ) = Δt for a HIGH-to_LOW transition on R to cause an output change on Q - there is also a specification on how small of a pulse width we can have and be recognized tPW(min) = minimum input pulse width that can be recognized EE 261 – Introduction to Logic Circuits Module #7 Page 14 Sequential Logic • S’R’ Latch - we can also use NAND gates to form an inverted SR Latch S’ R’ 0 0 0 1 1 0 1 1 Q 1 1 0 Last Q Qn . 1 0 1 Last Qn EE 261 – Introduction to Logic Circuits - Don’t Use - Set - Reset - Hold Module #7 Page 15 Sequential Logic • SR Latch w/ Enable - we then can add an enable line using NAND gates - remember the Truth Table for a NAND gate AB 00 01 10 11 F 1 1 1 0 - a 0 on any input forces a 1 on the output - when C=0, the two EN NAND Gate outputs are 1, which forces “Last Q/Qn” - when C=1, S & R are passed through INVERTED EE 261 – Introduction to Logic Circuits Module #7 Page 16 Sequential Logic • SR Latch w/ Enable - the truth table then becomes C 1 1 1 1 0 SR 0 0 0 1 1 0 1 1 x x Q Last Q 0 1 1 Last Q Qn . Last Qn 1 0 1 Last Qn - Hold - Reset - Set - Don’t Use - Hold NAND AB 00 01 10 11 EE 261 – Introduction to Logic Circuits F 1 1 1 0 Module #7 Page 17 Sequential Logic • D Latch - a modification to the SR Latch where R = S’ creates a D-latch - when C=1, Q <= D - when C=0, Q <= Last Value CD 1 0 1 1 0 x Q 0 1 Last Q Qn . 1 - track 0 - track Last Qn - Hold EE 261 – Introduction to Logic Circuits Module #7 Page 18 Sequential Logic • Flip-Flops - a "Latch" is a device that "tracks or holds" the input depending on a control signal (i.e., C or CLK) - a "Flip-Flop" is a device that will "acquire and hold" the input when a transition is present on C or CLK - Flip-Flops are commonly used in sequential logic due to their speed EE 261 – Introduction to Logic Circuits Module #7 Page 19 Sequential Logic • D-Flip-Flops - we can combine D-latches to get an edge triggered storage device (or flop) - the first D-latch is called the “Master”, the second D-latch the “Slave” Master CLK=0, Q<=D “Open” CLK=1, Q<=Q “Closed” Slave CLK=0, Q<=Q “Close” CLK=1, Q<=D “Open” - on a rising edge of clock, D is “latched” and held on Q until the next rising edge EE 261 – Introduction to Logic Circuits Module #7 Page 20 Sequential Logic • D-Flip-Flops in VHDL - In VHDL, we use a “process” to model the behavior of a D-Flip-Flop entity DFF is port (Clock Reset D Q, Qn end entity DFF; R Qn : in BIT; : in BIT; : in BIT; : out BIT); architecture DFF_arch of DFF is begin D_FLIP_FLOP : process (Clock, Reset) begin if (Reset = '0') then Q <= '0'; Qn <= '1'; elsif (Clock'event and Clock='1') then Q <= D; Qn <= not D; end if; end process D_FLIP_FLOP; -- sensitivity list end architecture DFF_arch; EE 261 – Introduction to Logic Circuits Module #7 Page 21 Sequential Logic • D-Flip-Flop Operation - Below is a timing diagram of a D-Flop R Qn D Changes but it does not effect Q. Q & Qn are updated on the rising edge of clock. EE 261 – Introduction to Logic Circuits Module #7 Page 22 Finite State Machines • Synchronous - we now have a way to store information on an edge (i.e., a flip-flop) - we can use these storage elements to build "Synchronous Circuitry" - Synchronous means that events occur on the edge of a clock Qn • State Machine - a generic name given to sequential circuit design - it is sequential because the outputs depend on : 1) the current inputs 2) past inputs - state machines are the basis for all modern digital electronics EE 261 – Introduction to Logic Circuits Module #7 Page 23 Finite State Machines • State Memory - a set of flip-flops that store the Current State of the machine - the Current State is due to all of the input conditions that have existed since the machine started - if there are "n" flip-flops, there can be 2n states - a state contains everything we need to know about all past events - we define two unique states in a machine 1) Current State 2) Next State • Qn Current State - the state that the machine is currently in - this is found on the outputs of the flip-flops (i.e., Q) EE 261 – Introduction to Logic Circuits Module #7 Page 24 Finite State Machines • Next State - the state that the machine "will go to" upon a clock edge - this is found on the inputs of the flip-flops (i.e., D) - the Next State depends on - the Current State - any Inputs - we call the Next State Logic "F" EE 261 – Introduction to Logic Circuits Module #7 Page 25 Finite State Machines • State Transition - upon a clock edge, the machine changes from the "Current State" to the "Next State" - After the clock edge, we reassign back the names (i.e., Q=Current State, D= Next State) • State Table - a table where we list which state the machine will transition to on a clock edge - this table depends on the "Current State" and the "Inputs" - we can use the following notation when describing Current and Next States Current S Scur SC Acur QC Next S* Snxt SN Bnxt QN EE 261 – Introduction to Logic Circuits Module #7 Page 26 Finite State Machines • State Table cont… - we typically give the states of our machine descriptive names (i.e., Reset, Start, Stop, S0) ex) State Table for a 4-state counter, no inputs Current State Next State S0 S1 S1 S2 S2 S3 S3 S0 EE 261 – Introduction to Logic Circuits Module #7 Page 27 Finite State Machines • State Table cont… - when there are inputs, we list them in the table ex) State Table for a 4-state counter with directional input Current State Dir Next State S0 Up Down Up Down Up Down Up Down S1 S3 S2 S0 S3 S1 S0 S2 S1 S2 S3 - we don't need to exhaustively write all of the Current States for each Input combination (i.e., Direction) which makes the table more readable EE 261 – Introduction to Logic Circuits Module #7 Page 28 Finite State Machines • State Variables - remember that the State Memory is just a set of flip-flops - also remember that the state is just the current/next binary number on the in/out of the flip-flops - we use the term State Variable to describe the input/output for a particular flip flop - let's call our State Variables Q1, Q0, …. Current State Q1 Q0 Dir Next State Q1* Q0* 0 0 0 1 1 0 1 1 Up Down Up Down Up Down Up Down 0 1 1 0 1 0 0 1 1 1 0 0 1 1 0 0 EE 261 – Introduction to Logic Circuits Module #7 Page 29 Finite State Machines • State Variables - we call the assignment of a State name to a binary number "State Encoding" ex) S0 = 00 S1 = 01 S2 = 10 S3 = 11 - this is arbitrary and up to use as designers - we can choose the encoding scheme based on our application and optimize for 1) Speed 2) Power 3) Area EE 261 – Introduction to Logic Circuits Module #7 Page 30 Finite State Machines • Next State Logic "F" - for each "Next State" variable, we need to create logic circuitry - this logic circuitry is combinational and has inputs: 1) Current State 2) any Inputs ex) Q1* = F(Current State, Inputs) = F(Q1, Q0, Dir) Q0* = F(Current State, Inputs) = F(Q1, Q0, Dir) - the logic expression for the Next State Variable is called the "Characteristic Equation" - this is a generic term that describes the logic for all flip-flops - when we write the logic for a specific flip-flop, we call this the "Excitation Equation" - this is a specific term that describes logic for your flip-flop (i.e., DFF) - there will be an Excitation Equation for each Next State Variable (i.e., each Flip-Flop) EE 261 – Introduction to Logic Circuits Module #7 Page 31 Finite State Machines • State Variables and Next State Logic "F" - we already know how to describe combinational logic (i.e., K-maps, SOP, SOP) - we simply apply this to our State Table ex) State Table for a 4-state counter, no inputs Current State Q1 Q0 Next State Q1* Q0* 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 Next State Variable F inputs F outputs - we put these inputs and outputs in a K-map and come up with Q1* = Q1 Q0 EE 261 – Introduction to Logic Circuits Module #7 Page 32 Finite State Machines • State Variables and Next State Logic "F" - we continue writing Excitation Equations for each Next State Variable in our Machine - let's now write an Excitation Equation for Q0* ex) State Table for a 4-state counter, no inputs Current State Q1 Q0 Next State Q1* Q0* 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 Next State Variable F inputs F outputs - we simply put these values in a K-map and come up with Q0* = Q0' EE 261 – Introduction to Logic Circuits Module #7 Page 33 Finite State Machines • Logic Diagram - the state machine just described would be implemented like this: Q1* Q0* EE 261 – Introduction to Logic Circuits Module #7 Page 34 Finite State Machines • Excitation Equations - we designed this State Machine using D-Flip-Flops - this is the most common type of flip-flop and widely used in modern digital systems - we can also use other flip-flops - the difference is how we turn a "Characteristic Equation" into an "Excitation Equation" - we will look at State Memory using other types of Flip-Flops later EE 261 – Introduction to Logic Circuits Module #7 Page 35 Finite State Machines (Mealy vs. Moore) • Output Logic "G" - last time we learned about State Memory - we also learned about Next State Logic "F" - the last part of our State Machine is how we create the output circuitry - the outputs are determined by Combinational Logic that we call "G" - there are two basic structures of output types 1) Mealy 2) Moore = the outputs depend on the Current State and the Inputs = the outputs depend on the Current State only EE 261 – Introduction to Logic Circuits Module #7 Page 36 Finite State Machines (Mealy vs. Moore) • State Machines “Mealy Outputs” – outputs depend on the Current State and the Inputs - G(Current State, Inputs) EE 261 – Introduction to Logic Circuits Module #7 Page 37 Finite State Machines (Mealy vs. Moore) • State Machines “Moore Outputs” – outputs depend on the Current State only - G(Current State) EE 261 – Introduction to Logic Circuits Module #7 Page 38 Finite State Machines (Mealy vs. Moore) • Output Logic "G" - we can create an "Output Table" for our desired results - most often, we include the outputs in our State Table and form a hybrid "State/Output Table" ex) Current State Q1 Q0 In 0 0 0 1 0 1 0 1 0 1 0 1 1 0 1 1 Next State Q1* Q0* 0 0 1 0 0 1 0 0 0 1 0 0 0 1 0 0 EE 261 – Introduction to Logic Circuits Out 0 0 0 0 0 0 0 1 Module #7 Page 39 Finite State Machines (Mealy vs. Moore) • State Machine Tables - officially, we use the following terms: State Table - list of the descriptive state names and how they transition Transition Table - using the explicitly state encoded variables and how they transition Output Table - listing of the outputs for all possible combinations of Current States and Inputs State/Output Table - combined table listing Current/Next states and corresponding outputs EE 261 – Introduction to Logic Circuits Module #7 Page 40 Finite State Machines (Mealy vs. Moore) • Output Logic "G" - we simply use the Current State and Inputs (if desired) as the inputs to G and form the logic expression (K-maps, SOP, POS) reflecting the output variable - this is the same process as creating the Excitation Equations for the Next State Variables ex) Current State Q1 Q0 In 0 0 0 1 0 1 0 1 0 1 0 1 1 0 1 1 G inputs Next State Q1* Q0* 0 0 1 0 0 1 0 0 0 1 0 0 0 1 0 0 Out 0 0 0 0 0 0 0 1 Output Variable G outputs - plugging these inputs/outputs into a K-map, we get G=Q1·Q0·In EE 261 – Introduction to Logic Circuits Module #7 Page 41 Finite State Machines • State Diagrams - a graphical way to describe how a state machine transitions states depending on : - Current State - Inputs - we use a "bubble" to represent a state, in which we write its descriptive name or code - we use a "directed arc" to represent a transition - we can write the Inputs next to a directed arc that causes a state transition - we can write the Output either near the directed arc or in the state bubble (typically in parenthesis) EE 261 – Introduction to Logic Circuits Module #7 Page 42 Finite State Machines • State Diagrams Ex) EE 261 – Introduction to Logic Circuits Module #7 Page 43 Finite State Machines • Timing Diagrams - notice we don't show any information about the clock in the State Diagram - the clock is "implied" (i.e., we know transitions occur on the clock edge) - note that the outputs can change asynchronously in a Mealy machine Clock In Found STATE S0 S1 S2 t EE 261 – Introduction to Logic Circuits Module #7 Page 44 Finite State Machines • State Machines - there is a basic structure for a Clocked, Synchronous State Machine 1) State Memory 2) Next State Logic “F” 3) Output Logic “G” (i.e., flip-flops) (combinational logic) (combinational logic) EE 261 – Introduction to Logic Circuits Module #7 Page 45 Finite State Machines • State Machines - the steps in a state machine design are: 1) Word Description of the Problem 2) State Diagram 3) State/Output Table 4) State Variable Assignment 5) Choose Flip-Flop type 6) Construct F 7) Construct G 8) Logic Diagram EE 261 – Introduction to Logic Circuits Module #7 Page 46 Finite State Machines • State Machine Example “Simple Gray Code Counter” 1) Design a 2-bit Gray Code Counter. There are no inputs (other than the clock). Use Binary for the State Variable Encoding 2) State Diagram EE 261 – Introduction to Logic Circuits Module #7 Page 47 Finite State Machines • State Machine Example “Simple Gray Code Counter” 3) State/Output Table Current State Next State Out CNT0 CNT1 00 CNT1 CNT2 01 CNT2 CNT3 11 CNT3 CNT0 10 EE 261 – Introduction to Logic Circuits Module #7 Page 48 Finite State Machines • State Machine Example “Simple Gray Code Counter” 4) State Variable Assignment – binary Current State Q1 Q0 Next State Q1* Q0* Out 0 0 0 1 00 0 1 1 0 01 1 0 1 1 11 1 1 0 0 10 5) Choose Flip-Flops - let's use DFF's EE 261 – Introduction to Logic Circuits Module #7 Page 49 Finite State Machines • State Machine Example “Simple Gray Code Counter” 6) Construct Next State Logic “F” Q1 Q0 0 0 1 2 0 0 Q1* = Q1Q0’ + Q1’Q0 = Q1 Q0 1 1 1 3 1 0 0 1 Q1 Q0 0 1 0 Q0* = Q0’ 2 1 1 1 3 0 EE 261 – Introduction to Logic Circuits 0 Module #7 Page 50 Finite State Machines • State Machine Example “Simple Gray Code Counter” 7) Construct Output Logic “G” Q1 Q0 0 0 1 2 0 0 Out(1) = Q1 1 1 1 3 0 1 0 1 Q1 Q0 0 0 0 Out(0) = Q1 Q0 2 1 1 1 3 1 EE 261 – Introduction to Logic Circuits 0 Module #7 Page 51 Finite State Machines • State Machine Example “Simple Gray Code Counter” 8) Logic Diagram Q1* Q0* EE 261 – Introduction to Logic Circuits Module #7 Page 52 Finite State Machines (Example) • State Machines - there is a basic structure for a Clocked, Synchronous State Machine 1) State Memory 2) Next State Logic “F 3) Output Logic “G” (i.e., flip-flops) (combinational logic) (combinational logic) EE 261 – Introduction to Logic Circuits Module #7 Page 53 Finite State Machines • State Machines - the steps in a state machine design are: 1) Word Description of the Problem 2) State Diagram 3) State/Output Table 4) State Variable Assignment 5) Choose Flip-Flop type 6) Construct F 7) Construct G 8) Logic Diagram EE 261 – Introduction to Logic Circuits Module #7 Page 54 Finite State Machines • State Machine Example “Sequence Detector” 1) Design a machine by hand that takes in a serial bit stream and looks for the pattern “1011”. When the pattern is found, a signal called “Found” is asserted 2) State Diagram EE 261 – Introduction to Logic Circuits Module #7 Page 55 Finite State Machines • State Machine Example “Sequence Detector” 3) State/Output Table Current State In Next State Out (Found) S0 0 1 0 1 0 1 0 1 S0 S1 S2 S0 S0 S3 S0 S0 0 0 0 0 0 0 0 1 S1 S2 S3 EE 261 – Introduction to Logic Circuits Module #7 Page 56 Finite State Machines • State Machine Example “Sequence Detector” 4) State Variable Assignment – let’s use binary Current State Q1 Q0 In 0 0 0 0 1 1 1 1 0 1 0 1 0 1 0 1 0 0 1 1 0 0 1 1 Next State Q1* Q0* 0 0 1 0 0 1 0 0 0 1 0 0 0 1 0 0 Out Found 0 0 0 0 0 0 0 1 5) Choose Flip-Flop Type - 99% of the time we use D-Flip-Flops EE 261 – Introduction to Logic Circuits Module #7 Page 57 Finite State Machines • State Machine Example “Sequence Detector” 6) Construct Next State Logic “F” Q1 Q1 Q0 In 00 0 2 0 0 Q1* = Q1’∙Q0∙In’ + Q1∙Q0’∙In 1 In 01 6 1 3 0 1 11 10 4 0 7 0 0 5 0 1 Q0 Q1 Q1 Q0 In 00 0 2 0 0 Q0* = Q0’∙In 1 In 1 01 6 0 3 1 11 10 4 0 7 0 0 5 0 1 Q0 EE 261 – Introduction to Logic Circuits Module #7 Page 58 Finite State Machines • State Machine Example “Sequence Detector” 7) Construct Output Logic “G” Q1 Q1 Q0 In 00 0 Found = Q1∙Q0∙In 2 0 0 1 In 01 1 6 0 3 0 11 10 4 0 7 0 0 5 1 0 Q0 8) Logic Diagram Found Q1* Q0* EE 261 – Introduction to Logic Circuits Module #7 Page 59 State Variable Encoding • State Variable Encoding - we design State Machines using descriptive state names - when we’re ready to synthesize the circuit, we need to assign values to the states - we can arbitrarily assign codes to the states in order to optimize for our application EE 261 – Introduction to Logic Circuits Module #7 Page 60 State Variable Encoding • Binary - this is the simplest and most straight forward method - we simply assign binary counts to the states S0 = 00 S1 = 01 S2 = 10 S3 = 11 - for N states, there will be log(N)/log(2) flip flops required to encode in binary - the advantages to Binary State Encoding are: 1) Efficient use of area (i.e., least amount of Flip-flops) - the disadvantages are: 1) Multiple bits switch at one time leading to increased Noise and Power 2) The next state logic can be multi-level which decreases speed EE 261 – Introduction to Logic Circuits Module #7 Page 61 State Variable Encoding • Gray Code - to avoid multiple bits switching, we can use a Gray Code S0 = 00 S1 = 01 S2 = 11 S3 = 10 - for N states, there will be log(N)/log(2) flip flops required - the advantages of Gray Code Encoding are: 1) One-bit switching at a time which reduces Noise/Power - the disadvantages are: 1) Unless doing a counter, it is hard to guarantee the order of state execution 2) The next state logic can again be multi-level which decreases speed EE 261 – Introduction to Logic Circuits Module #7 Page 62 State Variable Encoding • One-Hot - this encoding technique uses one flip-flop for each state. - each flip-flop asserts when in its assigned state S0 = 0001 S1 = 0010 S2 = 0100 S3 = 1000 - for N states, there will be N flip flops required - the advantages of One-Hot Encoding are: 1) Speed, the next state logic is one level (i.e., a Decoder structure) 2) Suited well for FPGA’s which have LUT’s & FF’s in each Cell - the disadvantages are: 1) Takes more area EE 261 – Introduction to Logic Circuits Module #7 Page 63 Other Flip-Flops Devices • Flip-Flops - we have learned about the following sequential storage devices - SR Latch - D Latch - D Flip-Flop - we can make state machines out of any sequential storage device - each flip-flop has a “Characteristic Equation” that governs how the Next State Logic is synthesized ex) Type Characteristic Eq SR Latch D Latch D Flip Flop Q* = S + R’∙Q Q* = D Q* = D - we use the Characteristic Equation & the Next State Logic to form the “Excitation Signals” that are fed into the State Memory EE 261 – Introduction to Logic Circuits Module #7 Page 64 Other Flip-Flops Devices • D Flip-Flop w/ Enable - a regular DFF transfers D to Q on a clock edge and then holds it - adding an enable gives the DFF the ability to continue holding the data while ignoring clock edges EN 1 1 1 0 CLK 0 1 x Q / Qn D / D’ Last Q / Qn Last Q / Qn Last Q / Qn - the Characteristic Eq is : Q* = EN∙D + EN’∙Q EE 261 – Introduction to Logic Circuits Module #7 Page 65 Module Overview • Topics Feedback, Metastability Latches & Flip Flops - SR Latch - S’R’ Latch - D Latch - D Flip Flop Synchronous State Machines - State Memory - Next State Logic “F” - Output Logic “G” - Mealy, Moore - State Diagrams - State Tables - Characteristic Equation - Excitation Equation - State Variable Encoding EE 261 – Introduction to Logic Circuits Module #7 Page 66