Design the digital control unit for the 9904 112 31004 stepper

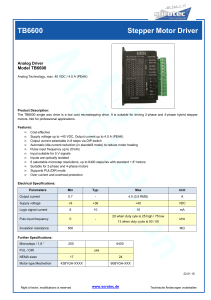

advertisement

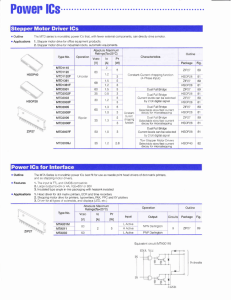

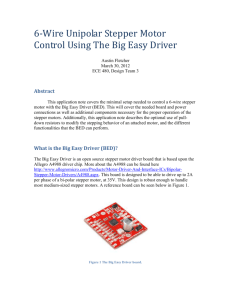

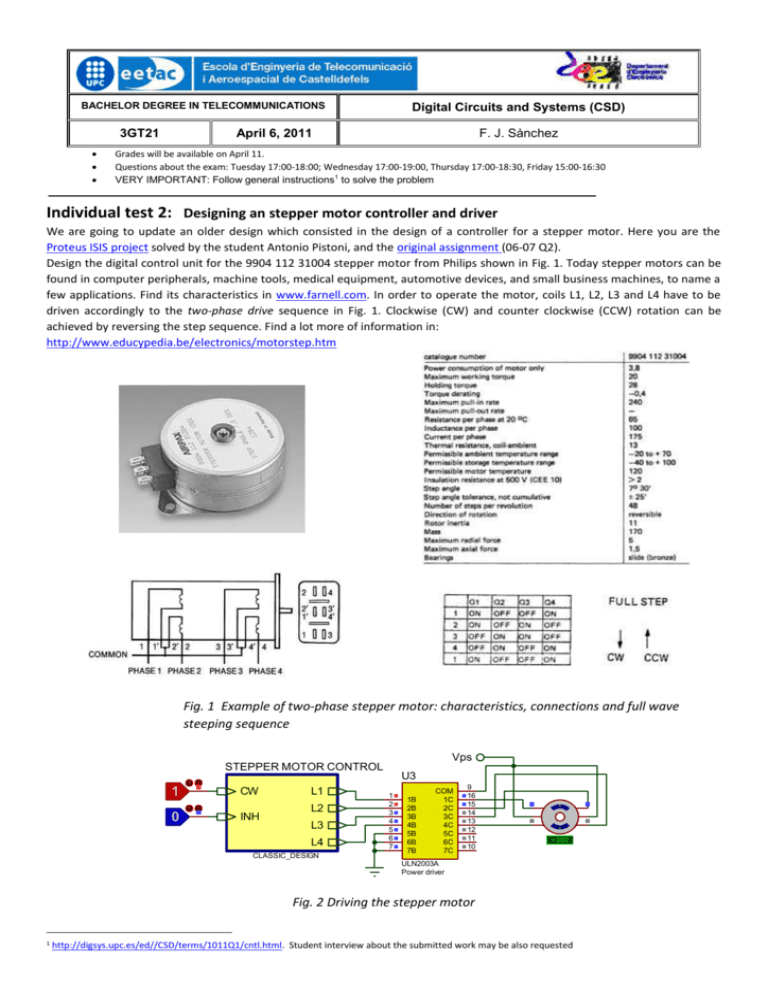

BACHELOR DEGREE IN TELECOMMUNICATIONS 3GT21 Digital Circuits and Systems (CSD) April 6, 2011 F. J. Sànchez Grades will be available on April 11. Questions about the exam: Tuesday 17:00-18:00; Wednesday 17:00-19:00, Thursday 17:00-18:30, Friday 15:00-16:30 VERY IMPORTANT: Follow general instructions1 to solve the problem Individual test 2: Designing an stepper motor controller and driver We are going to update an older design which consisted in the design of a controller for a stepper motor. Here you are the Proteus ISIS project solved by the student Antonio Pistoni, and the original assignment (06-07 Q2). Design the digital control unit for the 9904 112 31004 stepper motor from Philips shown in Fig. 1. Today stepper motors can be found in computer peripherals, machine tools, medical equipment, automotive devices, and small business machines, to name a few applications. Find its characteristics in www.farnell.com. In order to operate the motor, coils L1, L2, L3 and L4 have to be driven accordingly to the two-phase drive sequence in Fig. 1. Clockwise (CW) and counter clockwise (CCW) rotation can be achieved by reversing the step sequence. Find a lot more of information in: http://www.educypedia.be/electronics/motorstep.htm Fig. 1 Example of two-phase stepper motor: characteristics, connections and full wave steeping sequence Vps STEPPER MOTOR CONTROL 1 CW 0 INH L1 L2 L3 L4 CLASSIC_DESIGN U3 1 2 3 4 5 6 7 1B 2B 3B 4B 5B 6B 7B COM 1C 2C 3C 4C 5C 6C 7C 9 16 15 14 13 12 11 10 +360 ULN2003A Power driver Fig. 2 Driving the stepper motor 1 http://digsys.upc.es/ed//CSD/terms/1011Q1/cntl.html. Student interview about the submitted work may be also requested a) Running the sample project and determine the specifications. - Draw the symbol. - Devise the state diagrams for the system, naming states, annotating transitions and all the outputs. 1p b) Prepare a timing diagram to show some input and output activity and write the “*.do” macro which may be used later in functional or gate-level simulations. 2p c) How many VHDL files will be required? - Define the entity and write it in VHDL. - Draw the FSM internal architecture connecting all the inputs and outputs. 1p d) How many D-type flip flops will be required if the FSM is coded in binary (sequential)? - Write the VHDL code for the state register and the state type signals. 1p e) Write the VHDL code for the CC2. f) Sketch a flow chart or ASM for the process commanding the CC1 and write its VHDL code. 2p 3p In case of you are more interested in the subject … g) (extra) Start a functional simulation in ActiveHDL (work_functional) h) (extra) Start an ispLEVER project and synthesise the design for a GAL22V10. Verify your solution in Proteus-VSM using the initial project which contains the power driver ULN2003. The idea, as always, is to replace the old circuitry built using gates by a sPLD. i) (extra) Study a commercial chip with similar characteristics like this one in Fig. 3. Fig. 3 Chip UCN5804 (BiMOS II unipolar stepper-motor translator/driver) and a typical application controlling a twophase stepper-motor. www.allegromicro.com