SECT_02 System Overview - Advanced Microcomputer Systems

advertisement

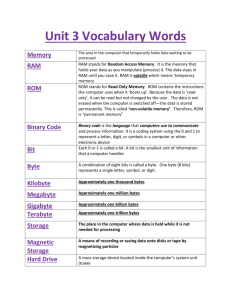

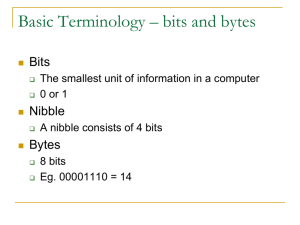

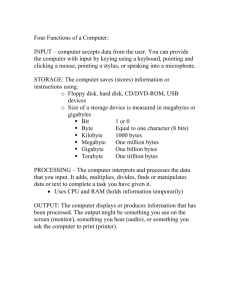

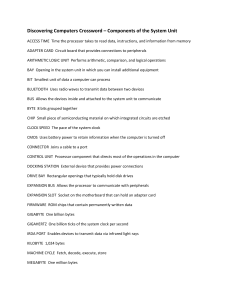

MC68HC11 System Overview MC68HC11 System Overview System block diagram (A8 version) 68HC11: major features HCMOS Technology (low power / high speed) On-chip RAM, ROM, EEPROM Basic core functions of MC6801 --improved instruction set functionality 2 operating modes and 2 test modes On-chip counter / timer On-chip analog-to-digital conversion On-chip parallel and serial ports Improved interrupt capabilities than earlier products supports 21 interrupt vectors Some fault detection capability for major errors (power, illegal instruction, hung processor) 68HC11: major features Available in at least 25 different versions – Different pin counts and packaging – Different amounts/types of memory » RAM size (192 to 1.25K bytes) » ROM size (4K to 32K bytes) » EEPROM (512 to 2K bytes) » ROM, EPROM, or EEPROM program memory Memory maps vary from version to version! – Different I/O capabilities (number of timers, chip selects, DMA channels, A/D types, etc.) CONTD 68HC11: major features Our textbook generally discusses the 68HC11A8 version, but we use the 68HC11E9 in the lab – A8: 256 bytes RAM 8 KB ROM 512 bytes EEPROM – E9: 512 bytes RAM 12 KB ROM 512 bytes EEPROM 68HC11: major features Pin assignments Basic support pins – Vdd, Vss: power (+5V) and ground – Xtal, Extal: crystal connection for internal oscillator – E: "enable" clock output signal (input freq ÷ 4) – Reset*: external reset; system failure indicator – IRQ*, XIRQ*: interrupt request lines – MODA, MODB: specifies operating mode CONTD Pin assignments Port functions (in addition to parallel I/O) – Port A: timer functions – Port B: strobed outputs, expanded mode address (high byte) – Port C: parallel I/O, expanded mode address (low byte) and data – Port D: general serial I/O pins, handshake lines for expanded mode – Port E: A/D conversion Modes of operation The chip has 2 “operating” modes and 2 “test” modes Mode determination: – On reset or power up, the mode is selected by values on pins MODA and MODB » Jumpers J3 and J4 on EVBU trainer kit – During operation, mode can be changed in some cases by writing to the HPRIO register 2 “operating” modes Single chip (MODA=0, MODB=1) – No external address and data bus functions » CPU can only access on-chip memory – Ports B and C are general purpose parallel I/O – All software needed to control MCU must be in internal memory – On reset, execution begins at address $E000 » Located in ROM » For EVBU version, checks jumper J2, may jump to CONTD $B600 (EEPROM) 2 “operating” modes Expanded multiplexed (MODA=MODB=1) – External memory and peripheral devices can be accessed by time-multiplexed address-data bus – Port B used for high byte of address (output) – Port C provides low byte of address (output) and 8- bit data (bi-directional) – External address latch is required – Execution begins at address $E000 » Just as in single-chip mode, jumper J2 can be used to have the program jump to address $B600 2 “test” modes Special bootstrap (MODA=MODB=0) – On power up or reset, the program in the bootstrap ROM is executed – CPU waits for a 256-byte program segment to be downloaded through the serial link and stored starting at address $0000 – Execution then begins at address $0000 – Permits wide variety of programs to be downloaded CONTD 2 “test” modes Special test (MODA=1, MODB=0) – Primarily a testing mode for the manufacturer – Overrides some automatic protection mechanisms -- risky! On-chip memory ROM (12K bytes) – Factory programmed – Special bootstrap ROM RAM (512 bytes) – Data, stack – Can be used for downloaded code – Low-power standby mode EEPROM (512 bytes) – Programmed and erased on-chip – Calibration storage, diagnostic log, critical data logging, security data CONTD Off-chip memory EPROM – For prototype development – Windowed and one-time programmable versions Memory maps Different versions of the HC11 have different memory maps: type, quantity, and location of memory varies Be sure to know which version you are using! – Our text references the generic HC11A8 version – We use the HC11E9 version in the lab Working with memory Usually work with 8-bit data values in HC11 (sometimes 16-bit values) Addresses are 16 bits Example: Working with memory Often show memory contents as follows: $110 8E 01 FF BD 60 00 CE 8A C0 31 E2 42 29 90 01 FE Addr 16 data values 16-bit data values are stored in consecutive memory locations – MSB = first location – LSB = second location – What is the 16-bit value stored at location $11A? 68HC11 register set 68HC11 register set 68HC11 CPU registers – Accumulators ACCA and ACCB used for computations » 8-bit values » For 16-bit computation, ACCA and ACCB may be combined and accessed as ACCD – Index registers IX and IY generally used to hold addresses » 16-bit values » Used as pointers to memory locations » Some instructions use them for 16-bit computation, also CONTD 68HC11 register set – SP and PC » Used by the CPU » Not generally used by the programmer Programming model – Register-register operations – Register-memory operations – Memory-only operations – Indexed addressing Condition code register 5 on-chip I/O ports Port A (8 bits) – 1 bidirectional pin, 4 output pins, 3 input pins – Also used for timer Port D (6 bits) – 6 bidirectional pins (controlled by direction register) – Also used for asynchronous (SCI) and synchronous serial (SPI) I/O Port E (8 bits) – 8 input pins – Also used for A/D converter CONTD 5 on-chip I/O ports Port B (8 bits) – 8 output pins with optional handshaking – Also used as address in expanded mode (replaced by PRU) Port C (8 bits) – 8 bidirectional pins with optional handshaking and wired-or mode – Also used as data/address in expanded mode (replaced by PRU) I/O registers HC11 includes 64 I/O registers – Each has a specific function – Some are used for system configuration – Others are used to interface with the different I/O subsystems » Control » Status » Data CONTD I/O registers These registers are accessed like memory locations – Addresses $1000 to $103F – Programming Reference Guide and textbook both contain list of I/O registers Eg., you write a value to a specific I/O port by storing a value to the corresponding memory location – The PORTA register is at address $1000 – The instruction STAA $1000 will write the value in ACCA to Port A Programming model -summary Use ACCA and ACCB for most operations and computations – 8-bit values Use ACCD and/or IX for 16-bit computations IX and IY usually used to hold addresses – Pointers to memory locations Perform I/O by reading/writing I/O registers – Memory locations $1000-$103F There are also several addressing modes -----but that's a topic for another day MC68HC11 EVBU Universal Evaluation Board Kit includes – MC68HC11 board – Development software (freeware assembler, PCbug11 monitor, Buffalo monitor) – Documentation Compact, low-cost "universal" evaluation board – MC68HC11E9 or MC68HCX711E9 » 12K ROM or EPROM CONTD MC68HC11 EVBU Universal Evaluation Board » 512 bytes EEPROM » 512 bytes RAM – 8 MHz crystal (2 MHz bus clock) – RS232 interface (MC145407) with DB25 connector – Reset switch (MC34064P) – Wire-wrap area Added for ECPE 4535 at Virginia Tech: – Power supply – Protoboard area – IASM11 assembler and SIM11 simulator Designing with the MC68HC11 Understand HC11 capabilities – Microcontroller resources – Standard components such as switches and displays Understand application domain – Application requirements – Appropriate algorithms – Data and signal formats CONTD Designing with the MC68HC11 Structure the design – Decompose functions and map to resources – Define interfaces between functions and keep them simple – Specify memory and timing requirements for each function – Understand interactions for timing, interrupts, data, etc.