211Notes05-CombinationalComponents

advertisement

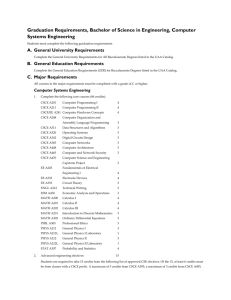

CSCE 211 Digital Design Lecture 5 Combinational Components Topics Products-of-Sums Form examples 5 variable and larger Karnaugh Maps Components: Decoders, Multiplexers Readings –1– September 21, 2015 CSCE 211H Fall 2015 Overview Last Time: Boolean Algebra Continued Combinational Circuit Analysis Sums-of-Products Form Karnaugh Maps 3,4 variable maps Don’t Care Conditions Products-of-Sums Form New: –2– Review Products-of-Sums Form (5, 6, … variable maps) Decoders Multiplexers Circuits kits on paper CSCE 211H Fall 2015 Karnaugh Map Simplification F(W,X,Y,Z) = X WX YZ 00 00 01 11 10 01 Z 11 Y 10 W –3– CSCE 211H Fall 2015 Karnaugh Map Simplification F(W,X,Y,Z) = X WX YZ 00 00 01 11 10 01 Z 11 Y 10 W –4– CSCE 211H Fall 2015 Products-of-Sums Simplification F(W,X,Y,Z) = X WX YZ 00 00 01 11 10 01 Z 11 Y 10 W –5– CSCE 211H Fall 2015 5 Variable Map Simplification F(V, W,X,Y,Z) = X X WX YZ 00 01 WX 00 01 11 10 0 4 12 8 1 5 13 9 11 3 7 15 11 10 2 6 14 10 Y YZ 00 01 Z 00 01 11 10 0 4 12 8 1 5 13 9 11 3 7 15 11 10 2 6 14 10 Y Z W W –6– CSCE 211H Fall 2015 5 Variable Map Simplification F(V, W,X,Y,Z) = X X WX YZ 00 00 01 WX 11 YZ 00 10 00 01 11 10 01 Z 01 Z 11 11 Y 10 Y 10 W W –7– CSCE 211H Fall 2015 6 Variable Map F(U,V,W,X,Y,Z) = 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 –8– CSCE 211H Fall 2015 6 Variable Map F(U,V,W,X,Y,Z) = 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 –9– CSCE 211H Fall 2015 Combinational Circuits A combinational circuit is one that – 10 – The outputs are functions strictly of the inputs There are no feedback loops CSCE 211H Fall 2015 – 11 – CSCE 211H Fall 2015 – 12 – CSCE 211H Fall 2015 – 13 – CSCE 211H Fall 2015 – 14 – CSCE 211H Fall 2015 – 15 – CSCE 211H Fall 2015 – 16 – CSCE 211H Fall 2015 – 17 – CSCE 211H Fall 2015 3x8 Decoder – 18 – CSCE 211H Fall 2015 – 19 – CSCE 211H Fall 2015 4x16 decoder from 2x4s – 20 – CSCE 211H Fall 2015 – 21 – CSCE 211H Fall 2015 Multiplexers A multiplexer selects one of its inputs to route to its outputs. – 22 – CSCE 211H Fall 2015 BreadBoard – 23 – CSCE 211H Fall 2015 Wiring an LED To wire an led 1. Hook the positive to Vcc 2. Hook the negative to a 330 ohm resistor 3. Hook the resistor to Gnd 4. Check for loose wires 5. Check for shorts + See section 3.7.5 page 129-130 for more details • I LED = 10 mA needed to light the LED • Voltage drop is about 1.6V • 303 Ohms – 24 – CSCE 211H Fall 2015 74LS00 – Quad 2 input NAND – 25 – CSCE 211H Fall 2015 74LS04 Hex Inverter – 26 – CSCE 211H Fall 2015 Half adder 1. How many inputs? 2. How many outputs? – 27 – CSCE 211H Fall 2015 6 Variable Map F(U,V,W,X,Y,Z) = 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 0 4 12 8 1 5 13 9 3 7 15 11 2 6 14 10 – 28 – CSCE 211H Fall 2015 – 29 – CSCE 211H Fall 2015 – 30 – CSCE 211H Fall 2015 Analyze This! 0 0 1 1 F1 = ? F2 = ? What are the delays? – 31 – CSCE 211H Fall 2015 Quick What’s This? – 32 – CSCE 211H Fall 2015 What’s This? – 33 – CSCE 211H Fall 2015 8 to 1 Mux from 4x1 Muxes – 34 – CSCE 211H Fall 2015 Big Multiplexers from smaller ones Show the design of a 32-to-1 Mux from 8-to-1’s and smaller muxes – 35 – CSCE 211H Fall 2015 BreadBoard – 36 – CSCE 211H Fall 2015 Wiring an LED To wire an led 1. Hook the positive to Vcc 2. Hook the negative to a 330 ohm resistor 3. Hook the resistor to Gnd 4. Check for loose wires 5. Check for shorts + See section 3.7.5 page 129-130 for more details • I LED = 10 mA needed to light the LED • Voltage drop is about 1.6V • 303 Ohms – 37 – CSCE 211H Fall 2015 74LS00 – Quad 2 input NAND – 38 – CSCE 211H Fall 2015 74LS04 Hex Inverter – 39 – CSCE 211H Fall 2015 Two Bit adder 1. How many inputs? 2. How many outputs? 3. Do we have enough chips? – 40 – CSCE 211H Fall 2015 Implementing a Binary Adder Using a Decoder PC 0 0 0 0 1 1 1 1 – 41 – X 0 0 1 1 0 0 1 1 Y 0 1 0 1 0 1 0 1 S C PC X 3x8 Decoder Y CSCE 211H Fall 2015 74LS139 Decoder Dual 2x4 decoder – 42 – CSCE 211H Fall 2015 Using a 74LS139 to implement a Half-adder X Y S C – 43 – CSCE 211H Fall 2015 74LS157 Dual 4 input Mux – 44 – CSCE 211H Fall 2015 Hardware Description Languages Hardware description language or HDL is any language from a class of computer languages for formal description of electronic circuits Boolean Algebra was applied to circuits by Shannon 1948. http://cm.bell-labs.com/cm/ms/what/shannonday/paper.html Current HDLs include: Verilog HDL VHDL – VHSIC HDL VHSIC – Very High Speed Integrated Circuits ABEL HDL - Advanced Boolean Expression Language http://en.wikipedia.org/wiki/Hardware_description_langu age – 45 – CSCE 211H Fall 2015 Seven Segment Display Common anode – 46 – CSCE 211H Fall 2015 Functions for 74LS47 with don’t cares a(D,C,B,A) = D + A.C + A.B + A’.C’ b(D,C,B,A) = D + (D'*C') + (A'*B') + (A*B) c <= d= e = A(bar) and (B or C(bar)) f = D + A'B' + B'C + A'BC g=D + B'C + C'B + A'B – 47 – CSCE 211H Fall 2015 Karnaugh Map Simplification On a real 74LS47 the outputs for 10, …15 are not don’t cares. They would indicate errors in BCD input. We could use the period for that. period(D,C,B,A)=SUM( dc(D,C,B,A) = SUM( ) ) C DC BA 00 00 01 11 10 period(D,C,B,A) = 01 A 11 B 10 D – 48 – CSCE 211H Fall 2015 Transistors History 1790s Ben Franklin “assigns” negative charge to electrons 1898 Thompson discovers the electron 1947 Shockley, Bardeen and Brattain “invent” transistor 1958 first Integrated Circuit, Texas Instruments 1971 Intel 4004, microprocessor, Ted Hoff Timeline http://www.pbs.org/transistor/ – 49 – CSCE 211H Fall 2015 Hot Batteries You should regularly check your batteries “slightly warm” is OK but hot indicates that your circuit has a short circuit. Unplug quickly and check. 1. 2. 3. – 50 – Look for direct lines Vcc to GND. Remember you need 330 ohm resistors in series with LEDs and that includes segments of the seven segment display. Recheck sections of the breadboard. CSCE 211H Fall 2015 Transistor: Water Flow Model Water flow in B raises the plunger so that water can flow from C to E. Small flow turns on and off bigger flow. Put signal on B, transfer signal C to E Reference: http://www.satcure-focus.com/tutor/page4.htm – 51 – CSCE 211H Fall 2015 Transistor Terminology Conductor – electrons easily passed from one atom to next (copper every atom has loose electron) Insulator – electrons tightly tied down to atoms, no flow Semiconductor – by adding impurities (doping) can be changed to increase conductivity Silicon wafer – used for IC circuits N-type - silicon doped with boron (excess electrons) P-ype - silicon doped with phosphorous (excess “holes” lack of electrons) – 52 – CSCE 211H Fall 2015 Transistor Reference: http://www.intel.com/education/transworks/ – 53 – CSCE 211H Fall 2015 Transistor Reference: http://www.intel.com/education/transworks/ – 54 – CSCE 211H Fall 2015 Transistor Put Positive charge on gate. This attracts electrons into gap. This allows electrons to pass freely through the gap. Reference: http://www.intel.com/education/transworks/ – 55 – CSCE 211H Fall 2015 Transistor Reference: http://www.intel.com/education/transworks/ – 56 – CSCE 211H Fall 2015 Transistor Take positive charge off Gate This stops attracting electrons. This shuts off the flow. Reference: http://www.intel.com/education/transworks/ – 57 – CSCE 211H Fall 2015 N channel transitor – 58 – CSCE 211H Fall 2015 P channel Transistor – 59 – CSCE 211H Fall 2015 CMOS Inverter – 60 – CSCE 211H Fall 2015 CMOS NAND – 61 – CSCE 211H Fall 2015 What’s This? – 62 – CSCE 211H Fall 2015 – 63 – CSCE 211H Fall 2015