By Kareem Ali Ahmed - AUC DAR Home

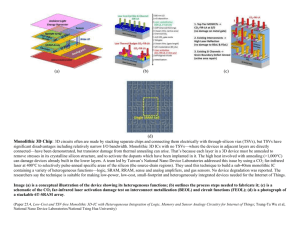

advertisement