Preventive Maintenance

Computer Engineering

Department

Research Profile

Dr. Sadiq M. Sait

Computer Engineering Department

King Fahd University of Petroleum & Minerals

Computer Engineering Faculty

20 Professorial Rank faculty members

•

2 Full Professor

•

2 Associate Professor

•

16 Assistant Professor

6 lecturers

COE Research Areas

Data Communications & Computer Networks.

Computer Applications: Robotics, Interfacing, Data acquisition, Machine learning, Data Mining.

Digital Design Automation & VLSI System Design &

Test.

Computer Architecture & Parallel Processing.

Computer Arithmetic & Cryptography.

COE Recent Research Projects: Data

Communications & Computer Networks

Wireless Multi-hop Voice over IP over Wi-Fi using

Client-Server UDP.

Mobile Patient using sensor network.

Wireless Local Area Networks Integration for Mobile

Networks Operators.

E-Tourism Promoter – An Internet Assisted Location

Tracker and Map Reader for Tourists.

A Framework for Integration of Web-based Network

Management and Management by Delegation.

Radio Resource Management and QoS Control for

Wireless Integrated Services Networks.

Adaptive TCP Mechanisms for Wireless Networks.

Engineering Modern Iterative Heuristics to Solve Hard

Computer Network Design Problems.

Wireless Multi-hop Voice over IP

Objectives

Setting up and implementing a wireless mobile ad hoc infrastructureless environment.

Imitating the cellular network topology ( Virual Base Stations)

Engergy Aware protocols

Maximizing the number of hops within the 200 ms constraint

IP telephony (protocols, basic and advanced services)

Reconfiguring IEEE 802.11 wireless cards

Impelementing H 323 protocol in

MANET

Sending data and voice over UDP/IP

H.323 Service

(Setting up Value-added Services )

Wireless Multi-hop Voice over IP

Energy Aware Gateways

Source

Input voice

Compression

≤ 200 ms

Output voice

Dest

Decompression

.

.

.

.

.

.

nodes

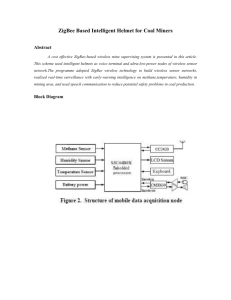

Mobile Patient

Objectives

•

Introduce mobile health as the future of medicine.

•

Cost effective solution.

•

Facilitate the use of both medical sensors and wireless mobile network in health applications.

•

Building a sensor network to monitor patients effectively:

• Providing doctors with easy access to the database

• Providing immediate help to patients

Mobile Patient

MS5536

Compatible with most existing microcontrollers

1. Uses 3-wire serial interface (SPI)

2. Low voltage/low power consumption

3. SPI programmable

1. Full TCP/IP v4/v6 support

2. 10/100 Base-T Ethernet MAC

3. Built in OS

4. Three serial ports

5. Java programmable

6. Built in web-server and FTP

Start

-reset

-information

-Request

Sensor receive request

Reading data from

PROM

Assemble data into two words

Send 2 words to TINI

TINI accept and reassemble the data

Forward data to LAB TOP

Send:

1: e-mail attachment

2: SMS

Wireless Local Area Networks Integration for Mobile Networks Operators

Motivation

•

Address capacity requirements in “hotspot” areas.

•

Provide seamless service continuity.

Objective

•

Integrate WLANs with 3G wireless data networks leading to hybrid mobile data networks.

• Describe possible architectures and integration solutions relevant to existing and future Saudi Telecom Company (STC) wireless networks.

• Present a typical deployment scenario of a WLAN into an STC wireless network

• Specify required network elements

• Provide corresponding commercially available products

WLAN Integration: Methodology &

Planned Deliverables

Survey and classify existing solutions

Identify most suitable solution or introduce new solution

Tailor the solution to suit the particular local environment and network

Survey

Solutions

Analyze & Evaluate

Solutions

Wireless

ISP server

Pick Best

Solution

(novel/existing)

WLAN IWU

CC&BS

AAA

HLR

Apply to

Case Study

Node B

Node B

Node B

RNC

Node B

3G

SGSN UMTS IP backbone

3G

GGSN

Example of WLAN Integration

Phases of Project

• Case study: Provide a typical deployment scenario in King Fahd Airport in Dammam

•

Specify required network elements and the corresponding commercial available product

E-Tourism Promoter – An Internet Assisted

Location Tracker and Map Reader for Tourists

Motivation

•

Vehicle tracking and path identification

•

E-directory (databased) for public service areas and centers of interest (hotels, hospitals, police stations, etc.)

•

Encouragement and promotion of tourism

Functionality

•

Advanced Arabic/English-based graphical user interface

•

Real-time display of information and manipulation of map

•

Communication with infrastructure networks (PSTN or

GSM/GPRS) using email/SMS/voice

•

Possible extensions: service/product advertisements, shortest path instructions, etc.

E-Tourism: Specification, Methodology and

Planned Product

•

•

•

•

Integrated database system to position on the map and query service centers and areas of interest

Minimum requirement is to identify these facilities of interest and display their attributes (phone #, email, website, etc.)

Communication using PSTN, mobile

GSM network, or GPRS/internet

Additional features may include identification of shortest path

Project Architecture

•

•

Development: JAVA and .NET framework

•

GPS communication System

•

Map application

•

Bluetooth serial support port SSP

•

GSM/GPRS modem support

An integrated software/hardware system that may be running on a

PocketPC, laptop, or a PC for demonstration purposes

A Framework for Integration of Web-based Network

Management and Management by Delegation

Network Management is mainly based on a centralized architecture. This causes the manager and its segment to become a bottleneck. The most widely used protocol is

SNMP, which lacks flexibility and efficiency.

XML provides a more flexible and standard representation and exchange of data. Load balancing techniques provide a more efficient data processing

– How can these techniques improve existing network management systems?

Objective : Develop an

XML-based network management system using JPVM to dynamically distribute the management load across multiple

XML/SNMP gateways.

Agent

Agent

JPVM XML/SNMP

Gateway

Agent

Agent

Agent

JPVM XML/SNMP

Gateway

Agent

XML-Based Network Management Station

XML-based Request over

HTTP

JPVM XML/SNMP

GATEWAY

Divide and Distribute the work to slave JPVM XML/SNMP gateways

Agent

SNMP Request

Response Handler

Agent Agent

XML-based Response over

HTTP

Generate the XMLbased Final Response

Receive Response

From all JPVM XML/

SNMP Gateway

Agent

Agent

JPVM XML/SNMP

Gateway

Agent Agent

JPVM XML/SNMP

Gateway

Agent Agent

Approach: Integration of XML and Different

Load Balancing Techniques

XML/SNMP Gateway

- A master gateway distributes the management load across multiple XML/SNMP gateways Muti-Get and Multi-Set

- A gateway translates XML to SNMP and SNMP to XML.

XML-based Network

Request

HTTP

XML-based Response

Management Station

- XML-based network management approaches using Java Parallel Virtual Machine (JPVM) :

- Dynamic load balancing

- Adaptive load balancing

- Static weighted load balancing

- Equal work non-weighted load balancing

SNMP Communication

SNMP

Request/

Response

XML-Request Servlet

XPath/Xquery

SNMP

Request/

Response

XML Response

DOM Tree Update

SNMP

Request/

Response

Router Bridge

Workstation

Achievements:

Standard representation and exchange of data

Efficient distribution of tasks: adaptive and dynamic

Delegation of tasks to other gateways

Increased processing efficiency of management data

Decreased communication time between the manager and the agents

Proposed Work related to Intel ’s R&D

The project is being extended through the investigation of the following issues:

•

New load balancing approaches that adapt dynamically in function of the network load

•

Reliable and fault-tolerant network management

•

Hierarchical network management

Adaptive Distributed and Reliable XML-based Network

Management can prove useful in areas such as:

•

Automated and remote provisioning techniques

•

Remote and reliable operations such as secure reset and power cycling

•

Remote and distributed network management applications such as monitoring, control, topology discovery, and performance evaluation

Computer Applications: Embedded Systems,

Machine Learning, Robotics

COE Recent Research Projects: Computer

Applications

Design of a wireless safety system for smart kitchen.

Predicting log properties from seismic data using abductive networks.

Design of an Intelligent Telerobotic System.

Designing and building a mobile emergency warning system for patients under health care.

Context aware energy management system.

Designing and Implementing a Safety & Health

Check System for Home Environment

Motivation

•

Preventing children accidents.

•

Keep a record of children encounters: access to hazardous appliances.

•

Provide immediate help for children when needed.

•

Utilize the advances in Web technology to keep an eye on children.

•

Enhance the level of safety at home.

Objectives

•

Introduce a safety system for the kitchen environment.

•

Cost effective solution.

• To inform child ’s parents of his status in case of emergency.

•

Building a sensor ’s network to gather real time Information of events in the kitchen:

• Detection of hazards and generating Alarms

• Identification of children to disable access to hazardous appliances and tools

Proposed Solution

Contributions:

•Remote live alert of hazardous gas.

•Low cost smart kitchen for safety of children.

•Controlled access to hazardous kitchen tools.

•Web enabled solution for monitoring of children in real time.

•Alert when gas barrel is empty.

Predicting Log Properties from Seismic

Data using Abductive Networks

Modeling well log parameters in terms of seismic data gives a more complete picture of rock properties over a reservoir.

A large number of seismic features existWhich ones are relevant?

Objective: Use abductive networks to select an optimum subset of seismic attributes and model rock porosity.

Approach: Self-Organizing Abductive

(Polynomial) Networks

- Easier to train: Self organization

- Algorithm selects: Significant inputs,

Function elements, Connectivity, Coefficients

- Automatic stopping criteria with complexity control

- More transparent models. Analytical inputoutput relationships

Achievements: y = w0 + w1 x1 + w2 x2 + w3 x1 2 + w4 x2 2

+ w5 x1 x2 + w6 x1 3 + w7 x2 3

Several porosity models at various degrees of complexity.

Accuracy comparable with previous neural network models obtained using much larger datasets.

Significant reduction in the number of input features needed.

Proposed Work related to Intel ’s R&D

COE has a wide experience in abductive network modeling for science, engineering, medical informatics, and the environment.

A project is being initiated for FPGA realization of abductive networks.

VLSI implementations of abductive models should prove useful in areas such as:

•

Intelligent processing in communication networks

•

Intelligent health care monitoring and control

•

Environmental and weather monitoring and forecasting

•

Inferential monitoring and control of industrial processes

•

Predictive maintenance for machinery

TELEROBOTICS FOR OIL

EXPLORATION AND DRILLING

PROPOSED RESEARCH

Supervisory and automatic inspection in oil exploration and drilling (OED).

Develop standards in computer and software architectures for telerobotics.

Handles real-world and communication uncertainties and respond to expected and unexpected events.

Develop a universal master workstation and application-oriented slave robots.

Develop computer-aided telerobotic tools to promote man-machine interfacing and quality of telerobotic work.

Use of inexpensive, light, easily maintainable, telerobotic systems.

Communication uncertainties

TELEROBOTICS FOR OIL

EXPLORATION AND DRILLING

Standards hardware and software architectures

New Processor architecture (effective multithreading)

•

Multithreading and multi-streaming

•

Interfacing: sensing (mobility, video, force, etc) and 3D visualization

•

Communication: real-time wireless networking

Software architecture (uncertainties in task and communication)

•

Reactivity : supervisory and linguistic control, supervised-autonomy, shared-control, cooperative and collaborative control

•

Advanced real-time motion coordination and mobility

•

Task planning : graphical modeling/simulation using VR and augmented reality

•

Reliability and exception handling : agentbased reactive behavior using multi-sensor fusion Graphic modelling

TELEROBOTICS FOR OIL

EXPLORATION AND DRILLING

Applications

Scaled telerobotics : a manned station teleoperating (wired or wirelss) a scaled slave robot for remote operations and routine maintenance in inaccessible areas like tubes, pipes, equipment, well, drilling hole, etc.

Hazardous : a manned station teleoperating a stationary or mobile robot (vehicle) for remote operations and inspection in harsh environments like high temperature, high pressure, poisonous

(gaz or other), high pollution, underground, underwater, etc.

Tight safety : a manned station teleoperating a slave robot carrying out security patrol tasks, disposal of dangerous material, rescue, fire fighting and clearance, oil platform inspection and repair, operating in emergency cases as surveillance and reconnaissance, etc.

Underwater,excavation, and drilling

Warning and Monitoring Medical System:

Designing and implementation

Motivation

•

The remote system ensures high quality service to the patients.

•

Keep a record of your patient encounters.

•

Improve information efficiency and manageability of knowledge sources.

•

Overcome nurse negligence.

•

Provide better health care and medication support.

Objectives

•

Introduce mobile health as the future of medicine.

•

Cost effective solution.

• To facilitate improved productivity using mobile health solutions.

•

Building a sensor network to monitor patients effectively:

• Providing doctors with easy access to the database

• Providing immediate help to patients

Proposed Solution

Blood Pressure

Sensor Circuit

Digital Design Automation & VLSI System Design & Test

COE Recent Research Projects: Design

Automation & VLSI System Design & Test.

Iterative Heuristics for Timing & Low Power VLSI

Standard Cell Placement.

Parallelization of Iterative Heuristics for Low Power

VLSI Standard Cell Placement.

Efficient Test Relaxation Based Static Test Compaction

Techniques for Combinational and Sequential Circuits.

Efficient Test Data Compression Techniques for

Testing Systems-on-Chip.

Segmented Addressable Scan Architecture for

Effective Test Data Compression.

COE Recent Research Projects: Design

Automation & VLSI System Design & Test.

Development of Digital Circuit Techniques for Clock

Recovery and Data Re-Timing for High Speed NRZ

Source-Synchronous Serial Data Communications.

Fast context switching configurable architectures supporting dynamic reconfiguration for computation intensive applications.

Development of Integrated Micro-electronic Heavy

Metal Sensors for Environmental Applications.

Multi-objective Finite State Machine Encoding using

Non-Deterministic Evolutionary Algorithms targeting area, low power and testability.

Design and Implementation of Scalable Interconnect

Efficient LDPC Error Correcting Codes.

Parallelizing Non-Deterministic Iterative

Heuristics to Solve VLSI CAD Problems

CAD Problems such as Floorplanning, Placement,

Routing, Scheduling, etc., require an enormous amount of computation time.

Iterative Heuristics such as Genetic Algorithms, Tabu

Search, Simulated Evolution, and others have been found effective in solving several NP-hard optimization problems.

Objective : To use a cluster of PCs to solve multiobjective VLSI CAD problems in order to improve quality and reduce run-time.

Approach: To employ a Cluster of PCs to

Distribute Computationally Intensive Tasks

Clusters of low end PCs are easy to build.

Tools such as MPI and PVM are available for message passing.

Tools such as gprof, Intel ’s VTUNE Performance

Analyzer, etc., are used for generating profiles for serial codes and determining the part of the code that has the bottlenecks.

Iterative algorithms are non-deterministic, and dividing work load, i.e. partitioning the search space, is a challenge.

The parallelizing model (i.e., Partitioning,

Communication, Agglomeration and Mapping) is very well-defined for numerical problems, which are mostly deterministic. This is not the case for Iterative heuristics, which are non-deterministic.

Tools used in our Current Cluster

MPICH Library provides a flexible implementation of MPI for easier message-passing interface development on multiple network architectures.

Intel® Trace Collector 5.0

applies event-based tracing in cluster applications with a low-overhead library. Offers performance data, recording of statistics, multi-threaded traces, and automatic instrumentation of binaries on IA-32.

Intel® Trace Analyzer 4.0

provides visual analysis of application activities gathered by the Intel Trace Collector.

TotalView (MPICH) is also used for observing communication between processors.

Also used in Condor (for scheduling jobs on the cluster).

Relationship to Intel ’s R&D

COE Department has faculty experienced in VLSI

Design.

Two books in the area of iterative algorithms and VLSI

Design have been authored by the department faculty.

The Technology Center being proposed in RI will have the state-of-art tools and equipment.

Faculty and students currently interested in HPC and parallelization of heuristics can work together to address industrial and real-world problems.

Efficient Test Compaction & Compression

Techniques for Comb. & Seq. Circuits

SOC Testing Challenges

•

Reduce amount of test data.

•

Reduce time a defective chip spends on a tester.

Test Compaction & Compression

•

Reduce the size of a test set as much as possible.

Test vector reordering for combinational circuits.

•

Steepen the curve of fault coverage vs. number of test vectors.

Efficient Test Compaction & Compression

Techniques for Comb. & Seq. Circuits

Efficient Test Relaxation for

Combinational & Sequential circuits

•

Enabling technology for test

Compaction & Compression

•

Test power reduction

Developed efficient test compaction techniques based on test relaxation.

110011001

011000110

000110011

101111100

000010001

Test Vector Decomposition

•

Maximizes test compaction by vector clustering techniques

•

Maximizes test width-based compression techniques.

110011001

Test

Relax.

1X0XX100X

X11XX0X10

0XXXX0XX1

XXXX111XX

X0X01XXXX

1XXX1X0XX

XXX00XXX1

X1XXX1X0X

Segmented Addressable Scan: Scan Test

Challenges

Test data volume challenge

•

Limited IOs & unlimited increase in transistors

•

Exponential increase in test data volume

Tester pin count challenge

•

Tester cost is almost linear in number of pins

Test time challenge

•

Critical path

•

Hard to parallelize test loading massively

Test power challenge

•

High activity leading to high power consumption.

Segmented Addressable Scan

Aggressive parallelization of scan chains

Reconfigurable partial compatibilities

Special SAS decoder

Pin count: 2 log

2

S +1 pins,

can be reduced to ONLY 2

Data volume: 10x ~ 20x compression with small designs for both SAF and TDF

Bigger designs have higher compression

Overhead:

few gates per scan chain

Power consumption

selective clocking

Test time: aggressive parallelization

test time reduction

Test Data Volume & Test Time (Delay test)

Total Data Volume

SAS Data

Volume

32 Segments

64 Segments

128 Segments

256 Segments

98 Mb Compression

Ratio

7.7 Mb 12x

5.3 Mb

4.5 Mb

3.6 Mb

17x

22x

27x

$Ms of annual test cost savings

Computer Architecture & Parallel Processing

COE Recent Research Projects: Computer

Architecture & Parallel Processing

Load Balancing for Parallel Visualization of Blood Head

Vessel Angiography on Cluster of PCs.

Shared Channels in Interconnection Networks.

Study of modified Multistage Interconnection Networks for

Networks-on-Chips.

Design of a Simulator for a Class of Dynamic

Execution Processors.

Beyond Instruction-Level Parallelism in Processor

Architecture.

Design and Performance Evaluation of a Distributed

Crossbar Scheduler.

Software Pipelining for Reconfigurable Instruction Set

Processors.

Scalable Cache Memory Design for

Large-Scale SMT Architectures

Scalable front end

•

Multiple i-caches

•

Scalable i-cache capacity

•

Scalable i-cache bandwidth

One-level scalable and shareable data cache

•

Split into multiple block-interleaved banks

•

Each bank is singleported and shared by all threads

•

Parallel access to different banks through interconnect

•

Complexity grows with number of ports and banks

I-cache

Decode &

Rename

Int

Q

FP

Q

I-cache

Decode &

Rename

Int

Q

FP

Q

Registers

&Bypass

Registers

&Bypass

Registers

&Bypass

Registers

&Bypass

ALU

Dcache

Bank

Dcache

Bank

...

ALU LS FPU

Interconnect

Dcache

Bank

ALU

Dcache

Bank

Dcache

Bank

...

Dcache

Bank

Memory Module

I-cache

Decode &

Rename

Int

Q

FP

Q

I-cache

Decode &

Rename

Int

Q

FP

Q

Memory Module

Modular and Scalable SMT (not a pure SMT)

Most hardware resources have limited thread sharing

•

I-caches, Decode logic, Queues, Registers, FUs

Simulation and Performance

SPEC 2000 Simulation

•

8 simultaneous threads

Simulation Parameters

Issue/retirement width:

32 instructions / cycle

Scheduling Queue: 128 entries

Load-Store Queue: 64 entries

Other Resources:

•

24 simple ALUs

•

8 fully pipelined FPUs

•

4 cycle-latency for FP add and FP multiply

Conclusions

•

Large-scale SMT can tolerate latencies

•

Parallel D-cache banks improve capacity and bandwidth, but increase hit latency

18

16

14

12

10

4

2

8

6

0

24

22

20

23.07

20.46

20.19

19.71

19.10

18.39

Ideal Mem Ideal Cache

188.ammp

197.parser

Latency 3

183.equake

255.vortex

Latency 5

177.mesa

175.vpr

Latency 7

176.gcc

181.mcf

Latency 9

Related Publications

•

Mudawar M. and Wani J., One-Level Cache Memory Design for Scalable

SMT Architectures, in Proceedings of the 17th ISCA International

Conference on Parallel and Distributed Computing Systems, September

15-17 2004, San Francisco, California.

•

Mudawar M., Scalable Cache Memory Design for Large-Scale SMT

Architectures, ACM International Conference Proceedings Series, Vol 68; also in Proceedings of the 3rd Workshop on Memory Performance Issues: in conjunction with 31st IEEE/ACM International Symposium on Computer

Architecture, June 20-23 2004, Munich, Germany.

Proposed work related to Intel ’s R & D

Wide experience in processor simulation and evaluation of micro-architectures.

A project is being initiated for the automatic generation of simulators from the formal description of the instruction set architecture.

We are currently investigating

•

A formal language for the concise description of an instruction set architecture.

•

Automatic generation of a simulator from a formal description.

•

Generation of an assembler from a formal description.

We are considering using this tool in

•

Proposing new instruction set architectures for research and development.

•

Education in related Computer Architecture courses.

Study of Modified Multistage Interconnection

Networks for Networks-On-Chips

Past Networks-On-Chips (NoCs) Solutions:

•

Reproduce what has been learned in the area of inter-chip networks,

•

Focus on the router architecture alone to achieve certain goals in latency

•

Asynchronous design of NoCs, mainly GALS

•

Circuit switching techniques introduced to provide a certain guarantee for the latency.

•

Did not fully take advantage of the fact that the network is on-chip where the main gain is no-pin limitation.

•

Router architectures directly derived from inter-chip architectures where the routers were implemented on a single chip. This implies a substantial overhead.

•

Added complexity to achieve guaranteed latency is an overkill in the onchip context.

Analysis:

•

Low throughput . Means: latency cannot be guaranteed above the maximum throughput levels

•

Cannot prevent contention from happening . Contention makes router architectures more complex because they need to integrate buffering and prioritization logic.

•

Routers that implement both packet and circuit switching makes the architecture even more complex .

Modified Multistage

Idea

•

•

Contention free

Router architecture bufferless because no contention = no need to buffer

Which network is almost contention free?

•

•

Crossbar with Virtual Output Queues

Crossbar non-scalable

What topology resembles a crossbar?

•

Banyans or Multistage Interconnection Networks.

• Unidirectional: Wire Routing issue.

• Bidirectional multistage or folded multistage networks:

Good

• Bidirectional multistage are two entities:

• The MIN, so-called “fat-tree” network

•

The butterfly.

• MIN better than butterfly (previous work)

How to modify the MIN so that it becomes contention free?

•

Routing in a MIN:

• Going up: adaptive

• Going down: deterministic. Means a high probability of contention.

•

Solution: add as many output down links as there is a probability of contention per stage

Preliminary Results: latency is minimal throughput is

> 90%

C

R

R

R

R

R

R

C C

R

R

R

R

R

R

C C C C

Regular MIN

C C

R

R

R

R

R

R

C C C

Modified MIN

C

R

R

R

R

R

R

C C

C

Proposed work related to Intel ’s R & D

Large Experience in Interconnection Networks

Evaluation.

Large Experience in ASIC/SoC Design.

System C based simulation/performance evaluation environment under development.

Future investigations

•

Customized automatic generation of topologies and routers that implement bufferless approach.

•

Investigate the automatic generation of bandwidthasymmetric network for non-equal requirements on the side of the IP-core clients.

•

Mathematical Analysis to Determine Maximum Latency

Levels in the context of bufferless architecture routers.

Computer Arithmetic & Cryptography

COE Recent Research Projects: Computer

Arithmetic & Cryptography

High-Performance Arithmetic for Cryptographic

Applications.

Design of efficient integrated circuits for the inverse computation in different finite fields.

Design of Elliptic Curve Cryptography Architectures using parallel multipliers.

Secure reliable storage system.

Design, Analysis, and FPGA prototyping of High-

Performance Arithmetic for Cryptographic Applications.

High-Performance Arithmetic Circuitry for Cryptography

New Modulo Multiplication Algorithm & Circuitry

Patent Application Pending.

New High-Radix Multiplier Divider Algorithm and

Hardware performing the operation (A*B/N) with hardware complexity close to that of Division operation

Patent in Preparation.

Efficient Parallel Implementations of Elliptic Curve

Cryptosystems.

Aladdin Modulo Multiplier

Public-Key Encryption/Decryption Algorithms Largely depend on the computation of Modulo multiplication

(AB mod N).

Current Dominant Method is Montgomery ’s

Circuitry have been modeled and verified using VHDL

Montgomery

Pre-computations Excessive Minor

Aladdin

Single Modulo

Multiplication

Impractical

Produces Quotient No

Modulus

Modulo

Exponentiation

Very Practical

Yes

Must be ODD No Restrictions

O(n

2

) O(n

2

) but with 15% higher proportionality constant

High-Radix Multiplier Divider

Theory Fully Developed

For n-bit operands, with k-bit radix system ( k > 8 ), computing ( A*B/N ) requires ( n / k ) steps instead of n .

Research is continuing to study full exploitation of such processor for faster performance of:

•

Pure multiplication

•

Pure division

ECC Efficient Implementations

Efficient High-Speed computation of the Scalar

Multiplication operation (ECC) through exploiting parallelism.

Improved Resistance against Side Channel Attacks

(SCA):

•

Parallelism

•

Randomized computation order starting Least-2-Most or

Most-2-Least

•

Randomized Number of Processors

•

Randomized coordinate system (affine vs projective)

Hardware will be implemented on an FPGA platform.

Available Experience ….

COE has a wide experience in digital circuits and VLSI design.

Work is verified on FPGA platform but can readily be ported onto dedicated VLSI processors.

Developed Circuits & Algorithms can be readily used by INTEL.

Our Needs:

•

Professional CAD Tools for VLSI design, verification, and synthesis tools e.g. Mentor Graphics tools, Cadence, etc.

Computer Engineering Faculty

Research Profile

Dr. Sadiq Sait, Professor

Research Interests

•

Digital Design Automation, VLSI System Design, High Level

Synthesis, and Iterative Algorithms.

Recent Projects

•

Parallelization of Iterative Heuristics for Low Power VLSI Standard

Cell Placement ', KFUPM, 2003-2005.

•

Iterative Heuristics for Timing & Low Power VLSI Standard Cell

Placement , KFUPM, 2001-2003.

Recent Publications

•

Sadiq M. Sait and Junaid A. Khan, " Simulated Evolution for Timing

& Low-Power VLSI Standard Cell Placement ", Engineering

Applications to Artificial Intelligence (EAAI), Vol. 16, Sep. 2003, pp.

407-423.

•

Sadiq M. Sait and H. Youssef. Iterative Computer Algorithms with

Applications in Engineering: Solving Combinatorial Optimization

Problems.

December 1999, IEEE Computer Society Press,

California.

•

Sadiq M. Sait and H. Youssef. VLSI Physical Design Automation:

Theory and Practice , McGraw-Hill Book Co., Europe, December

1994. Also Co-published by IEEE Press, USA, January 1995 (Hard bound edition).

Dr. Mayez Al-Muhammad, Professor

Research Interests

•

Computer Architecture, Parallel Processing and Algorithms,

Computer Networks, and Robotics.

Recent Projects

•

Design of a Simulator for a Class of Dynamic Execution

Processors , KFUPM, 2003-2004.

•

Design of an Intelligent Telerobotic System , King Abdulaziz

City for Science and Technology (KACST). 2000-2004.

Recent Publications

•

M. Al-Mouhamed, M. Kaleemudding, and H. Youssef,

Evaluation of Pipelined Dilated Switch Architectures for

ATM Networks, IEEE/ACM Trans. on Networking, Vol. 7,

No. 5, October 1999, pp. 724-740.

•

M. Al-Mouhamed, O. Toker, and A-K Al-Harthy, “ A 3D Vision-

Based Man-Machine Interface For Hand-Controlled Telerobot ”,

IEEE Transactions on Industrial Electronics, Vol 52, No 1, 2005, pp. 306-319.

•

M. Al-Mouhamed, Array Organization in Parallel Memories ,

International Journal of Parallel Programming (IJPP), Vol 32,

No.2, April, 2004, pp.123-163.

Dr. Alaaeldin Amin, Assoc. Professor

Research Interests

•

VLSI Integrated Circuit design, MOS Memory Design and Testing,

Computer Arithmetic & Cryptography, Digital System Testing and

Asynchronous Design.

Recent Projects

•

High-Performance Arithmetic for Cryptographic Applications

Industrial Experience

•

8 Years in MOS Memory Design (National Semiconductor MOS Memory

R&D)

Patents

•

4 US Patents in Flash Memory architectures, circuits & cells

•

2 Patent Applications for High Performance Arithmetic for Cryptographic

Applications.

Publications

•

Double-rail encoded self-timed adder with matched delays (IEEE ICEC

2003).

•

Asynchronous Modulo Multiplier for Cryptosystems , (IEEE GCC, 2004 ).

•

Fault Models and Efficient BIST Algorithm for Dual Port Memories (IEEE

TCAD 1997).

Dr. Radwan Abdel-Aal, Assoc. Professor

Research Interests

•

Multidisciplinary applications of abductive networks machine learning in science, engineering and medicine , Data acquisition and analysis for experimental and nuclear physics, Testing of digital systems.

Recent Projects

•

Predicting log properties from seismic data using abductive networks ”. 1

Feb-31 Oct 2005, Client: Saudi Aramco, Value: SR 272,646.

Industrial Experience

•

4 Years in Digital Systems Design (Microwave Associates Inc.,

Bedfordshire, UK).

Recent Publications

•

Abdel-Aal, R. GMDH-based feature ranking and selection for improved classification of medical data , Journal of Biomedical Informatics, 2005.

•

Abdel-Aal, R. Improving electric load forecasts using network committees ,

Electric Power Systems Research, v. 74, pp. 83 –94, 2005.

•

Abdel-Aal, R. Hourly temperature forecasting using abductive networks ,

Engineering Applications of Artificial Intelligence, v. 17, pp. 543-556, 2004.

•

Abdel-Aal, R. Short term hourly load forecasting using abductive networks .

IEEE Trans on Power Systems, v. 19, pp. 164-173, 2004.

Dr. Aiman El-Maleh, Assist. Professor

Research Interests

•

Testing and Synthesis of Digital Systems, Error Correcting LDPC Codes.

Recent Projects

•

Multi-objective Finite State Machine Encoding using Non-Deterministic

Evolutionary Algorithms , KFUPM, 2005-2007.

•

Efficient Test Relaxation Based Static Test Compaction Techniques for

Combinational and Sequential Circuits , KFUPM, 2004-2005.

Industrial Experience

•

Member of Scientific Staff, Mentor Graphics Corp. Oregon, USA (1995-

1998).

Patents

•

Test Pattern Generation for an Electronic Circuit Using a Transformed Circuit

Description, US Patent 5,528,604.

Recent Publications

•

A. El-Maleh, S. Khursheed, S. Sait, “ Static Compaction Techniques for Sequential

Circuits Based on Reverse Order Restoration and Test Relaxation ” IEEE 14th Asian

Test Symp., 2005 .

•

A. El-Maleh and K. Al-Utaibi, “ An Efficient Test Relaxation Technique for Synchronous

Sequential Circuits , ” IEEE Transactions on Computer Aided Design of Integrated

Circuits, Vol. 23, pp. 933-940, June 2004.

•

A. El-Maleh and Y. Osais, " Test Vector Decomposition Based Static Compaction

Algorithms for Combinational Circuits ", ACM Transactions on Design Automation of

Electronic Systems, Vol. 8, pp. 430 - 459, Oct. 2003.

Dr. Muhamed El-Rabaa, Assist. Professor

Research Interests

•

Low-Power Digital Circuits, Digital Communication Circuits, Configurable

Computing.

Recent Projects

•

Development of Digital Circuit Techniques for Clock Recovery and Data

Re-Timing for High Speed NRZ Source-Synchronous Serial Data

Communications , KFUPM, 2005-2007.

•

Fast context switching configurable architectures supporting dynamic reconfiguration for computation intensive applications , 2005-2007.

Industrial Experience

•

Senior Component Design Engineer, Intel Corp., Oregon, USA (1995-

1998).

Patents

•

Two US patents in BiCMOS design No. 5,602,774 (1999) and No.

5,966,032 (1997).

Recent Publications

•

Muhammad E. S. Elrabaa, " A New Static Differential CMOS Logic with Superior Low

Power Performance ," Analog Integrated Circuits and Signal Processing, Vol. 43, No.

2, pp. 183-190, May 2005.

•

Muhammad E. S. Elrabaa, " An All-Digital Clock Recovery and Data Retiming

Circuitry for High Speed NRZ Data Communications ," IEICE Transactions on

Electronics (Japan), Vol. E85-C, No. 5, P. 1170, May, 2002.

•

Muhammad E. S. Elrabaa, Mohab Anis, and Mohamed Elmasry, " A Contention-Free

DOMINO Logic For Scaled-Down CMOS ," IEICE Transactions on Electronics, Vol.

E85-C, No. 5, P. 1177, May, 2002.

Dr. Ahmad Al-Yamani, Assist. Professor

Research Interests

•

VLSI Design and Test (Test Compression and BIST), Fault Tolerance, Iterative

Heuristics.

Recent Projects

•

Lead the VLSI test experiments at Stanford between 01 and 05.

•

Test data compression using compatibility classes.

Industrial Experience

•

Lead a major test cost saving operation with $millions of annual savings.

Patents

•

Four US patents filed (all related to VLSI test).

Recent Publications

•

Al-Yamani, A., E. Chmelar and M. Grinchuk, " Segmented Addressable Scan

Architecture ," 23 rd IEEE VLSI Test Symposium (VTS'05) , Palm Springs, CA, May 1-

5, 2005. PATENT PENDING TECHNOLOGY

•

Al-Yamani, A., and E.J. McCluskey, " BIST-Guided ATPG ," 6 th IEEE International

Symposium on Quality Electronics Design (ISQED'05) , San Jose, CA, March, 05.

•

Al-Yamani, A., and E. McCluskey, " Test Quality for High Level Structural Test ," ACM

Transactions on Design & Test of Electronic Systems ( TODAES'05 ) , Oct. 05.

•

McCluskey, E.J., Al-Yamani, Li, Tseng, Volkerink, Ferhani, Li, and Mitra," ELF-

Murphy Data on Defects and Test Sets ," 22 nd IEEE VLSI Test Symposium

(VTS

’04)

, Napa Valley, CA, Apr. 25-28, 2004. STANFORD TEST EXPERIMENT .

Dr. Adnan Gutub, Assist. Professor

Research Interests

•

Modeling, simulating, and synthesizing VLSI hardware for cryptography and computer arithmetic operations.

Recent Projects

•

Design of efficient integrated circuits for the inverse computation in different finite fields.

•

Design of Elliptic Curve Cryptography Architectures using parallel multipliers.

Recent Publications

•

Adnan Abdul-Aziz Gutub and Alexandre F. Tenca, “ Efficient Scalable VLSI

Architecture for Montgomery Inversion in GF(p) ”, Integration, the VLSI

Journal , Vol. 37, No. 2, pages 103-120, May 2004.

•

Adnan Abdul-Aziz Gutub, “ VLSI CORE ARCHITECTURE FOR GF(P)

ELLIPTIC CURVE CRYPTO PROCESSOR ”, IEEE 10th International

Conference on Electronics, Circuits and Systems (ICECS 2003) , pages 84-

87, University of Sharjah, United Arab Emirates, December 14-17, 2003.

•

Adnan Abdul-Aziz Gutub and Alexandre F. Tenca, “ Efficient Scalable

Hardware Architecture for Montgomery Inverse Computation in GF(P) ”,

IEEE Workshop on Signal Processing Systems (SIPS ’03) , pages 93-98,

Seoul, Korea, August 27-29, 2003.

Dr. Abdelhafid Bouhraoua, Assist.

Professor

Research Interests

•

ASIC/SoC Design and Verification Methodologies, Digital System Design,

Interconnection Networks, Switch Architectures, Telecommunication protocols, Computer Cryptography and Asynchronous Design.

Recent Projects

•

Study of modified Multistage Interconnection Networks for Networks-on-

Chips .

•

Design and Performance Evaluation of a Distributed Crossbar Scheduler .

Industrial Experience

•

6 years experience in ASIC Design/Verification, mostly as Chip Architect for

AMCC and Zarlink Semiconductor. Worked on Network Processors,

SONET, Digital Wrapper, Reed Solomon Codecs, VDSL PHY Chipset, ATM framers, TDM and Ethernet Switches.

•

Directed product and field testing at Lambda Opticalsystems Corp building an all-optical MEMS-based carrier-class switch.

Patents

•

Patent Applications for VDSL aggregation line-rate circuitry.

Publications

•

Experimental Study of a Generic Router Architecture under MILE ,

IASTED'97

•

Adaptive Message Routing for Compact Reconfigurable Router , IEEE

ICECS'97.

Dr. AbdulRahim Naseer, Assist. Professor

Research Interests

•

Design Automation and FPGA based Synthesis, Reconfigurable

Computing, Hardware Software Co-Design and Embedded

Systems, Computer Architecture, Parallel and distributed processing

Recent Projects

•

Software Pipelining for Reconfigurable Instruction Set Processors

•

Design and Implementation of a Reconfigurable Network Interface

•

Load Balancing for Parallel Visualization of Blood Head Vessel

Angiography on Cluster of PCs

Recent Publications

•

A. .R. Naseer, et al., “Adaptive Pre-Task Assignment scheduling strategy for heterogeneous distributed raytracing system ”, Journal IEICE EE , vol.

1, No. 13, October 2004, pp 373-379

•

A. R. Naseer, et al., “Direct Mapping of RTL Structures onto LUT-Based

FPGAs ”, IEEE Transactions on Computer Aided Design of Integrated

Circuits and Systems, Volume 17, July 1998, pp. 624-631

•

A. R. Naseer, "FAST : FPGA Targeted RTL Structure Synthesis Technique",

Proc. of IEEE/ACM 7th International Conference on VLSI Design'94

January 1994, pp. 21-24 (bagged the BEST PAPER AWARD)

Dr. Muhamed Mudawar, Assist. Professor

Research Interests

•

Processor Micro-architecture, Multiprocessors and Interconnection

Networks, Parallel programming environments and compilation techniques

Recent Projects

•

Beyond Instruction-Level Parallelism in Processor Architecture ,

AUC, 2002-2003.

•

Shared Channels in Interconnection Networks, AUC 1999-2000.

Recent Publications

•

Mudawar M., Scalable Cache Memory Design for Large-Scale SMT

Architectures , Proc. of the 3rd Workshop on Memory Performance

Issues , June 20-23 2004, Munich, Germany .

•

Mudawwar M. and Saad A., The k-ary n-cube Network and its Dual: a Comparative Study , in Proceedings of the 13th IASTED

International Conference on Parallel and Distributed Computing and

Systems , August 21-24, 2001, Anaheim, California, pages 254-259.

•

Mudawwar M. and Mameesh R., Region Broadcasting in k-ary mway Networks , in Proc. of the ISCA 13th International Conference on Parallel and Distributed Computing Systems , August 8-10, 2000,

Las Vegas, Nevada, pages 268-274.

Dr. Ashraf Mahmoud, Assist. Professor

Research Interests

•

3G/4G wireless networking

– Wi-Fi and Wi-Max networks, Performance analysis and capacity for wireless networks, Simulation and modeling

Recent Projects

•

Wireless Local Area Networks Integration for Mobile Networks Operators ,

2005.

•

E-Tourism Promoter – An Internet Assisted Location Tracker and Map

Reader for Tourists , 2005.

Industrial Experience

•

5 years with Nortel Networks, Ottawa, Canada

Patents

•

3 Patent applications in the area of radio resource managements

Recent Publications

•

“

Performance of Inter-Base Station Soft Handoff for 3G CDMA Networks ,

”

ICMSAO ’05.

•

“ Non-blocking FCFS algorithm for Data Services over Wireless CDMA

Networks, ” ICMSAO’05

•

“ Buffer Occupancy Analysis For A Broadband Polling-Based WLAN , ” Net-

Con'2003)

Dr. Mohammed H. Sqalli, Assist. Professor

Research Interests

•

Network Design, Network Management, Iterative Heuristics, Constraint

Satisfaction Problems (CSP), and Case-Based Reasoning (CBR).

Recent Projects

•

A Framework for Integration of Web-based Network Management and

Management by Delegation , 2004-2006.

•

Web Engineering Modern Iterative Heuristics to Solve Hard Computer

Network Design Problems , 2004-2005.

Industrial Experience

•

Senior Automation Testing Specialist, Siemens, Ottawa, Canada (1999-

2002).

Recent Publications

•

M. H. Sqalli, and S. Sirajuddin, “ Static Weighted Load-balancing for XMLbased Network Management using JPVM ”, Proceedings of the 8th

International Conference on Management of Multimedia Networks and

Services (MMNS 2005), Barcelona, Spain, October 24-26, 2005.

•

S. Sirajuddin, and M. H. Sqalli, “ Comparison of CSV and DOM Tree

Approaches in XML-based Network Management ”, Proceedings of the 12th

International Conference on Telecommunications (ICT 2005), Cape Town,

South Africa, May 3-6, 2005.

•

C. Marling, M. H. Sqalli, E. Rissland, H. Muñoz-Avila, and D. Aha, “ Case-

Based Reasoning Integrations ”, AI Magazine, Volume 23, Issue 1, Spring

2002, 69-86.

Dr. Tarek Sheltami, Assist. Professor

Research Interests

•

Wireless Ad Hoc and Sensor Networks, Wireless mobile Multi-hop voice/video over IP, Pervasive Computing, Heterogeneous

Netowrks, Wireless Communication Protocols.

Recent Projects

•

Wireless Multi-hop Voice over IP over Wi-Fi using Client-Server

UDP , 2005.

•

Mobile Patient using sensor network , 2005.

Recent Publications

•

T. R. Sheltami and H. T. Mouftah, “ Average waiting time of Clusterhead

Controlled Token for Virtual Base Station On-demand in MANETs , ” ACM

‘Ad Hoc Networks’ of the journal ‘Cluster Computing’, Kluwer Academic

Publisher, July 2005, vol. 8, no. 2-3, pp. 157-165(9).

•

T. R. Sheltami and H. T. Mouftah, “ A Warning Energy Aware Clusterhead

(WEAC) for MANETs , ” IEEE Trans. on Wireless Communications, 2005

•

T. R. Sheltami and H. T. Mouftah,

“

Power Aware Routing for the Virtual

Base Station On-demand Protocol in MANETs , ” The Arabian Journal for

Science and Engineering., Vol 28, number 2C, 2003.

•

T. R. Sheltami and H. T. Mouftah, “ Minimum Power-Routing for the Virtual

Base Station On-demand Protocol in MANETs , ” Computer Networks: The

Intern. Journal of Computer and Telecommunications Networking 2003.

Dr. Uthman Baroudi, Assist. Professor

Research Interests

•

Radio Resource Management, Ad hoc Networking, Multiple

Access Schemes .

Recent Projects

•

Radio Resource Management and QoS Control for Wireless

Integrated Services Networks ; 75KSAR, KFUPM from Sep. 2005-

Dec. 2006

•

Adaptive TCP Mechanisms for Wireless Networks , 75KSAR,

KFUPM, from Sep. 2005-Dec. 2006.

Recent Publications

•

U. Baroudi and A. Elhakeem, “ A Simulation Study for Adaptive

Admission/Congestion Control Policies for CDMA Based Wireless Internet ”

Wireless Communications and Mobile Computing Journal, 2006.

•

Yaser Al-Jarbou and U. Baroudi , “ Performance of Heterogeneous Traffic in

Roaming Based Sharing Multi Operator 4G WCDMA ” 2nd International

Symposium on Wireless Communication Systems 2005, Italy.

•

U. Baroudi and A. K. Elhakeem, " A Hybrid TDMA/MC-CDMA Utilizing

Multiuser Detection for Integrated Wireless Networks " IEICE Transactions on Communications, Vol.E83-B, No. 6, pp. 1308-1320, June 2000.

Dr. Marwan Abu Amara, Assist. Professor

Research Interests

•

3G/4G wireless networking, Fault-tolerance in wireless & computer networks,

Network analysis, planning, and design.

Recent Projects

•

Wireless Local Area Networks Integration for Mobile Networks Operators , 2005.

•

E-Tourism Promoter

– An Internet Assisted Location Tracker and Map Reader for

Tourists , 2005.

Industrial Experience

•

Senior Wireless Technical Advisor , Nortel Networks, Richardson, USA

(1995-2003).

Patents

•

“

CDMA Inter-Mobile Switching Center Soft Hand-Off ,

” with S. Sides, A. Jalali, J.

Boppana, S. Doctor, US Patent # 5,930,714 , 1999, US Patent # 6,173,183 , 2001.

Recent Publications

•

A. Mahmoud and M. Abu-Amara, “ Performance of Inter-Base Station Soft Handoff for

3G CDMA Networks ,

” Proceeding of the First International Conference on Modeling,

Simulation and Applied Optimization, Sharjah, U.A.E. February 2005.

•

M. Abu-Amara, “ Minimum Traffic Inter-BS SHO Boundary Selection Algorithm for

CDMA-Based Wireless Networks , ” Proceedings of the 2004 IEEE Radio and

Wireless Conference, Atlanta, Georgia, September 2004, pp. 51-53.

Dr. Wasim Raad, Assist. Professor

Research Interests

•

Embedded systems, Smart cards applications, Real time DSP systems

Recent Projects

•

Context aware energy management system

•

Design of a wireless safety system for smart kitchen

•

Designing and building a mobile Emergency warning system for patients under health care.

Recent Publications

•

M.W. Raad, J.M. Noras, M. Shafiq and A. Aksoy, ‘ Gamma-Ray Peak

Detection Algorithms Using Embedded DSP ’, ESS Conference,

October 2004, UK.

•

M.W. Raad, J.M. Noras and M. Deriche, ‘ Parameter Estimation and

Digital Peak Localization Algorithms For Gamma Ray

Spectroscopy ’, In the proceedings of the fourth International

Symposium on Communication systems, Networks and Digital

Signal Processing, University of Newcastle, UK,20-22 July 2004.

•

M.W.Raad and J.M. Noras, ‘ Moment Preserving parameter estimation and digital online peak localization algorithms for Gamma

Ray Spectroscopy ’, IEEE Nordic Signal Processing Symposium,

June 13-15, 2000, Kolmarden,Sweden.

Dr. Talal Alkharobi, Assist. Professor

Research Interests

•

Design automation, neural networks, fuzzy logic, information and network security .

Recent Projects

•

Secure reliable storage system, 2004-2005.

•

Design, Analysis, and FPGA prototyping of High-Performance

Arithmetic for Cryptographic Applications, 2005.

Recent Publications

•

Hand Writing recognition using Artificial neural network , ICANN96 –

Italy.

•

Secret Sharing using Artificial neural network , Ph.D. dissertation

2004, Texas A&M university - College Station – Texas – USA .