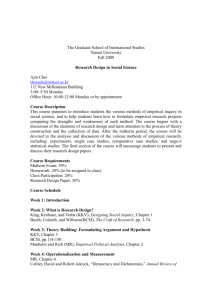

Yonsei University

advertisement

Chapter 6 External Device Yonsei University Contents • • • • • • • 6-2 External Devices I/O Modules Programmed I/O Interrupt-Driven I/O Direct Memory Access I/O Channel and Processors The External Interface:SCSI and FireWire Yonsei University Overview External Devices • Input / Output modules are the third critical element of the computer system (others are the CPU and the memory) • Why one does not connect peripherals directly to the system bus – Variety of peripherals with various methods of operation – Data transfer rate of peripherals is slow – Different data format and word lengths • I/O module major functions – Interface to the processor and memory via the system bus or central switch – Interface to the one or more peripheral devices by tailored data links 6-3 Yonsei University Generic Model of an I/O Module 6-4 External Devices Yonsei University Peripheral device External Devices • External device is referred to as a peripheral device • External Device – Human readable • VDT(video display terminal) – Machine readable • Magnetic disk, tape systems, sensor – Communication 6-5 Yonsei University External Device 6-6 External Devices Yonsei University Keyboard/Monitor External Devices • Most common means of computer/user interaction • Basic unit of exchange is the character • ASCII is most commonly used 6-7 Yonsei University America Standard Code 6-8 External Devices Yonsei University ASCII Control Characters 6-9 External Devices Yonsei University ASCII Control Characters 6-10 External Devices Yonsei University ASCII Control Characters 6-11 External Devices Yonsei University ASCII Control Characters 6-12 External Devices Yonsei University Disk Drive External Devices • Disk driver exchanges data, control, status signal with an I/O module plus the electronics for controlling the disk read/write mechanism • Fixed-head disk – Convert the magnetic patterns on the moving disk surface to bits in the devices buffer • Moving-head disk – Cause disk arm to move in and out across the disk’s surface 6-13 Yonsei University Module Function I/O Modules • Major funtion for an I/O module – – – – – 6-14 Control and timing Processor communication Device communication Data buffering Error detection Yonsei University Control and timing • Control step of the transfer data – Processor interrogates the I/O module – I/O module returns the device status – Transfer data by means of a command to the I/O module – I/O miodule obtains a unit of data – Data are transferred from the I/O module to the processor 6-15 Yonsei University Processor communication • Processor communication – Command decoding • I/O module accepts commands from processor – Data • Exchange data between processor and I/O – Status reporting • It is important to know status of I/O module • Common status signal : BUSY, READY – Address recognition • Each I/O device has an address • An I/O module must recognize one unique address for each peripheral it controls 6-16 Yonsei University I/O Device Data Rates 6-17 External Devices Yonsei University Device communication External Devices • Device communication involves commands, ststus information, and data 6-18 Yonsei University Data buffering External Devices • Data coming from main memory are sent to an I/O module in a rapid burst • Data are buffered in the I/O module and then sent to the peripheral device at it data rate • In opposite direction, data I/O module must be able to operate at both device and memory speeds. 6-19 Yonsei University Error detection External Devices • I/O module is responsible for error detection and for subsequently reporting errors to the processor 6-20 Yonsei University I/O Module Structure External Devices • Connect to the rest of the computer through a set of signal lines • I/O module function to allow the processor to view a wide range of devices in a simple-minded way • I/O channel – Quite primitive and requires detailed control – Commonly seen on the microcomputer • I/O controller – Used on mainframes 6-21 Yonsei University Block Diagram of an I/O Module 6-22 External Devices Yonsei University Three Techniques for I/O Operations Programmed I/O • Programmed I/O • Interrupt driven I/O • DMA No Interrupts Use of Interrupts I/O-to-memory transfer Programmed I/O through processor Interrupt-driven I/O Direct I/O-to-memory transfer Direct memory access (DMA) 6-23 Yonsei University Overview Programmed I/O • Processor execute program that give it direct control I/O operation • I/O module perform the requested action • Set the appropriate bits in the I/O status register • I/O module takes no further action to alter the processor • It does not interrupt the processor 6-24 Yonsei University I/O Commands Programmed I/O • Four type I/O commands – Control • Activate a peripheral and tell it what to do – Ex. Megnetic-tape rewind, forward… – Test • Test a various ststus conditions associated with an I/O module and its peripherals – Read • Obtain an item of data from the peripheral and place it in an internal buffer(Fig6.4 data register) – Write • Take an item of data(byte or word) from the data bus and transmit that data item to the peripherals 6-25 Yonsei University Tree Techniques for Input of a Block of Data Programmed I/O 6-26 Yonsei University I/O Instructions Programmed I/O • Instruction are easily mapped into I/O commands • Form of the instruction depends on the way external devices are • I/O devices is given a unique identifier or address 6-27 Yonsei University I/O Instructions Programmed I/O • Two modes of addressing – Memory mapped I/O • Single address space for memory locations and I/O devices • Same machine instruction to access both memory and I/O devices – Isolated I/O • Address space for I/O is isolated from memory • Need I/O or memory select lines • Special commands for I/O 6-28 Yonsei University Memory-Mapped and Isolated I/O 6-29 Programmed I/O Yonsei University Interrupt-Driven I/O Interrupt-Driven I/O • Problem of programmed I/O – Processor wait a long time for the I/O module of concern to be ready for either reception or transmission of data • Alternative – Processor issue an I/O command to a module and go on to do some other useful work – Interrupt the processor to request service when it is ready to exchange data with the processor – Execute data transfer and resume its former processing 6-30 Yonsei University Interrupt-Driven I/O Interrupt-Driven I/O • Interrupt I/O is more efficient than programmed I/O because it eliminate needless waiting • Interrupt I/O still have much processor time 6-31 Yonsei University Simple Interrupt Processing 6-32 Interrupt-Driven I/O Yonsei University Interrupt Processing • Interrupt-Driven I/O Sequence of hardware events 1. Device issues an interrupt signal to processor 2. Processor finish execution of execution of current instruction 3. Processor signals acknowledgment of interrupt 4. Processor push PSW and PC onto control stack 5. Processor loads new PC value based on interrupt 6. Save remainder of process state information 7. Process interrupt restore process state information 8. Restore process state information 9. Restore old PSW and PC 6-33 Yonsei University Design Issues Interrupt-Driven I/O • How does the processor determine which device issued the interrupt • If multiple interrupts have occurred, how does the processor decide which one to process? • Four device identification – – – – 6-34 Multiple interrupt lines Software poll Daysy chain(hardware poll, vectored) Bus arbitration(vectored) Yonsei University Changes in Memory & Register Interrupt-Driven I/O (a) Interrupt occurs after instruction at location N 6-35 Yonsei University Changes in Memory & Register Interrupt-Driven I/O (b) Return from interrupt 6-36 Yonsei University Multiple Interrupt lines Interrupt-Driven I/O • Most straightforward approach to the problem • Impractical to dedicate bus lines or processor pins to interrupt lines 6-37 Yonsei University Software Poll Interrupt-Driven I/O • On interrupt, processor branchs to an interrupt-service routine which it is to poll each I/O module to determine which module caused the interrupt • Poll is in the form of a separate command line(TESTI/O) • Each l/O module contain an addressable status register • Read status register of each IO module to identify the interrupting module • Disadvantage is time consuming 6-38 Yonsei University Daisy Chain Interrupt-Driven I/O • Hardware poll • Vectored interrupt – Vector • A word on the data lines • Address of the I/O module or unique identifier – Processor use vector as a pointer to the appropriate device routine – Avoid the need to execute a general interruptservice routine first 6-39 Yonsei University Bus Arbitration Interrupt-Driven I/O • I/O module must first gain control of the bus • One module can raise the line at a time • On interrupt, it respond on the interrupt ack line • Requesting module place its vector on the data lines 6-40 Yonsei University Intel 82C59A Interrupt Controller Interrupt-Driven I/O • Intel 80396 provide a single interrupt request(INTR) and single ack(INTA) • External interrupt arbiter, 82C59A • 82C59A manage interrupt • Interrupt mode – Fully nested • Interrupt request are ordered in priority from 0(IR0) through 7(IR7) – Rotating • Lowest priority in the group – Special mask • Processor inhibit interrupt from certain devices 6-41 Yonsei University 82C59A Interrupt Controller 6-42 Interrupt-Driven I/O Yonsei University Intel 82C55A Interrupt-Driven I/O • General-purpose I/O module designed for use with the Intel 80386 processor • Next page Fig 6.10 6-43 Yonsei University Intel 82C55A 6-44 Interrupt-Driven I/O Yonsei University Keyboard/Display Interface 6-45 Interrupt-Driven I/O Yonsei University Drawbacks of I/O Direct memory access • Processor intervene in data transfer between memory and an I/O module • Inherent drawback – I/O transfer rate is limited – Processor is tied up in managing an I/O transfer • More efficient technique is required: – Direct memory access(DMA) 6-46 Yonsei University DMA Block Diagram 6-47 Direct memory access Yonsei University DMA Function Direct memory access • DMA involves an additional module on system bus • DMA module take over control of the system from processor • Cycle stealing – DMA module in effect steals a bus cycle 6-48 Yonsei University DMA Function Direct memory access • Issue a command to the DMA module, by sending to the DMA module the following information – Whether a read or write is requested, using the read or write control line between the processor and the DMA module – Address of I/O device involved, communicated on the data lines – Starting location in memory to read from or write to, communicated on the data lines and stored by the DMA module in its address register – The number of words to be read or written, again communicated via the data lines and stored in the data count register 6-49 Yonsei University DMA Function Direct memory access • DMA module transfer the entire block of data, – One word at a time – Directly to or from memory – Without going through the processor • When transfer complete, DMA module sends an interrupts signal to processor • Processor is involved only at the beginning and end of the transfer 6-50 Yonsei University DMA & Interrupt Break point 6-51 Direct memory access Yonsei University Alternative DMA Configuration Direct memory access • Single-Bus, Detached DMA 6-52 Yonsei University Alternative DMA Configuration Direct memory access • Single-Bus, Integrated DMA-I/O 6-53 Yonsei University Alternative DMA Configuration Direct memory access • I/O Bus 6-54 Yonsei University The evolution of the I/O Functions I/O Channels & Processors • Evolutionary step 1. CPU directly controls a peripheral device 2. Controller or I/O module is added 3. Same configurations is used, but now interrupts are employed 4. I/O module is given direct access to memory via DMA 5. I/O module is enhanced to become a processor in its own right, with a specialized instruction set tailored for I/O (I/O channel) 6. I/O module has a local memory of its own and is a computer in its own right (I/O processor) 6-55 Yonsei University The evolution of the I/O Functions I/O Channels & Processors • More and more of the I/O function is performed without CPU involvement 6-56 Yonsei University Characteristics of I/O Channels I/O Channels & Processors • I/O channel an extension of DMA concept • I/O channel has the ability to execute I/O instruction • CPU does not execute I/O instruction • Two type of I/O channel – Selector channel • Control multiple high-speed devices • Transfer of data with one of those devices – Multiplexor channel • Handle I/O with multiple devices at the same time 6-57 Yonsei University I/O Channel Architecture I/O Channels & Processors (a)Selector 6-58 Yonsei University I/O Channel Architecture I/O Channels & Processors (b)Multiplexor 6-59 Yonsei University Type of Interface External Interface: SCSI and FireWire • Parallel interface – Multiple line connecting the I/O module and the peripheral – Multiple bits transferred simultaneously – Used for higher speed peripherals(tape,disk) • Serial interface – One line used to transmit data – Bits must be transmitted one at a time – Printer, terminals 6-60 Yonsei University Dialogue for a Write Operation External Interface: SCSI and FireWire 1. I/O module send a control signal 2. Peripheral acknowledges the request 3. I/O module transfer data 4. Peripheral acknowledges receipt of the data (read operation proceeds similary) 6-61 Yonsei University Parallel and Serial I/O External Interface: SCSI and FireWire • 6-62 Yonsei University Point-to-Point & Multipoint External Interface: SCSI and FireWire • Point-to-point – Dedicated line between I/O module and external device – On small system(PC), include keyboard, printer, external modem • Multipoint – Used to support external mass storage devices(disk, type) and multimedia devices(CDROM,video) 6-63 Yonsei University Small Computer Interface External Interface: SCSI and FireWire • SCSI – Popularized in the Macintosh in 1984 – Now widely used on Mac, Windows/Intel system, workstation • SCSI Version – SCSI-1 : • 8 data lines and operate at a clock speed of 5MHz of a data rate of 5 Mbytes/s – SCSI-2 : • Optional expansion of the data lines to 16-32 and increase of the clock speed to 10 MHz • Maximum data rate of 20 or 40 Mbytes/s 6-64 Yonsei University Signals and Phases External Interface: SCSI and FireWire • Bus Free – No device is using the bus • Arbitration – Enable one device to gain control of the bus • Selection – Enable an initiator to select a target to perform a funcion • Reselection – Enable a target to reconnect to an initiator to resume an operation • Command – Enable target to request the command information 6-65 Yonsei University Signals and Phases External Interface: SCSI and FireWire • Data – Enable the target to request the transfer of data • Status – Enable the target to request that status information be sent from the target to the initiator • Message – Enable the target to request the transfer of one or more messages 6-66 Yonsei University SCSI Bus Phases 6-67 External Interface: SCSI and FireWire Yonsei University SCSI Control Lines External Interface: SCSI and FireWire • BSY – Set to indicate the bus is busy • SEL – Select a target to perform a command • C/D – Indicate whether data on the data bus is Control or Data information • I/O – Control the direction of data movement • MSG – Indicate to the initiator that the information being trasferred is a message 6-68 Yonsei University SCSI Control Lines External Interface: SCSI and FireWire • REQ – Request a data information transfer • ACK – Acknowkedge a REQ from traget • ATN – Inform the target that it has a message available for transfer • RST – Used to reset the bus 6-69 Yonsei University SCSI Bus Signals External Interface: SCSI and FireWire • 6-70 Yonsei University SCSI Timing Diagram 6-71 External Interface: SCSI and FireWire Yonsei University Messages • • • • External Interface: SCSI and FireWire Command complete Disconnect Initiator Detected Error Abort – Sent from initiator to the target to clear the present operation • Synchronous Data Transfer – Exchanged between initiator and target to establish synchronous data transfer 6-72 Yonsei University Commands External Interface: SCSI and FireWire • Steps for execution of command – Target acquires and decides command information – Data is transferred to or from the target – Target generates and returns status information • Fields of CDB – – – – – – – 6-73 Operation code Logical unit number Logical block address Transfer length Parameter list length Allocation length Control Yonsei University SCSI Command Block Format 6-74 External Interface: SCSI and FireWire Yonsei University Commands External Interface: SCSI and FireWire • Mandatory – – – – 6-75 Inquiry Request Sense Send Diagnostic Test unit ready Yonsei University Fire Wire Serial Bus External Interface: SCSI and FireWire • FireWire – IEEE standard 1394, for a high-performance serial bus • Advantages – High speed – Low cost – Easy to implement 6-76 Yonsei University Fire Wire Serial Bus External Interface: SCSI and FireWire • Use serial transmission (bit at a time) rather than parallel • Computers are getting physically smaller • Provide a single I/O interface with a simple connector • User can reach behind the machine and plug it in without looking 6-77 Yonsei University FireWire Configurations External Interface: SCSI and FireWire • Use a daisy chain • Provide for what is known as hot plugging • With SCSI, both ends of the bus must have terminators and each device must be assigned a unique address as part of the configuration • No terminators 6-78 Yonsei University FireWire Configurations External Interface: SCSI and FireWire • System automatically perform a configuration function to assign addresses • Tree structured configuration is possible • Three layer of the stack – Physical layer – Link layer – Transaction layer 6-79 Yonsei University Comparison of SCSI&FireWire 6-80 External Interface: SCSI and FireWire Yonsei University Physical layer External Interface: SCSI and FireWire • Several alternative transmission media and their connectors • Tree structured arrangement of the node 6-81 Yonsei University FireWire Protocol Stack 6-82 External Interface: SCSI and FireWire Yonsei University Link Layer External Interface: SCSI and FireWire • Tow type of transmission – Asynchronous – Isochronous • Subaction’s five time period – – – – – 6-83 Arbitration sequence Packet transmission Acknowledgement gap Acknowledgment Subaction gap Yonsei University FireWire Subactions 6-84 External Interface: SCSI and FireWire Yonsei University