Validation - ArtistDesign NoE

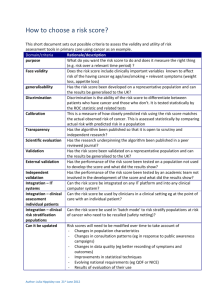

advertisement